Siemens EDA/シーメンス EDA

Questa Advanced Simulation

Questa検証プラットフォームのコアとなるシミュレーションおよびデバッグエンジン

Questa Advanced Simulatorは、Verilog、System Verilog、VHDL、SystemC、SVA、UPFおよびUVMを最も完全なネイティブサポートを実現するために、高い性能を誇り大規模設計に対応したシミュレーションエンジンに、高度なデバッグや機能カバレッジを組み合わせています。複雑なFPGAやSoC設計の検証におけるリスクを低減するための包括的かつ高度な検証プラットフォームです。

RTLやゲートレベル設計に対して、TLM(トランザクション・レベル・モデリング)の抽象度のテストベンチを適用できます。アサーションベース検証(ABV)とUVM-Universal Verification Methodologyを組み合わせることで、テストを自動化し、検証の生産性、再利用性を向上させることができます。

特徴

高い性能と大規模対応

Questa Advanced Simulatorは、Verilog/SystemVerilogおよびVHDLに対して強力なグローバルオプティマイズを適用し、業界最高レベルの性能と大規模対応を実現しています。特にSystemVerilogとVHDLが混在したRTL設計に対する最適化では、最大で10倍ものシミュレーション性能を引き出します。また次のシミュレーションまでの時間を最短化する、すなわち高速スループットを実現するために、ブロックごとの最適化時に、デバッグに最適な可視性を保持し、ライブラリを効率よく管理するユニークな機能により、大規模なリグレッションスイートでは、スループットを最大で3倍も改善します。

さらに長時間のシミュレーションを要する大規模設計に対応するために、マルチコアのアーキテクチャもサポートします。プロセッサの周波数改善が鈍化する傾向にあるなかで、複数のコアに手動または自動で設計をパーティショニングし、並列実行によって高い性能を引き出すことができます。

アサーションベース検証

Questa AdvancedSimulationでは標準言語仕様によるアサーションベース検証手法を提供しており、SVA–SystemVerilog Assertions、PSL–Property Specification Language、またはその両方混在を選択できます。またアサーションベース検証手法の採用を容易化すべくQVL–Questa Verification Libraryを提供しています。QVLはSystemVerilogによるチェッカ/モニターのライブラリで、幅広い業界標準プロトコルをサポートしており、シミュレーション、エミュレーション、フォーマル検証でも使用できるよう最適化されています。

テストの自動化

Questa Advanced Simulatorは、業界でもっとも包括的なテストベンチオートメーションのソリューションを提供します。Questa inFactとの連携によってインテリジェントなテスト生成を自動化し、記述された制約によって、シナリオの入力空間に対して複雑なスティミュラスを自動生成します。Questaは、スティミュラス生成と機能カバレッジを組み合わせ、自動生成されたスティミュラスによってどの機能が実行されたかを特定します。検証エンジニアは機能カバレッジのメトリクスをフィードバックしながら制約を調整することで、カバレッジの未達部分に対して集中的にランダムテストを追加していくことができます。この自動化手法では、手作業で数多くのディレクテッドテストを作成する場合に比べ、生産性が飛躍的に向上します。

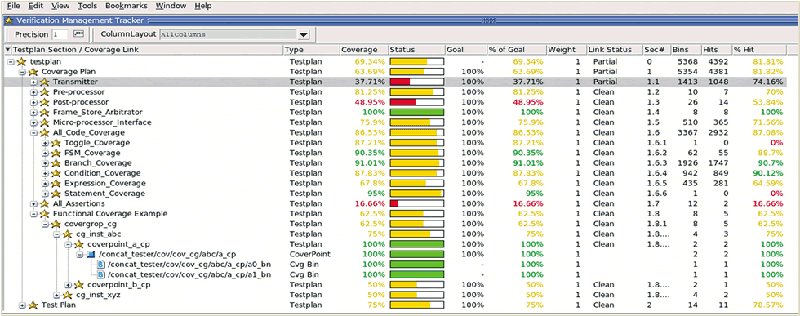

Questaでは、コードカバレッジ、アサーション・カバレッジ、フォーマルカバレッジ、機能カバレッジの情報をすべてUCDB-Unified Coverage DataBaseに集約し、これらのデータをテストベンチ内でリアルタイムに参照したり、あるいはシミュレーション後にQuesta Verification Managementで処理することができます。

Questa Verification Management

制約付きランダムテストでスティミュラスを自動生成しメトリクスドリブン検証を実施すると、検証プロセスで生成されるデータ量は劇的に増加してしまいます。Questa Verification Managementは、すべてのカバレッジおよび検証に関わるデータを解析し、検証テストスイートの最新の進捗状況を把握することができ、検証プロセスの効率と効果を高めるための手がかりを得ることができます。

統合された多言語デバッグ

Questaデバッグ環境は、すべての標準言語を完全にサポートしており、あらゆる言語および抽象度において一貫したGUIを利用できます。Questaでは、設計および検証環境における主要なオブジェクトが自動的に認識され、これらオブジェクトを直観的な方法で表示およびデバッグできます。たとえば、ステートマシン(FSM)が存在すると判断された場合は、FSMデバッグウィンドウ内でFSMの現在のステートおよび時系列でのステート遷移が自然な方法で視覚化されます。

OVMおよびUVMクラスライブラリで構成された検証環境は、全体的なシミュレーション階層の一部として認識されます。検知されたエラーからバグの原因までの因果関係を追跡する作業にも多くの時間と労力が必要ですが、こうしたプロセスもQuestaで自動化できます。グラフィカルな回路図ビューまたはソースベースのデータフローによって、ソースとシンク(ドライバとリーダ)の関係を辿り、バグの原因を容易に特定することが可能です。

パワーアウェア検証

消費電力の管理は、多くのアプリケーションで極めて重要です。しかし、パワーマネジメント技術には、設計や検証の面で特有の課題があります。QuestaのパワーアウェアシミュレーションとAccelleraのUPF(Unified Power Format)規格を組み合わせると、設計サイクルの早い段階でローパワーシリコンの動作を正確にモデリングできるため、ローパワーのシリコン設計を実装する際のリスクを軽減できます。

「アサーションベース設計 立ち上げ支援サービス」をご利用ください

Wilson Research Groupが実施した機能検証の市場調査によれば、アサーションを使用する大多数はSystemVerilog Assertions(SVA)を使用しています。SVAは2005年にIEEE標準となっています。新たな手法が登場したときに、それを開発フローに導入するには、言語の習得に始まり、その効果を評価しては改善するなど、多くの労力を要します。

PALTEKではこの労力を低減し、誰もがアサーションを使い始められるようにするための支援策として、「アサーションベース設計 立ち上げ支援サービス」を提供しています。

シーメンス EDAのことなら

PALTEKにご相談ください!

- AMD

- AudioCodes

- Bellnix

- congatec

- Diodes

- EFCO

- GSI Technology

- iBASE Technology

- InnoPhase IoT

- Macom Technology Solutions

- MaxLinear

- MEAN WELL

- Microchip Technology

- Micron Technology

- Monolithic Power Systems (MPS)

- Nexperia

- PHABRIX

- Plunify

- Robustel

- Siemens EDA(旧Mentor Graphics)

- SiTime

- TELEDYNE FLIR

- Toppan Technical Design Center