株式会社PALTEK > 半導体事業 > 取扱メーカー > Siemens EDA/シーメンス EDA > Questa – 機能検証プラットフォーム > Questa Connectivity Check

Siemens EDA/シーメンス EDA

Questa Connectivity Check

IP/SoCにおける動的/静的な接続性を検証

Questa Connectivity Checkは完全自動化された動的/静的な接続チェックのためのフォーマル検証アプリです。SoC設計は小さな設計規模であってもBIST、低電力用アイソレーション回路、I/O多重化技術などにより、接続性はいっそう複雑化しています。個々のIPブロックが正しく設計されていても、その接続に誤りがあればSoCとしては正しく動作しません。接続が正しく行われていることを検証するには、従来はテストスティミュラスを作成してシミュレーションを行う必要がありましたが、組合せ数が膨大になり、かつ複雑になるに連れ、接続チェックは1つの大きな検証項目となっています。

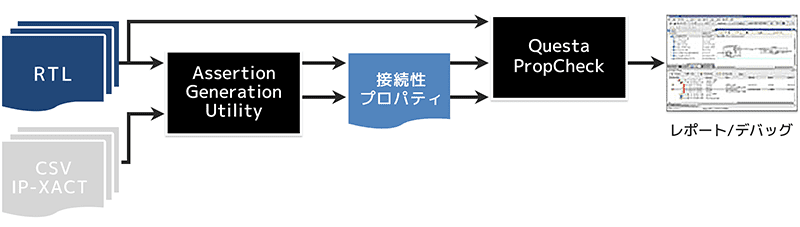

Questa Connectivity Checkは QuestaFormalエンジンをベースに、接続チェックに特化したアプリです。RTL設計に加えて、設計仕様所の一部として存在する接続定義ファイルをCSV、IP-XACTフォーマットで読込み、接続性を検証するためのアサーションを自動生成します。フォーマルエンジンはRTLが取り得るすべてのステートに対して自動生成されたアサーションに違反しないことを数学的に証明します。従来なら週単位で行われていた検証も、時間単位で網羅的に行うことが可能です。

概要

- SoCやサブシステムにおけるオンチップバス、ブロック間、制御信号、クロック系、リセット系のすべての接続を検証

- 接続仕様を分かりやすい表形式で表現、すべての動作モードを仕様にもとづいて完全にチェック静的/動的な接続形態を数時間で完全検証

- セットアップが容易で、かつフォーマル検証やアサーションの知識が必要ないため、誰でもが使用可能

- 仕様と設計との間に発生するすべての不一致は、反証波形によって問題となる接続箇所と時間を特定される

シーメンス EDAのことなら

PALTEKにご相談ください!

- AMD

- AudioCodes

- Bellnix

- congatec

- Diodes

- EFCO

- GSI Technology

- iBASE Technology

- InnoPhase IoT

- Macom Technology Solutions

- MaxLinear

- MEAN WELL

- Microchip Technology

- Micron Technology

- Monolithic Power Systems (MPS)

- Nexperia

- PHABRIX

- Plunify

- Robustel

- Siemens EDA(旧Mentor Graphics)

- SiTime

- TELEDYNE FLIR

- Toppan Technical Design Center