【FPGAテストベンチ/検証ノウハウ】テストベンチによるクロック信号/リセット信号の生成(VHDL編)

第2回目は、一度作成しておくと汎用的に再利用が可能で便利なテストベンチでクロック信号やリセット信号を生成する方法のVHDL編を紹介します。

テストベンチによるクロック信号やリセット信号の生成は、一度作れば再利用が可能でとても便利です。

【FPGAテストベンチ/検証ノウハウ】テストベンチによるクロック信号/リセット信号の生成(Verilog編) についてはこちらから確認してください。

では、始めましょう。

このブログは「FPGA設計ブログ一覧」の

2. シミュレーションのひとつです。

目次

クロックの生成

VHDLでは残念ながらVerilogのように周波数を設定することができず、あらかじめ周期を求めておく必要があります。

156.25MHzのクロックを生成するサンプルを下記に示します。

library ieee ;

library std ;

use ieee.std_logic_1164.all ;

use ieee.std_logic_unsigned.all ;

entity tb_clk_vhdl is

port(

CLK1 : out std_logic

) ;

end tb_clk_vhdl ;

architecture tb_clk_vhdl of tb_clk_vhdl is

signal ck1 : std_logic := '0' ;

-- Clock Cycle

constant CLK1_CYCLE/2 : time := 6400 ps; -- 156.25MHz

-- Clock Generate

begin

ck1 <= not ck1 after CLK1_CYCLE ;

CLK1 <= ck1;

end tb_clk_vhdl ;library宣言およびuse宣言については割愛します。

constantにて156.25MHzの周期(6.4ns = 6400ps)を設定しています。

クロックはこの周期の半分3200ps単位で信号がトグルすることにより、156.25MHzのクロックを求めることができます。

こちらも同じ記述を追加することで、1つのモジュールから複数のクロックを出力することも可能です。またここでは内部パラメータのconstantを使用していますが、generic宣言により上位から周期を与えることでより汎用的に使用することも可能です。

リセットの生成

次はリセットの生成についてです。

下記にリセット信号を設定時間にてトグルするサンプルを示します。

library ieee ;

library std ;

use ieee.std_logic_1164.all ;

use ieee.std_logic_unsigned.all ;

use ieee.std_logic_arith.all ;

entity tb_rst_vhdl is

port(

RST1 : out std_logic

) ;

end tb_rst_vhdl ;

architecture tb_rst_vhdl of tb_rst_vhdl is

signal rt1_1 : std_logic ;

signal rt1_2 : std_logic ;

signal rt1_3 : std_logic ;

-- Reset Time Set (ns)

constant RST_TIM1 : time := 100 ns;

constant RST_TIM2 : time := 50 ns;

constant RST_TIM3 : time := 100 ns;

begin

rt1_1 <= '1' , '0' after RST_TIM1;

rt1_2 <= rt1_1 , '1' after RST_TIM2;

rt1_3 <= rt1_2 , '0' after RST_TIM3;

RST1 <= rt1_3;

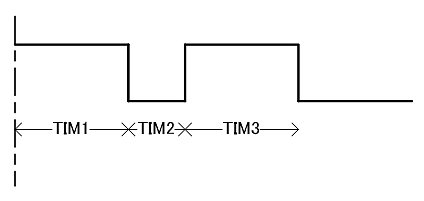

end tb_rst_vhdl ;constantにて信号をトグルさせたい時間を順番にns単位で設定しています。

ここではTIM1~3の3つのタイミングにて信号をトグルする設定としています。

こちらもVerilog編と同様にbegin以降で設定した時間により信号をトグルしています。

ここでは初期状態はHighとなっており、TIM1後にLow、さらにTIM2後にHigh、TIM3後に再度Lowとなります。

リセット生成もクロック生成と同様に複数個することや、generic宣言にて上位から時間設定を行うことでより便利に使うことができます。

以上でテストベンチによるクロック信号/リセット信号の生成の説明(VHDL編)を終わります。

このブログは「FPGA設計ブログ一覧」の

2. シミュレーションのひとつです。

最後までお付き合いいただきありがとうございました。

ModelSim/Questa エディション比較表はこちらをご覧ください。