EdgeCortix株式会社と提携、エッジAIハードウェア・アクセラレーション・ソリューションを市場に投入

2021 年 2 ⽉ 5 ⽇

PALTEK、EdgeCortix株式会社と提携して

エッジAIハードウェア・アクセラレーション・ソリューションを市場に投入

株式会社PALTEK(本社:横浜市港北区、代表取締役社⻑:⽮吹尚秀、証券コード:7587、以下PALTEK)は、エッジデバイス用の人工知能推論プロセッサ開発を手掛けるEdgeCortix株式会社(本社:東京都品川区、代表取締役:サキャシンガ・ダスグプタ、読み方:エッジコーテックス、以下EdgeCortix)と提携して、エッジAI導入における課題解決を実現、またFPGAを活用したことのないソフトウェア製品をソリューションとして販売している会社やシステムインテグレータに対しても、エッジAIに対する最適なソリューションを提供します。

EdgeCortixは、エッジデバイス上の深層学習推論プロセッサ用の低遅延でエネルギー効率の高いハードウェアIP(知的財産)とシステムソフトウェアを提供する会社です。このパートナーシップにより、PALTEKはEdgeCortixのハードウェアIPとMERA™コンパイラをAMD ザイリンクス社のアクセラレータカード「Alveo™ U50 データセンター アクセラレータ カード」※1に実装・提供することで、ADAS(高度なドライバ支援システム)、自動運転、ロボット、スマートシティ、ドローン、インダストリー4.0などにおける消費電力の削減が可能となります。

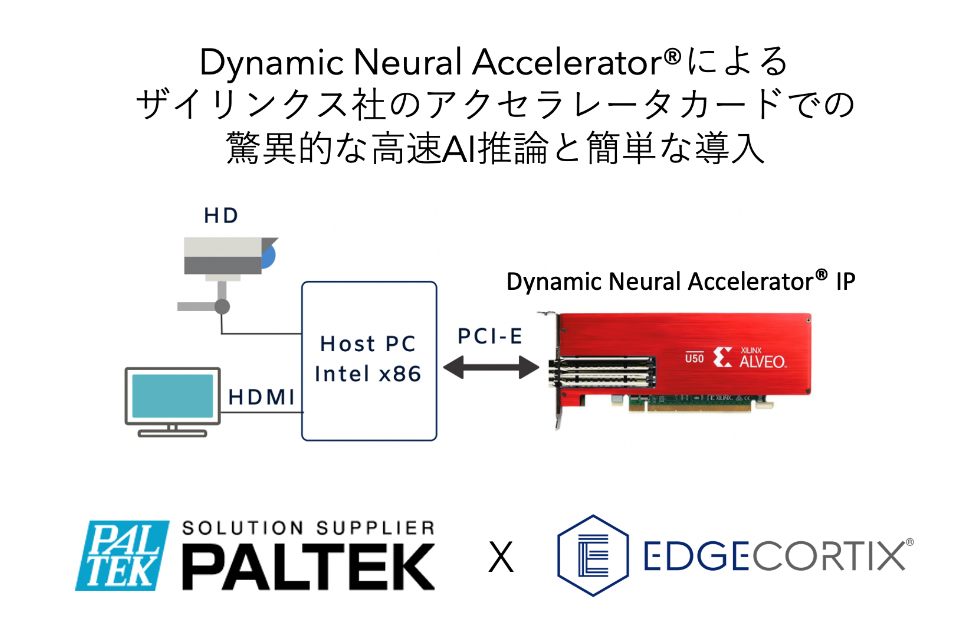

EdgeCortix IPコアを使用したフルHD解像度の推論をAMD ザイリンクス社のアクセラレータカード

Alveo™ U50 / U50LV上で実行するためのセットアップ例

今回の協業の背景・概要

近年、AI技術の要素技術であるディープラーニングにより、画像処理や音声処理など、いくつもの分野で劇的な精度向上が実現されてきましたが、現在のサービスはクラウド上のGPUを使って処理することが一般的で、推論時には通信量やネットワーク負荷、レイテンシの問題から、クラウドで効率的に処理できない活用事例が多数存在し、エッジデバイスでの推論処理の実行は重要な技術的課題となっています。

PALTEKが販売代理店契約を締結したEdgeCortixは、2019年に設立され(日本とシンガポール)、エッジデバイス向けに低遅延人工知能推論プロセッサ用のハードウェアIPとソフトウェアを提供する会社です。

EdgeCortixのハードウェアIPであるDynamic Neural Accelerator®※2は、PALTEKが提供するAMD ザイリンクス社のアクセラレータカード Alveo™ U50に搭載でき、応答速度やネットワーク環境などの厳しい制限にも対応できます。「ロボット、ドローン、インダストリー4.0」などの分野では、複雑かつ大容量の演算を高速に処理でき、省スペース化、低消費電力化にも優れているFPGAがエッジAI領域ではCPUやGPUよりも適しています。

こうした背景の下、エッジデバイスにAI機能を搭載できるEdgeCortixの高度な技術力と、PALTEKの量産導入までの提案・販売力および技術サポートを組み合わせることにより、エッジAI導入における現場の課題を解決します。また、FPGAを活用したことのないソフトウェア製品をソリューションとして販売している会社やシステムインテグレータに対しても、エッジAIに対する最適なソリューションを提供することができると考え、このたびの販売代理店契約締結に至りました。

主な取り組み内容・協業施策

本販売代理店契約締結では、両社の強みを組み合わせ、FPGAを活用したエッジAIソリューションの開発・量産導入を加速し、お客様の課題解決に向けた最適なソリューションを両社で提案・実行してまいります。

● EdgeCortix株式会社 代表取締役 サキャシンガ・ダスグプタは、次のように述べています。

「PALTEKとパートナーシップを結ぶことを大変嬉しく思います。FPGAを含むエッジAIハードウェアアクセラレーションビジネスが大幅に成長すると確信します。PALTEKとの協力によって、独自のテクノロジーを活用した完全な統合ソリューションが、エッジAI製品の実用化と全体的なカスタマーエクスペリエンスを向上できると強く感じます。PALTEKは1982年の創業以来、FPGAを中心とした半導体製品の販売・技術サポートの豊富な経験を持ち、お客様の製品開発のパートナーとして仕様検討から試作開発、量産までサポートしています。当社はこの経験に支えられて、FPGAを使用したエッジデバイスおよびデータセンターでの非常に高速な推論のためのAIプロセッサIPおよびコンパイラテクノロジーが提供できるようになりました。」

● 株式会社PALTEK 代表取締役社長 矢吹尚秀は次のように述べています。

「現在、様々なAIサービスが市場に投入されておりますが、その多くはクラウド上のCPUやGPUで処理されています。我々がターゲットとしているロボット、スマートシティ、インダストリー4.0などの分野では低遅延や低消費電力および長期供給性を求めるお客様が多いため、FPGAによるエッジAIのニーズが高まっています。EdgeCortixはエッジAIにフォーカスし、より低遅延、低消費電力に特化したソリューションを提供しており、我々が取り扱うAMD ザイリンクス社製品と一緒に提案することで更なる相乗効果が得られることを大変期待しております。」

EdgeCortixが提供する Dynamic Neural Accelerator® IP DNA-F200について

DNA-F200は、FPGA上のディープニューラルネットワーク(DNN)推論アプリケーション向けのEdgeCortix Dynamic Neural Accelerator®︎ データフローアーキテクチャベースのIPファミリーの新製品です。これは、HBMをサポートするAMD ザイリンクス社の Alveo™ U50 / U50LV適応型アクセラレータカード用に設計しています。DNA-F200(300MHzで3.7 INT8 TOP/s)およびその前身のDNA-F100(275MHzで2.3 INT8 TOP/s)は、高性能な畳み込みニューラルネットワーク(CNN)推論用のIPで、超低遅延でエネルギー効率が良く、高スループットなストリーミングデータ用のワークロードに最適です。非常に高速なエッジAIアプリケーション向けに特別に設計しています。DNA-F200 / F100は、INT8ビットバッチサイズ1の推論用に高度に最適化されたインストラクションセットで実行され、ResNet、YOLO、SSD、MobileNet、FPN、MonoDepthなどのすべての主流な畳み込みニューラルネットワークをサポートしています。また、Vitis※3プラットフォームを備えたすべてのAMD ザイリンクス社製ボードまたはカスタムボードもサポートしています。

EdgeCortixは、独自のMERA™コンパイラとともにDNA-F200ビットストリームを提供します。これにより、 PyTorchやTensorFlow Liteなどの最も一般的なフレームワークで設計されたディープニューラルネットワークをFPGAに最小限の努力でデプロイすることができます。オープンソースの機械学習コンパイラであるApache TVM※4上で開発されたMERA™を使用すると、機械学習エンジニアはCPUまたはGPU向けに設計されたネットワークをINT8ビット量子化することでAMD ザイリンクス社のAlveo™に実装されたDNA IP上で最適に実行できます。コンパイラは、ニューラルネットワークのどの部分をアクセラレータ上で実行できるかを自動的に識別し、その他の演算子をホストプロセッサ上で実行するように判断します。 MERA™コンパイラには、シミュレータとインタプリタも組み込まれています。コンパイル後、お客様はこれらのツールを使用して、ハードウェアでテストせずにサイクル精度のパフォーマンスシミュレーションを実行したり、INT8ビットの量子化がネットワークの精度に与える影響を定量化したりできます。

DNA-F200とMERAディープラーニングコンパイラの詳細は https://www.edgecortix.com/をご覧ください。専門用語説明

※1 Alveo™ U50 データセンター アクセラレータ カードディープニューラルネットワーク推論などの高速処理化に優れた性能を発揮するAMD ザイリンクス社のアクセラレータカード。

詳細は、 https://japan.xilinx.com/products/boards-and-kits/alveo/u50.html をご確認ください。

EdgeCortixが提供するIPで、ハードウェアアーキテクチャと高性能DNNモデルを組み合わせ、スループット、遅延、電力、サイズなどのメトリックの組み合わせに対して設定された目標を達成し、設計と最適化を同時に行うIP。

※3 Vitis 統合ソフトウェア プラットフォームAMD ザイリンクス FPGA、SoC、Versal ACAP でエンベデット ソフトウェアおよびアクセラレーション アプリケーションを開発するための環境です。

詳細は、 https://japan.xilinx.com/products/design-tools/vitis.html をご確認ください。

オープンソースでエンドツーエンドのCPU、GPU、アクセラレータ向け機械学習コンパイラフレームワークです。

詳細は、 https://tvm.apache.org/ をご確認ください。

※AMD ザイリンクスの名称および、その他本プレスリリースに記載のブランド名は米国およびその他各国のAMD ザイリンクスの登録商標または商標です。その他すべての名称は、それぞれの所有者に帰属します。

※Dynamic Neural Accelerator® および MERA™ は、EdgeCortix株式会社の登録商標です。

EdgeCortix株式会社について

EdgeCortix株式会社は、「低遅延、低コスト、エネルギー効率の高いディープニューラルネットワーク推論のために、クラウドレベルのパフォーマンスを組み込みエッジにもたらす」という企業使命を持って2019年に設立しました。

ハードウェアとソフトウェアを統合するコデザイン手法によって設計された独自の人工知能プロセッサ技術が強みです。EdgeCortixは、これまでに日本、シンガポール、アメリカの投資家から5億2500万円の資金調達に成功しました。電子製造業界の数社との既存のパートナーシップによる実績もあります。

AIハードウェアIPの作成にソフトウェア中心のアプローチを採用し、Dynamic Neural Accelerator® IPコアとMERA™コンパイラは、カスタムASICやFPGAに簡単にデプロイし動作するように設計されています。

EdgeCortixに関する詳細は、 https://www.edgecortix.com/ をご覧ください。

株式会社 PALTEK について

PALTEKは、1982年の創業以来、日本のエレクトロニクスメーカーに対して国内外の半導体製品の販売のほか、ハードウェアやソフトウェア等の設計受託サービスも提供し、お客様の製品開発のパートナーとして仕様検討から試作開発、量産までサポートしています。PALTEKは、「多様な存在との共生」という企業理念に基づき、お客様にとって最適なソリューションを提供することで、お客様の発展に貢献してまいります。

PALTEK に関する詳細は、https://www.paltek.co.jp をご覧ください。

■ニュースリリースに関するお問い合わせ

| 株式会社 PALTEK | |

|---|---|

| 担当者 | 広報担当 柴崎、寺田 |

| メールアドレス | pr@paltek.co.jp |

| 所在地 | 神奈川県横浜市港北区新横浜 2-3-12 新横浜スクエアビル 6F |

| 電話 | 045-477-2016 |

■本件に関するお問い合わせ

| 株式会社 PALTEK | |

|---|---|

| 担当者 | FPGAソリューション事業部 |

| メールアドレス | info_pal@paltek.co.jp |

| 所在地 | 神奈川県横浜市港北区新横浜 2-3-12 新横浜スクエアビル 6F |

| 電話 | 045-477-2002 |

■製品サービスに関するお問合わせ

| EdgeCortix株式会社 | |

|---|---|

| 担当者 | AIハードウェアアクセラレータチーム |

| メールアドレス | info@edgecortix.com |

| 所在地 | 東京都品川区西五反田3-15-6 |

| 電話 | 03-6417-9661 |