MPSoC-DDR4間のBGA接続テスト①FPGA実装編

みなさん、こんにちは。

本ブログはDDR4の接続テストモードを利用し、DDR4とFPGA間の接続テスト方法を紹介したいと思います。

なお、本篇で使用したEXAMPLEデザインはダウンロードできるよう準備していますので、

気になる方はダウンロードしていただければと思います。あわせてご確認ください。

それでは始めましょう。

このブログは「FPGA設計ブログ一覧」の

6. 実機評価のひとつです。

目次

概要

通常FPGAやDDR間のBGA実装不良や、基板不良などを判断する場合、JTAGバウンダリスキャンツールを利用すればできますが、専用ソフトが必要です。

今回専用ソフトを使わず、DDR4の接続テストモードを利用し、DDR4とFPGA間の接続テスト方法を紹介します。

背景

JEDEC®DDR4仕様で定義されたDDR4接続テスト(CT)モードは、DDR4デバイスのピンは入力セットと出力セットに分割され、入力ピンに異なる信号を送信し、出力ピンをチェックすることにより、短絡または開回路があるかどうかを確認できます。

方法

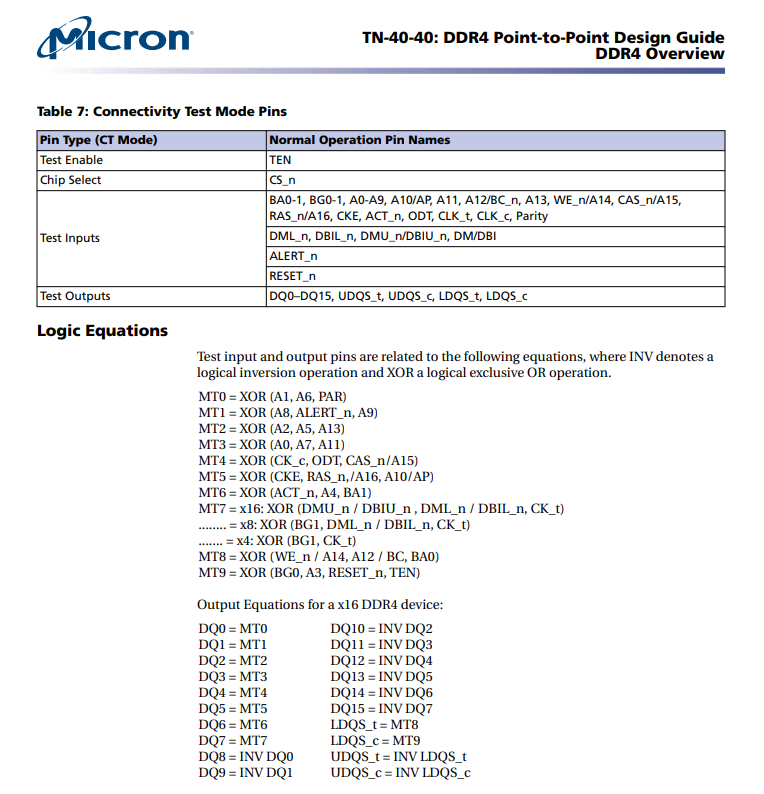

Micron社DDR4 Point-to-Point Design Guide CTモードの論理

出典: Micron TN-40-40: DDR4 Point-to-Point Design Guide (P10)

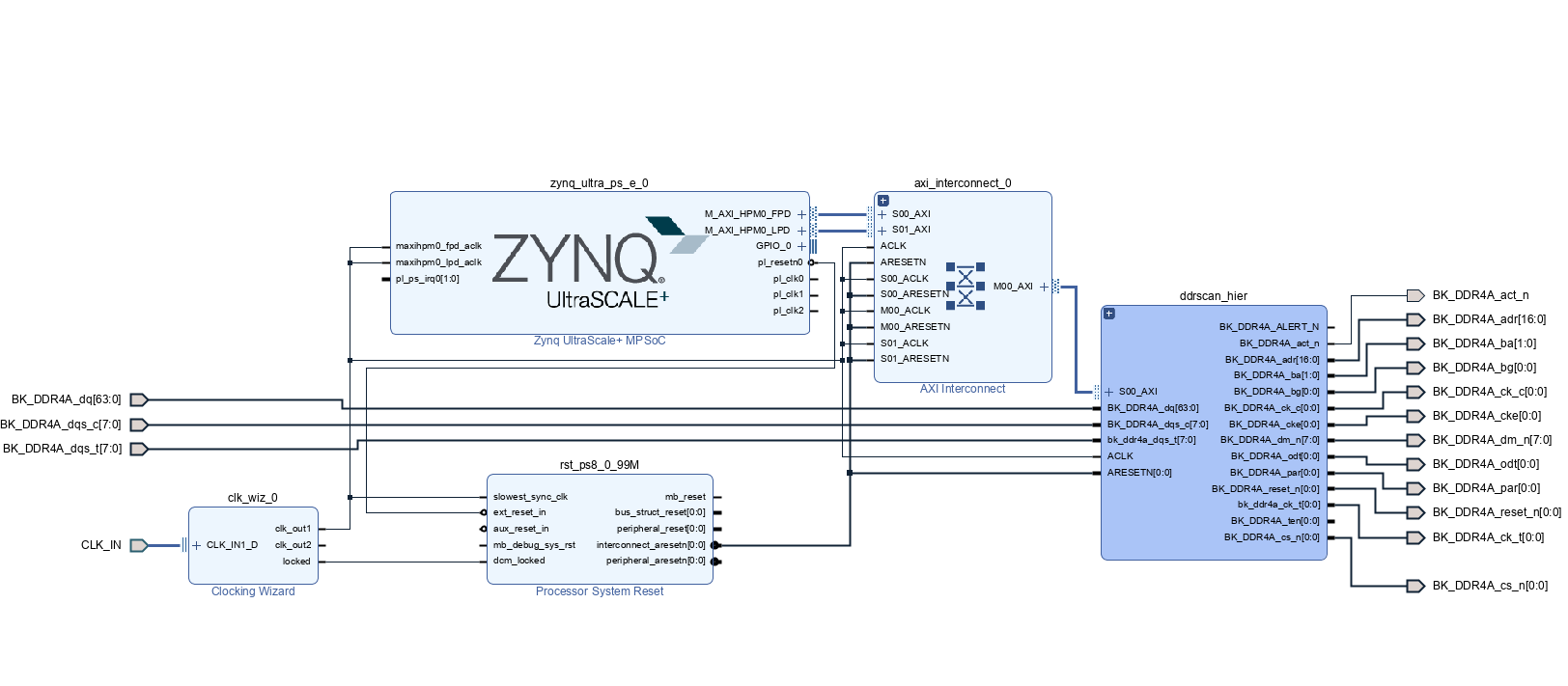

上記の論理をMPSoCから制御できる回路を以下のように構築します。

出典:Vivado® ML Edition

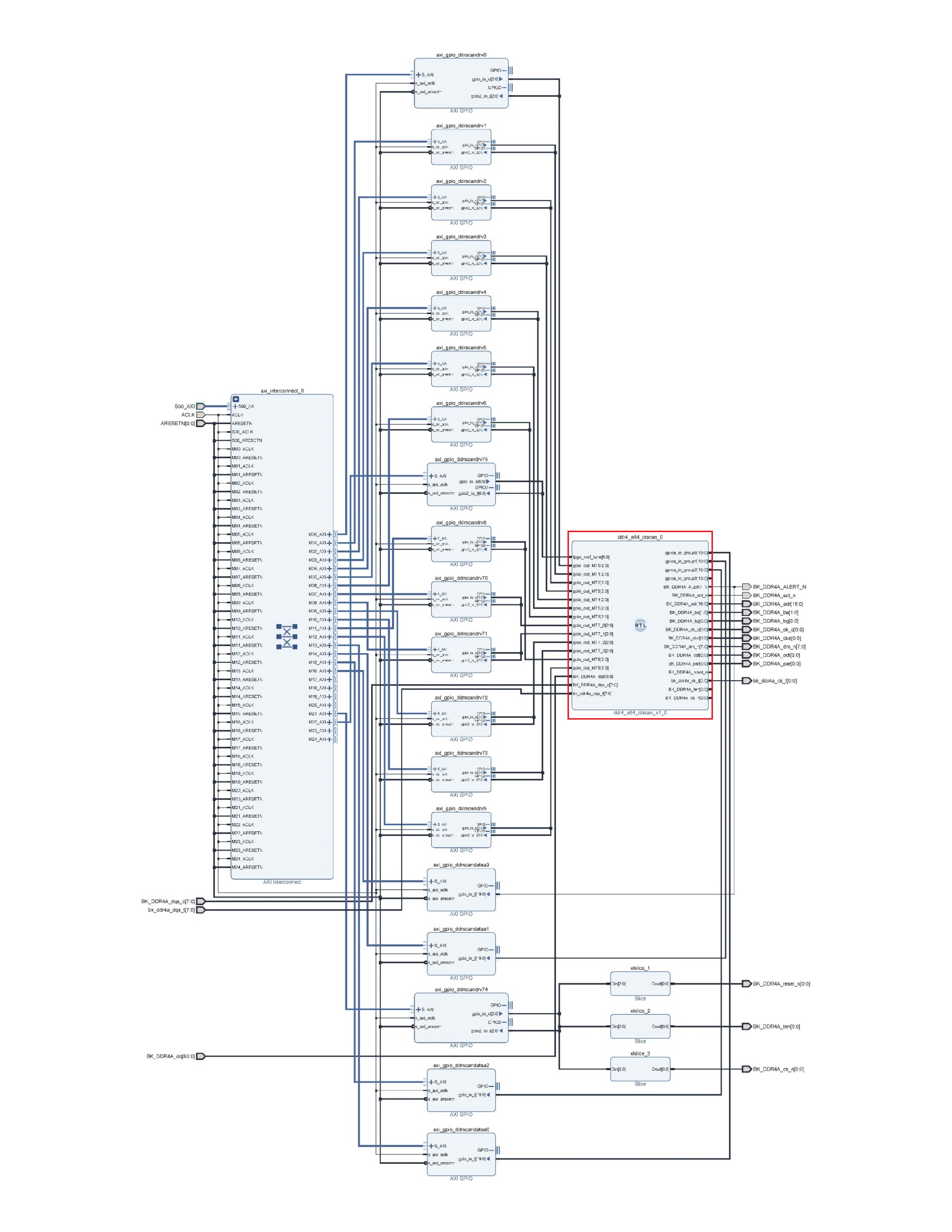

ddrscan_hireの内部構成

出典:Vivado® ML Edition

ddr4_a64_ctscan.vのRTLソース(ddrscan_hireの内部構成内の赤枠部)

///////////////////////////////////////////////////////////////////////////

module ddr4_a64_ctscan(

fpga_vref_tune,

gpio_out_MT0,

gpio_out_MT1,

gpio_out_MT2,

gpio_out_MT3,

gpio_out_MT4,

gpio_out_MT5,

gpio_out_MT6,

gpio_out_MT7_0,

gpio_out_MT7_1,

gpio_out_MT7_2,

gpio_out_MT7_3,

gpio_out_MT8,

gpio_out_MT9,

gpioa_in_group0,

gpioa_in_group1,

gpioa_in_group2,

gpioa_in_group3,

BK_DDR4A_ALERT_N,

BK_DDR4A_act_n,

BK_DDR4A_adr,

BK_DDR4A_ba,

BK_DDR4A_bg,

BK_DDR4A_ck_c,

BK_DDR4A_cke,

BK_DDR4A_dm_n,

BK_DDR4A_odt,

BK_DDR4A_par,

BK_DDR4A_reset_n,

bk_ddr4a_ck_t,

BK_DDR4A_dq,

BK_DDR4A_dqs_c,

bk_ddr4a_dqs_t,

BK_DDR4A_ten,

BK_DDR4A_cs_n

);

input [6:0] fpga_vref_tune;

input [2:0] gpio_out_MT0;

input [2:0] gpio_out_MT1;

input [2:0] gpio_out_MT2;

input [2:0] gpio_out_MT3;

input [2:0] gpio_out_MT4;

input [2:0] gpio_out_MT5;

input [2:0] gpio_out_MT6;

input [2:0] gpio_out_MT7_0;

input [2:0] gpio_out_MT7_1;

input [2:0] gpio_out_MT7_2;

input [2:0] gpio_out_MT7_3;

input [2:0] gpio_out_MT8;

input [2:0] gpio_out_MT9;

output [19:0] gpioa_in_group0;

output [19:0] gpioa_in_group1;

output [19:0] gpioa_in_group2;

output [19:0] gpioa_in_group3;

output BK_DDR4A_ALERT_N;

output BK_DDR4A_act_n;

output [16:0] BK_DDR4A_adr;

output [1:0] BK_DDR4A_ba;

output [0:0] BK_DDR4A_bg;

output [0:0] BK_DDR4A_ck_c;

output [0:0] BK_DDR4A_cke;

output [7:0] BK_DDR4A_dm_n;

output [0:0] BK_DDR4A_odt;

output [0:0] BK_DDR4A_par;

output BK_DDR4A_reset_n;

output [0:0] bk_ddr4a_ck_t;

input [63:0] BK_DDR4A_dq;

input [7:0] BK_DDR4A_dqs_c;

input [7:0] bk_ddr4a_dqs_t;

output [0:0] BK_DDR4A_ten;

output [0:0] BK_DDR4A_cs_n;

wire [63:0] s_BK_DDR4A_dq;

wire [7:0] s_BK_DDR4A_dqs_c;

wire [7:0] s_bk_ddr4a_dqs_t;

wire [7:0] VrefA;

assign BK_DDR4A_adr[1] = gpio_out_MT0[2];

assign BK_DDR4A_adr[6] = gpio_out_MT0[1];

assign BK_DDR4A_par[0] = gpio_out_MT0[0];

assign BK_DDR4A_adr[8] = gpio_out_MT1[2];

assign BK_DDR4A_ALERT_N = gpio_out_MT1[1];

assign BK_DDR4A_adr[9] = gpio_out_MT1[0];

assign BK_DDR4A_adr[2] = gpio_out_MT2[2];

assign BK_DDR4A_adr[5] = gpio_out_MT2[1];

assign BK_DDR4A_adr[13] = gpio_out_MT2[0];

assign BK_DDR4A_adr[0] = gpio_out_MT3[2];

assign BK_DDR4A_adr[7] = gpio_out_MT3[1];

assign BK_DDR4A_adr[11] = gpio_out_MT3[0];

assign BK_DDR4A_ck_c[0] = gpio_out_MT4[2];

assign BK_DDR4A_odt[0] = gpio_out_MT4[1];

assign BK_DDR4A_adr[15] = gpio_out_MT4[0];

assign BK_DDR4A_cke[0] = gpio_out_MT5[2];

assign BK_DDR4A_adr[16] = gpio_out_MT5[1];

assign BK_DDR4A_adr[10] = gpio_out_MT5[0];

assign BK_DDR4A_act_n = gpio_out_MT6[2];

assign BK_DDR4A_adr[4] = gpio_out_MT6[1];

assign BK_DDR4A_ba[1] = gpio_out_MT6[0];

assign BK_DDR4A_dm_n[1] = gpio_out_MT7_0[2];

assign BK_DDR4A_dm_n[0] = gpio_out_MT7_0[1];

assign bk_ddr4a_ck_t[0] = gpio_out_MT7_0[0];

assign BK_DDR4A_dm_n[3] = gpio_out_MT7_1[2];

assign BK_DDR4A_dm_n[2] = gpio_out_MT7_1[1];

assign BK_DDR4A_dm_n[5] = gpio_out_MT7_2[2];

assign BK_DDR4A_dm_n[4] = gpio_out_MT7_2[1];

assign BK_DDR4A_dm_n[7] = gpio_out_MT7_3[2];

assign BK_DDR4A_dm_n[6] = gpio_out_MT7_3[1];

assign BK_DDR4A_adr[14] = gpio_out_MT8[2];

assign BK_DDR4A_adr[12] = gpio_out_MT8[1];

assign BK_DDR4A_ba[0] = gpio_out_MT8[0];

assign BK_DDR4A_bg[0] = gpio_out_MT9[2];

assign BK_DDR4A_adr[3] = gpio_out_MT9[1];

assign BK_DDR4A_reset_n = gpio_out_MT9[0];

assign gpioa_in_group0 = {

s_BK_DDR4A_dq[0],

s_BK_DDR4A_dq[1],

s_BK_DDR4A_dq[2],

s_BK_DDR4A_dq[3],

s_BK_DDR4A_dq[4],

s_BK_DDR4A_dq[5],

s_BK_DDR4A_dq[6],

s_BK_DDR4A_dq[7],

s_BK_DDR4A_dq[8],

s_BK_DDR4A_dq[9],

s_BK_DDR4A_dq[10],

s_BK_DDR4A_dq[11],

s_BK_DDR4A_dq[12],

s_BK_DDR4A_dq[13],

s_BK_DDR4A_dq[14],

s_BK_DDR4A_dq[15],

s_bk_ddr4a_dqs_t[0],

s_BK_DDR4A_dqs_c[0],

s_bk_ddr4a_dqs_t[1],

s_BK_DDR4A_dqs_c[1]

};

assign gpioa_in_group1 = {s_BK_DDR4A_dq[16],

s_BK_DDR4A_dq[17],

s_BK_DDR4A_dq[18],

s_BK_DDR4A_dq[19],

s_BK_DDR4A_dq[20],

s_BK_DDR4A_dq[21],

s_BK_DDR4A_dq[22],

s_BK_DDR4A_dq[23],

s_BK_DDR4A_dq[24],

s_BK_DDR4A_dq[25],

s_BK_DDR4A_dq[26],

s_BK_DDR4A_dq[27],

s_BK_DDR4A_dq[28],

s_BK_DDR4A_dq[29],

s_BK_DDR4A_dq[30],

s_BK_DDR4A_dq[31],

s_bk_ddr4a_dqs_t[2],

s_BK_DDR4A_dqs_c[2],

s_bk_ddr4a_dqs_t[3],

s_BK_DDR4A_dqs_c[3]

};

assign gpioa_in_group2 = {s_BK_DDR4A_dq[32],

s_BK_DDR4A_dq[33],

s_BK_DDR4A_dq[34],

s_BK_DDR4A_dq[35],

s_BK_DDR4A_dq[36],

s_BK_DDR4A_dq[37],

s_BK_DDR4A_dq[38],

s_BK_DDR4A_dq[39],

s_BK_DDR4A_dq[40],

s_BK_DDR4A_dq[41],

s_BK_DDR4A_dq[42],

s_BK_DDR4A_dq[43],

s_BK_DDR4A_dq[44],

s_BK_DDR4A_dq[45],

s_BK_DDR4A_dq[46],

s_BK_DDR4A_dq[47],

s_bk_ddr4a_dqs_t[4],

s_BK_DDR4A_dqs_c[4],

s_bk_ddr4a_dqs_t[5],

s_BK_DDR4A_dqs_c[5]

};

assign gpioa_in_group3 = {s_BK_DDR4A_dq[48],

s_BK_DDR4A_dq[49],

s_BK_DDR4A_dq[50],

s_BK_DDR4A_dq[51],

s_BK_DDR4A_dq[52],

s_BK_DDR4A_dq[53],

s_BK_DDR4A_dq[54],

s_BK_DDR4A_dq[55],

s_BK_DDR4A_dq[56],

s_BK_DDR4A_dq[57],

s_BK_DDR4A_dq[58],

s_BK_DDR4A_dq[59],

s_BK_DDR4A_dq[60],

s_BK_DDR4A_dq[61],

s_BK_DDR4A_dq[62],

s_BK_DDR4A_dq[63],

s_bk_ddr4a_dqs_t[6],

s_BK_DDR4A_dqs_c[6],

s_bk_ddr4a_dqs_t[7],

s_BK_DDR4A_dqs_c[7]

};

assign BK_DDR4A_ten = 1'b1;

assign BK_DDR4A_cs_n = 1'b0;

HPIO_VREF #(.VREF_CNTR("FABRIC_RANGE1")) u7_hpio_vrefA ( .FABRIC_VREF_TUNE (fpga_vref_tune), .VREF (VrefA[7]) );

HPIO_VREF #(.VREF_CNTR("FABRIC_RANGE1")) u6_hpio_vrefA ( .FABRIC_VREF_TUNE (fpga_vref_tune), .VREF (VrefA[6]) );

HPIO_VREF #(.VREF_CNTR("FABRIC_RANGE1")) u5_hpio_vrefA ( .FABRIC_VREF_TUNE (fpga_vref_tune), .VREF (VrefA[5]) );

HPIO_VREF #(.VREF_CNTR("FABRIC_RANGE1")) u4_hpio_vrefA ( .FABRIC_VREF_TUNE (fpga_vref_tune), .VREF (VrefA[4]) );

HPIO_VREF #(.VREF_CNTR("FABRIC_RANGE1")) u3_hpio_vrefA ( .FABRIC_VREF_TUNE (fpga_vref_tune), .VREF (VrefA[3]) );

HPIO_VREF #(.VREF_CNTR("FABRIC_RANGE1")) u2_hpio_vrefA ( .FABRIC_VREF_TUNE (fpga_vref_tune), .VREF (VrefA[2]) );

HPIO_VREF #(.VREF_CNTR("FABRIC_RANGE1")) u1_hpio_vrefA ( .FABRIC_VREF_TUNE (fpga_vref_tune), .VREF (VrefA[1]) );

HPIO_VREF #(.VREF_CNTR("FABRIC_RANGE1")) u0_hpio_vrefA ( .FABRIC_VREF_TUNE (fpga_vref_tune), .VREF (VrefA[0]) );

//////////////////////////////////////////////////////////////////////////

IBUFE3 IBUFa79( .I(BK_DDR4A_dq[25] ), .O(s_BK_DDR4A_dq[25] ), .VREF (VrefA[7]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa78( .I(BK_DDR4A_dq[29] ), .O(s_BK_DDR4A_dq[29] ), .VREF (VrefA[7]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa77( .I(BK_DDR4A_dq[28] ), .O(s_BK_DDR4A_dq[28] ), .VREF (VrefA[7]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa76( .I(BK_DDR4A_dq[24] ), .O(s_BK_DDR4A_dq[24] ), .VREF (VrefA[7]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa75( .I(BK_DDR4A_dqs_c[3]), .O(s_BK_DDR4A_dqs_c[3]), .VREF (VrefA[7]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa74( .I(bk_ddr4a_dqs_t[3]), .O(s_bk_ddr4a_dqs_t[3]), .VREF (VrefA[7]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa73( .I(BK_DDR4A_dq[30] ), .O(s_BK_DDR4A_dq[30] ), .VREF (VrefA[7]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa72( .I(BK_DDR4A_dq[26] ), .O(s_BK_DDR4A_dq[26] ), .VREF (VrefA[7]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa71( .I(BK_DDR4A_dq[27] ), .O(s_BK_DDR4A_dq[27] ), .VREF (VrefA[7]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa70( .I(BK_DDR4A_dq[31] ), .O(s_BK_DDR4A_dq[31] ), .VREF (VrefA[7]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa69( .I(BK_DDR4A_dqs_c[2]), .O(s_BK_DDR4A_dqs_c[2]), .VREF (VrefA[6]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa68( .I(bk_ddr4a_dqs_t[2]), .O(s_bk_ddr4a_dqs_t[2]), .VREF (VrefA[6]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa67( .I(BK_DDR4A_dq[19] ), .O(s_BK_DDR4A_dq[19] ), .VREF (VrefA[6]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa66( .I(BK_DDR4A_dq[23] ), .O(s_BK_DDR4A_dq[23] ), .VREF (VrefA[6]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa65( .I(BK_DDR4A_dq[18] ), .O(s_BK_DDR4A_dq[18] ), .VREF (VrefA[6]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa64( .I(BK_DDR4A_dq[16] ), .O(s_BK_DDR4A_dq[16] ), .VREF (VrefA[6]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa63( .I(BK_DDR4A_dq[17] ), .O(s_BK_DDR4A_dq[17] ), .VREF (VrefA[6]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa62( .I(BK_DDR4A_dq[21] ), .O(s_BK_DDR4A_dq[21] ), .VREF (VrefA[6]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa61( .I(BK_DDR4A_dq[22] ), .O(s_BK_DDR4A_dq[22] ), .VREF (VrefA[6]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa60( .I(BK_DDR4A_dq[20] ), .O(s_BK_DDR4A_dq[20] ), .VREF (VrefA[6]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa59( .I(BK_DDR4A_dq[12] ), .O(s_BK_DDR4A_dq[12] ), .VREF (VrefA[5]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa58( .I(BK_DDR4A_dq[11] ), .O(s_BK_DDR4A_dq[11] ), .VREF (VrefA[5]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa57( .I(BK_DDR4A_dq[10] ), .O(s_BK_DDR4A_dq[10] ), .VREF (VrefA[5]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa56( .I(BK_DDR4A_dq[14] ), .O(s_BK_DDR4A_dq[14] ), .VREF (VrefA[5]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa55( .I(BK_DDR4A_dqs_c[1]), .O(s_BK_DDR4A_dqs_c[1]), .VREF (VrefA[5]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa54( .I(bk_ddr4a_dqs_t[1]), .O(s_bk_ddr4a_dqs_t[1]), .VREF (VrefA[5]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa53( .I(BK_DDR4A_dq[13] ), .O(s_BK_DDR4A_dq[13] ), .VREF (VrefA[5]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa52( .I(BK_DDR4A_dq[15] ), .O(s_BK_DDR4A_dq[15] ), .VREF (VrefA[5]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa51( .I(BK_DDR4A_dq[9] ), .O(s_BK_DDR4A_dq[9] ), .VREF (VrefA[5]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa50( .I(BK_DDR4A_dq[8] ), .O(s_BK_DDR4A_dq[8] ), .VREF (VrefA[5]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa49( .I(BK_DDR4A_dq[6] ), .O(s_BK_DDR4A_dq[6] ), .VREF (VrefA[4]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa48( .I(BK_DDR4A_dq[4] ), .O(s_BK_DDR4A_dq[4] ), .VREF (VrefA[4]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa47( .I(BK_DDR4A_dq[7] ), .O(s_BK_DDR4A_dq[7] ), .VREF (VrefA[4]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa46( .I(BK_DDR4A_dq[1] ), .O(s_BK_DDR4A_dq[1] ), .VREF (VrefA[4]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa45( .I(BK_DDR4A_dqs_c[0]), .O(s_BK_DDR4A_dqs_c[0]), .VREF (VrefA[4]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa44( .I(bk_ddr4a_dqs_t[0]), .O(s_bk_ddr4a_dqs_t[0]), .VREF (VrefA[4]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa43( .I(BK_DDR4A_dq[3] ), .O(s_BK_DDR4A_dq[3] ), .VREF (VrefA[4]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa42( .I(BK_DDR4A_dq[5] ), .O(s_BK_DDR4A_dq[5] ), .VREF (VrefA[4]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa41( .I(BK_DDR4A_dq[2] ), .O(s_BK_DDR4A_dq[2] ), .VREF (VrefA[4]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa40( .I(BK_DDR4A_dq[0] ), .O(s_BK_DDR4A_dq[0] ), .VREF (VrefA[4]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa39( .I(BK_DDR4A_dq[61] ), .O(s_BK_DDR4A_dq[61] ), .VREF (VrefA[3]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa38( .I(BK_DDR4A_dq[57] ), .O(s_BK_DDR4A_dq[57] ), .VREF (VrefA[3]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa37( .I(BK_DDR4A_dq[63] ), .O(s_BK_DDR4A_dq[63] ), .VREF (VrefA[3]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa36( .I(BK_DDR4A_dq[59] ), .O(s_BK_DDR4A_dq[59] ), .VREF (VrefA[3]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa35( .I(BK_DDR4A_dqs_c[7]), .O(s_BK_DDR4A_dqs_c[7]), .VREF (VrefA[3]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa34( .I(bk_ddr4a_dqs_t[7]), .O(s_bk_ddr4a_dqs_t[7]), .VREF (VrefA[3]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa33( .I(BK_DDR4A_dq[62] ), .O(s_BK_DDR4A_dq[62] ), .VREF (VrefA[3]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa32( .I(BK_DDR4A_dq[58] ), .O(s_BK_DDR4A_dq[58] ), .VREF (VrefA[3]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa31( .I(BK_DDR4A_dq[60] ), .O(s_BK_DDR4A_dq[60] ), .VREF (VrefA[3]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa30( .I(BK_DDR4A_dq[56] ), .O(s_BK_DDR4A_dq[56] ), .VREF (VrefA[3]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa29( .I(BK_DDR4A_dqs_c[6]), .O(s_BK_DDR4A_dqs_c[6]), .VREF (VrefA[2]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa28( .I(bk_ddr4a_dqs_t[6]), .O(s_bk_ddr4a_dqs_t[6]), .VREF (VrefA[2]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa27( .I(BK_DDR4A_dq[51] ), .O(s_BK_DDR4A_dq[51] ), .VREF (VrefA[2]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa26( .I(BK_DDR4A_dq[49] ), .O(s_BK_DDR4A_dq[49] ), .VREF (VrefA[2]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa25( .I(BK_DDR4A_dq[54] ), .O(s_BK_DDR4A_dq[54] ), .VREF (VrefA[2]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa24( .I(BK_DDR4A_dq[48] ), .O(s_BK_DDR4A_dq[48] ), .VREF (VrefA[2]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa23( .I(BK_DDR4A_dq[55] ), .O(s_BK_DDR4A_dq[55] ), .VREF (VrefA[2]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa22( .I(BK_DDR4A_dq[53] ), .O(s_BK_DDR4A_dq[53] ), .VREF (VrefA[2]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa21( .I(BK_DDR4A_dq[52] ), .O(s_BK_DDR4A_dq[52] ), .VREF (VrefA[2]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa20( .I(BK_DDR4A_dq[50] ), .O(s_BK_DDR4A_dq[50] ), .VREF (VrefA[2]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa19( .I(BK_DDR4A_dq[45] ), .O(s_BK_DDR4A_dq[45] ), .VREF (VrefA[1]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa18( .I(BK_DDR4A_dq[41] ), .O(s_BK_DDR4A_dq[41] ), .VREF (VrefA[1]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa17( .I(BK_DDR4A_dq[40] ), .O(s_BK_DDR4A_dq[40] ), .VREF (VrefA[1]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa16( .I(BK_DDR4A_dq[47] ), .O(s_BK_DDR4A_dq[47] ), .VREF (VrefA[1]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa15( .I(BK_DDR4A_dqs_c[5]), .O(s_BK_DDR4A_dqs_c[5]), .VREF (VrefA[1]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa14( .I(bk_ddr4a_dqs_t[5]), .O(s_bk_ddr4a_dqs_t[5]), .VREF (VrefA[1]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa13( .I(BK_DDR4A_dq[42] ), .O(s_BK_DDR4A_dq[42] ), .VREF (VrefA[1]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa12( .I(BK_DDR4A_dq[43] ), .O(s_BK_DDR4A_dq[43] ), .VREF (VrefA[1]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa11( .I(BK_DDR4A_dq[46] ), .O(s_BK_DDR4A_dq[46] ), .VREF (VrefA[1]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa10( .I(BK_DDR4A_dq[44] ), .O(s_BK_DDR4A_dq[44] ), .VREF (VrefA[1]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa09( .I(BK_DDR4A_dq[35] ), .O(s_BK_DDR4A_dq[35] ), .VREF (VrefA[0]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa08( .I(BK_DDR4A_dq[32] ), .O(s_BK_DDR4A_dq[32] ), .VREF (VrefA[0]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa07( .I(BK_DDR4A_dq[37] ), .O(s_BK_DDR4A_dq[37] ), .VREF (VrefA[0]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa06( .I(BK_DDR4A_dq[33] ), .O(s_BK_DDR4A_dq[33] ), .VREF (VrefA[0]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa05( .I(BK_DDR4A_dqs_c[4]), .O(s_BK_DDR4A_dqs_c[4]), .VREF (VrefA[0]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa04( .I(bk_ddr4a_dqs_t[4]), .O(s_bk_ddr4a_dqs_t[4]), .VREF (VrefA[0]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa03( .I(BK_DDR4A_dq[39] ), .O(s_BK_DDR4A_dq[39] ), .VREF (VrefA[0]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa02( .I(BK_DDR4A_dq[38] ), .O(s_BK_DDR4A_dq[38] ), .VREF (VrefA[0]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa01( .I(BK_DDR4A_dq[34] ), .O(s_BK_DDR4A_dq[34] ), .VREF (VrefA[0]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

IBUFE3 IBUFa00( .I(BK_DDR4A_dq[36] ), .O(s_BK_DDR4A_dq[36] ), .VREF (VrefA[0]), .OSC_EN (1'b0), .OSC (4'b0000), .IBUFDISABLE (1'b0));

Endmodule

///////////////////////////////////////////////////////////////////////////////////////////////

EXAMPLEデザイン

本ブログで使用した、EXAMPLEデザインについては以下よりダウンロードしてご活用ください。

おわりに

いかがでしたでしょうか。

このようにして、AMD ザイリンクス社のVivado® ML Edition2020.2のZynq® UltraScale+ MPSoC BASEのDDR4接続モードテスト用デザインが作成できました。

次回からはVitis® 2020.2でソフト環境の構築方法や、サンプリングテストプログラムを紹介したいと思います。

このブログは「FPGA設計ブログ一覧」の

6. 実機評価のひとつです。