IBERTデザインの作成 【第1回】

皆さん、こんにちは。

Vivado® ML Editionにはトランシーバを評価するためのIBERT(Integrated Bit Error Ratio Test)があります。

今回はIBERTデザインの作成方法を紹介したいと思います。

それでは始めましょう。

このブログは「FPGA設計ブログ一覧」の

6. 実機評価のひとつです。

目次

IBERTデザイン作成概要

IBERTのデザインを作成するには以下の手順が必要になります。

- IBERT IPコアの作成

- 作成したIBERT IPコアからサンプルデザインを生成

作成環境

今回は例としてVivado®2020.2を使用してKintex® Ultrascale™用のIBERTを作成します。

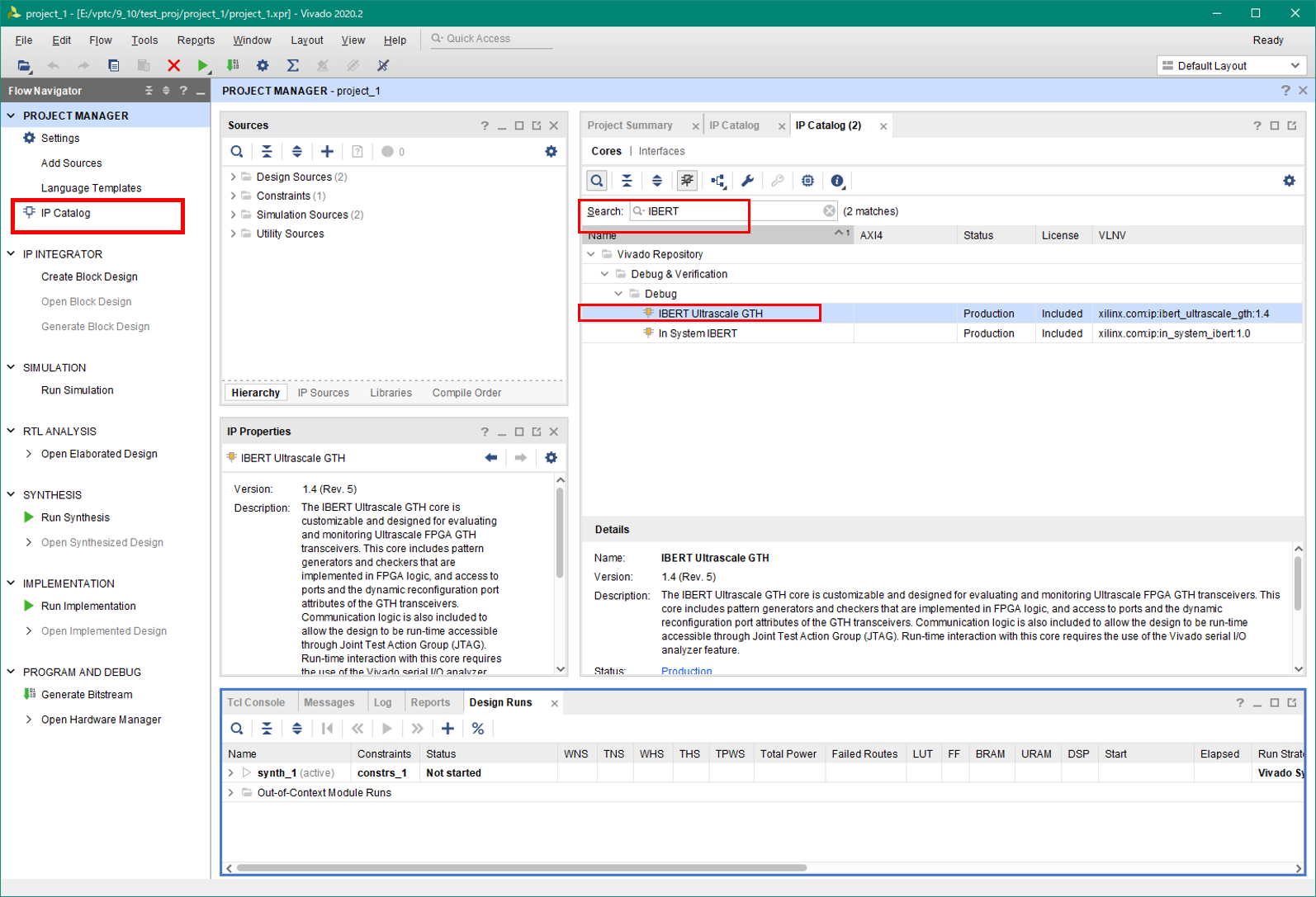

IBERT IPコアの作成

IBERTのIPのコアはIP Catalogから作成します。

- 左側Flow NavigatorのツリーからIP Catalogを選択

- 右側にIP Catalogのタブが現れるのでSearchウインドウにIBERTと入力

- IBERT Ultrascale GTHを選択

出典:Vivado® ML Edition

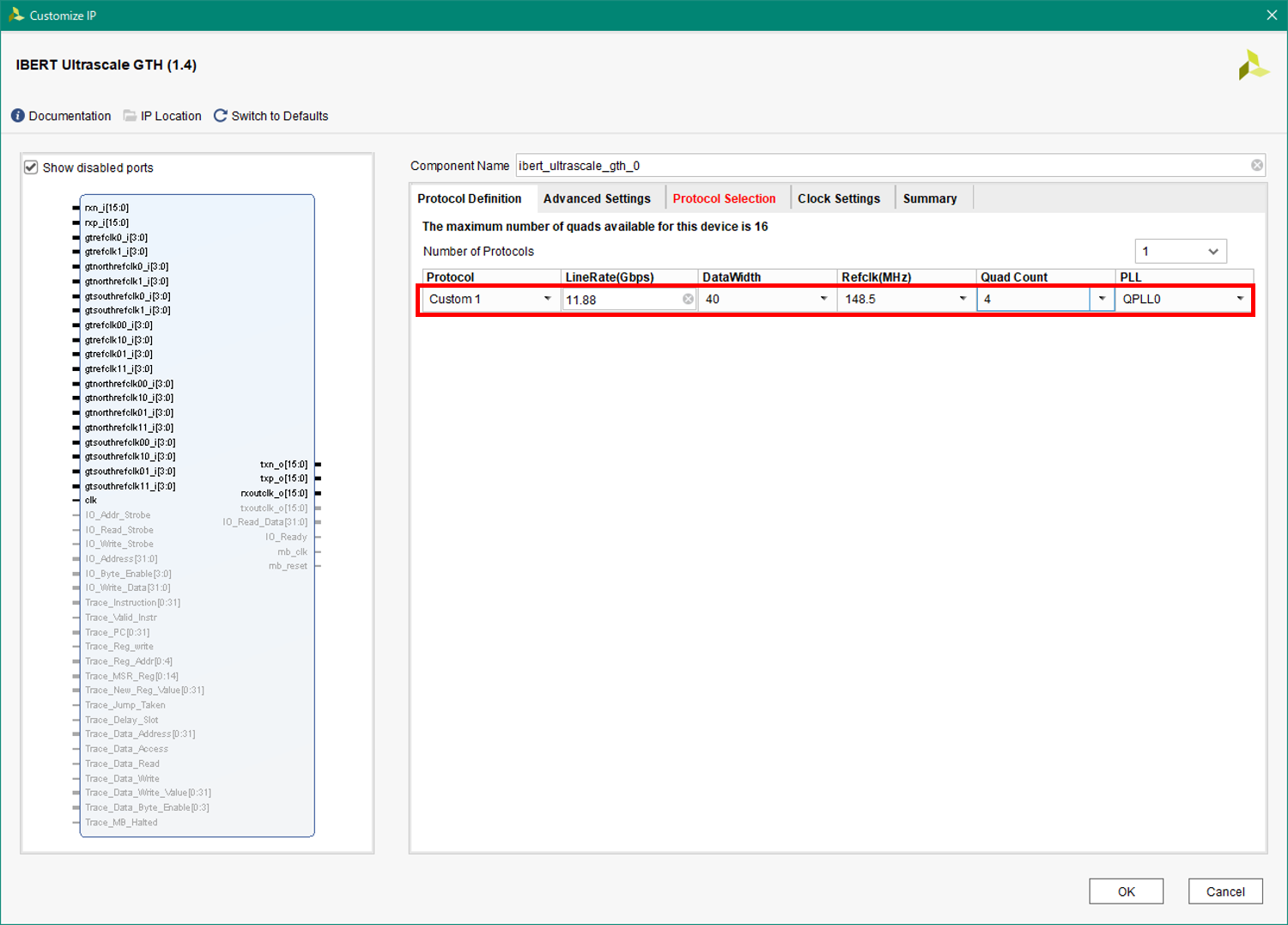

IBERT IPコア設定

IBERTのCustomize IPウインドウが現れます。

ここでは生成するIBERT IPコアの設定を行います。

Protocol Definitionタブ

ここではIBERTで使用する伝送レート、リファレンスクロック、使用Quad(トランシーバ数)、PLL選択などが行えます。

複数のProtocolを作成して別々のトランシーバに設定することも可能です。

ここでは例として下記の設定としています。

- LineRate(Gbps) : 11.88 Gbps

- DataWidth : 40 bit

- Refclk(MHz) : 148.5MHz

- Quad Count : 4

- PLL : QPLL0

出典:Vivado® ML Edition

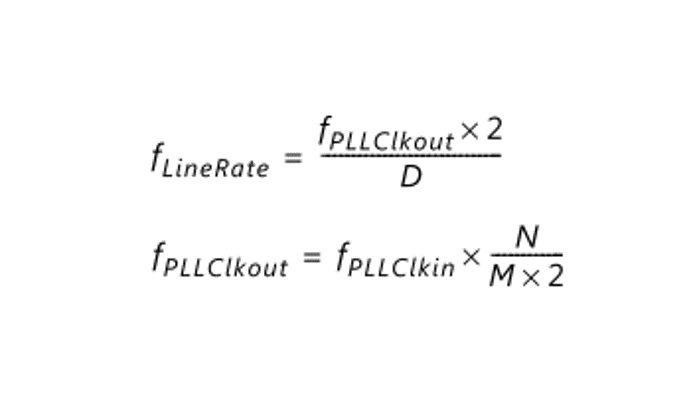

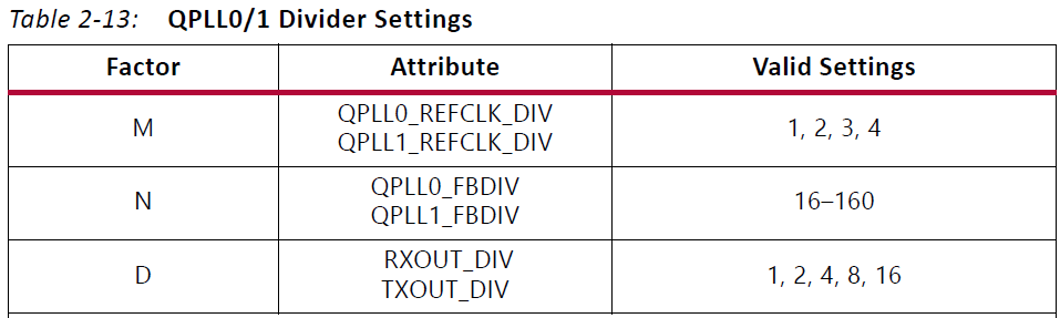

Refclk(MHz)はLineRate(Gbps)を設定すると複数の周波数から選択可能となりますが、LineRateとRefclkの関係は下記になります。

出典: UltraScale Architecture GTH Transceivers User Guide (UG576) QPLL0/1 Divider Settings

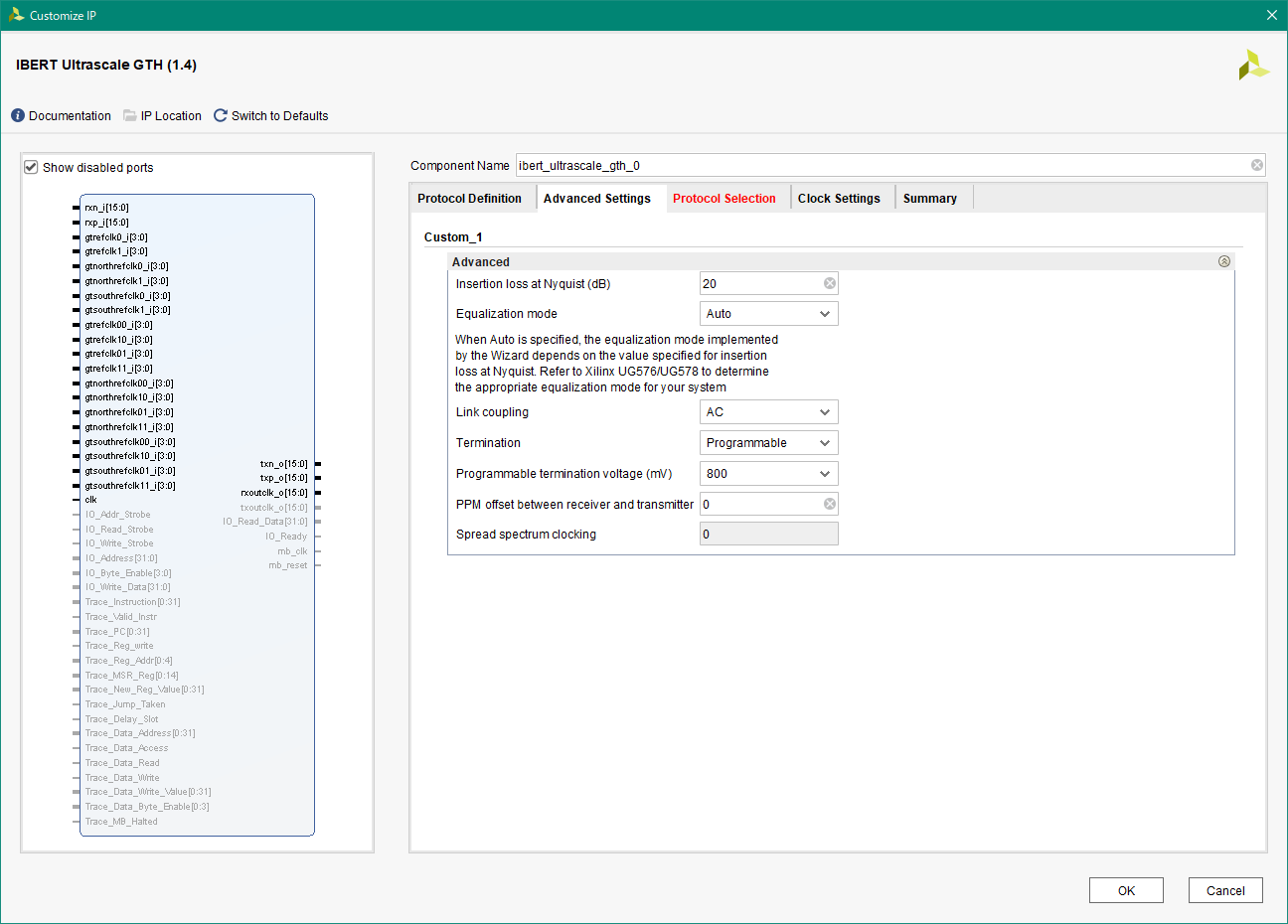

Advanced Settingsタブ

ここではイコライザのモード(DFE/LPM)やカップリングの方式等を設定できます。

イコライザのモードはIBERT使用中にも変更可能です。

出典:Vivado® ML Edition

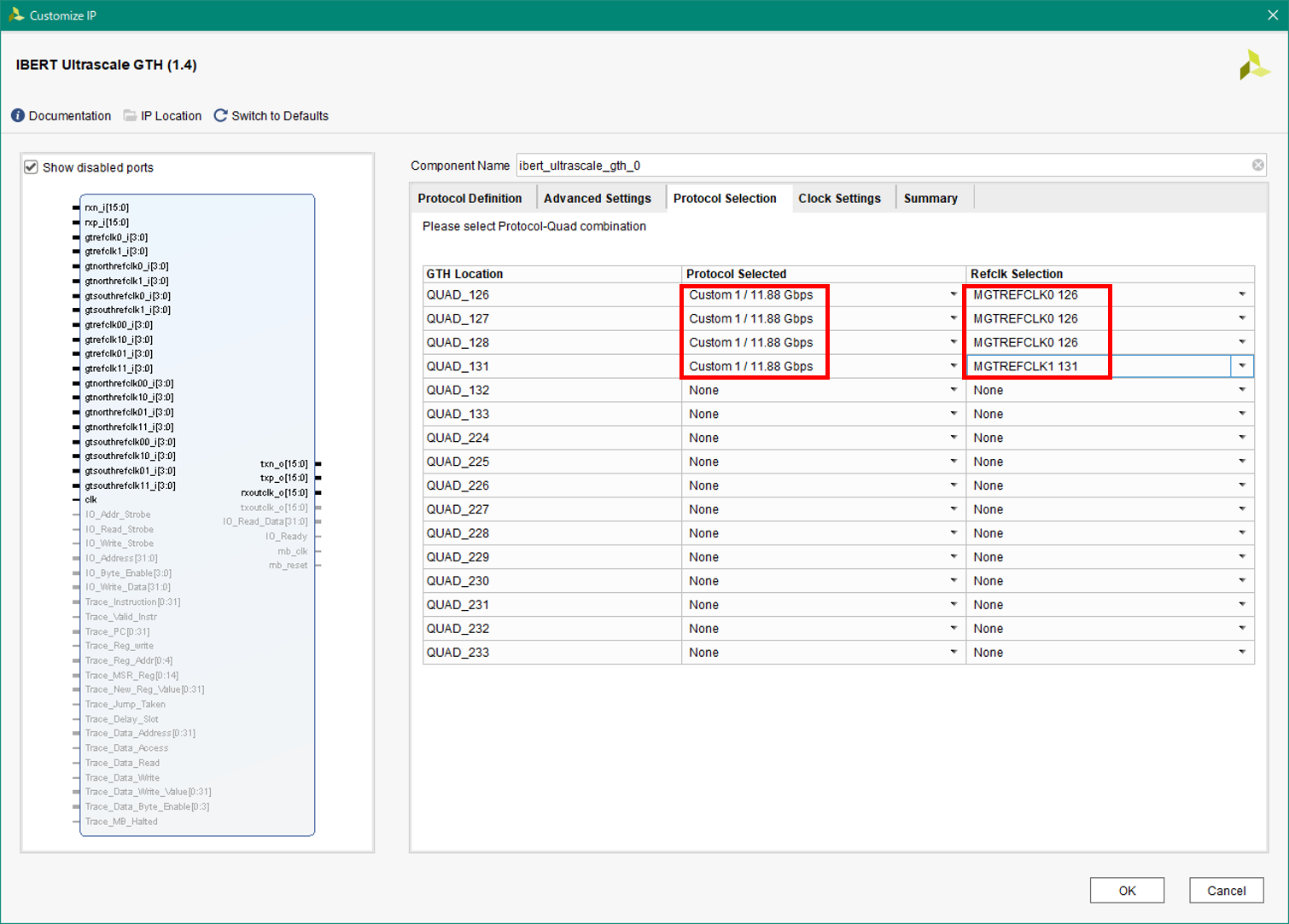

Protocol Slectionタブ

ここではトランシーバのQuad毎に作成したProtocolを設定します。

Quad Countを4としたので4つのQuadに11.88GbpsのProtocolを設定しています。

Refclk SlectionはQuadのBankに入力されているMGTREFCLK 0/1を選択します。

また同一のBankでなくても隣接する上下2Bankからクロック供給が可能です。

ここでは例として以下の設定としています。

- QUAD_126/127/128/131 にCustom/11.88GbpsのProtocolを設定

- QUAD_126/127/128のRefclkはMGTREFCLK0 126から供給

- QUAD_131のRefclkはMGTREFCLK1 131から供給

注意点として複数のMGTREFCLKを設定した場合でもProtocol Definitionタブで設定した周波数と同じクロックにする必要があります。

出典:Vivado® ML Edition

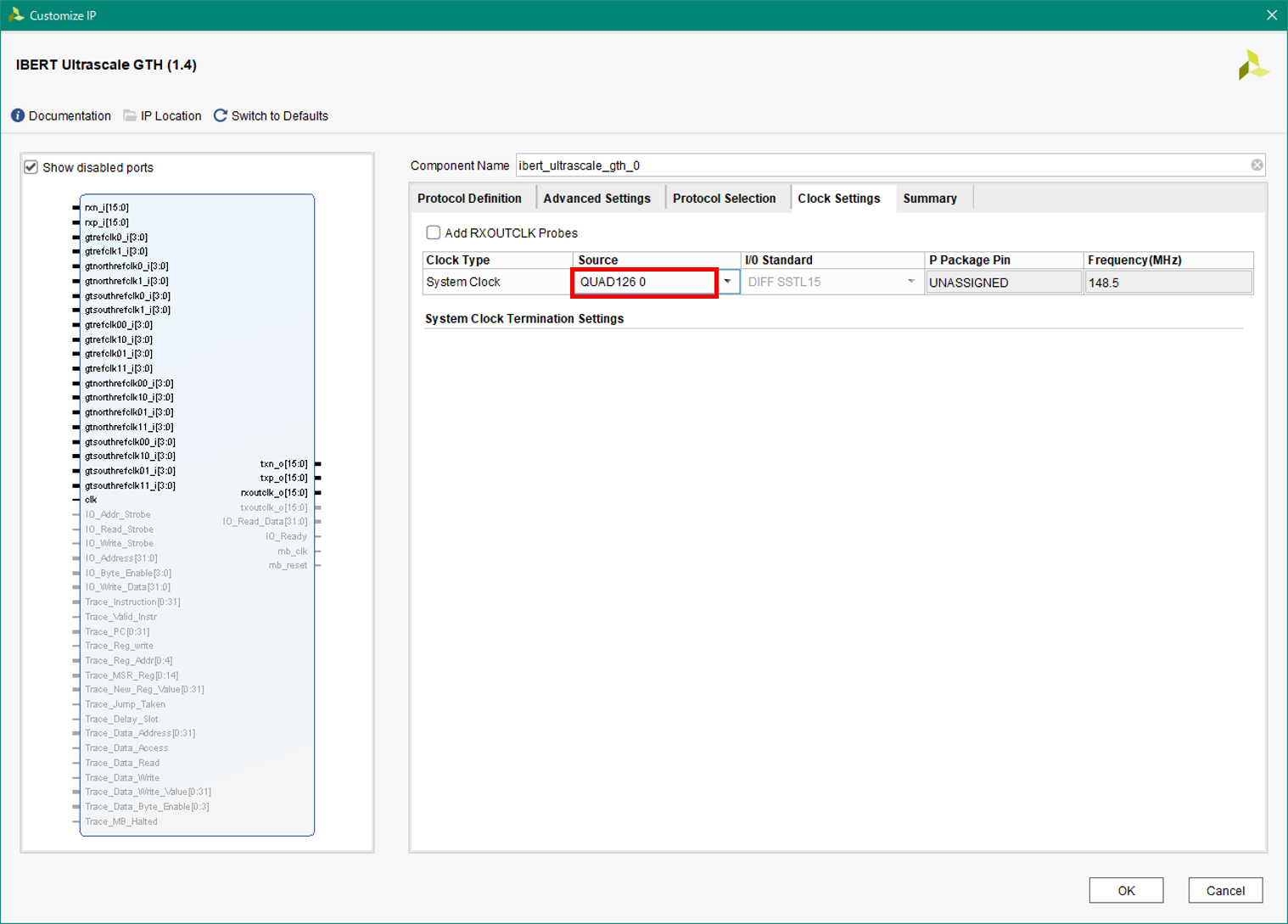

Clock Settingsタブ

ここでは内部クロックの入力を選択します。

クロックは外部端子または使用しているQuadから供給可能で、外部端子とした場合には端子のピン番号と周波数、I/O Standardを設定します。

Quadから供給する場合は使用するQuadを選択するのみとなります。

出典:Vivado® ML Edition

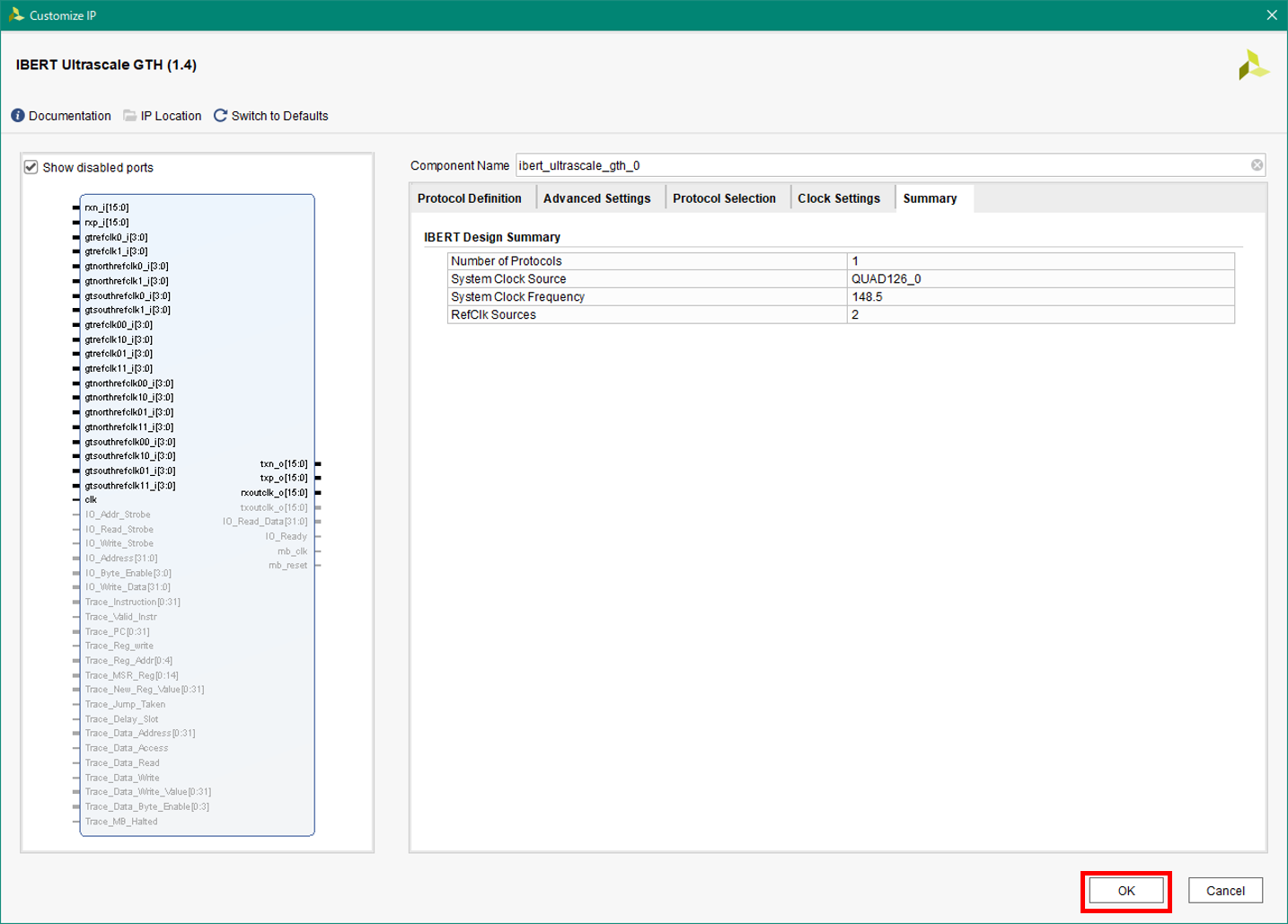

Summaryタブ

ここでは設定したデザインのサマリーが表示され、OKとすることでIBERTのIPコアが生成されます。

出典:Vivado® ML Edition

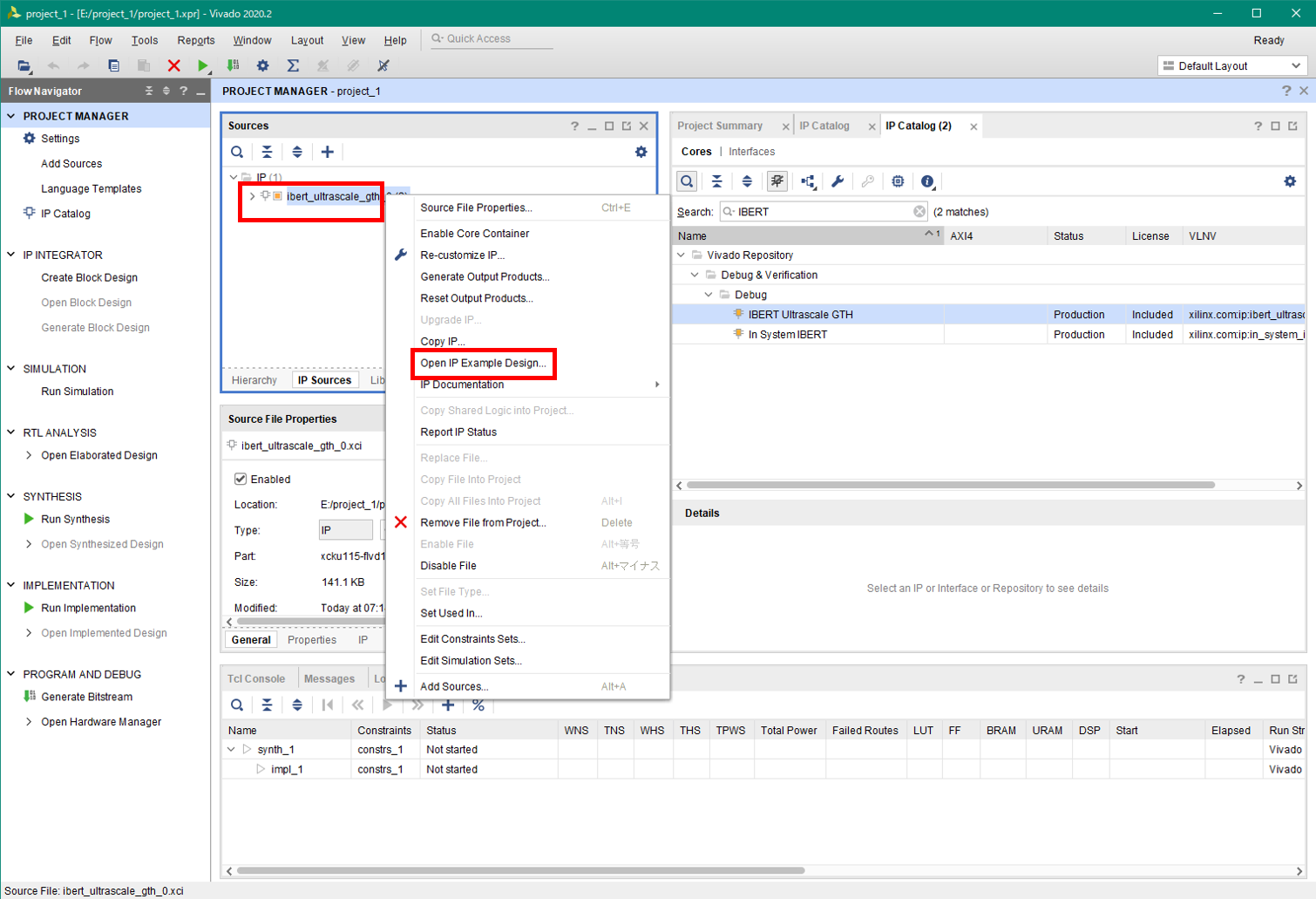

作成したIBERT IPコアからサンプルデザインを生成

IBERT IPコアを作成しただけでは、Bitファイルを生成しないため、サンプルデザインを生成します。

作成したIBERT IPコアを右クリックしてOpen Example Designを選択します。

出典:Vivado® ML Edition

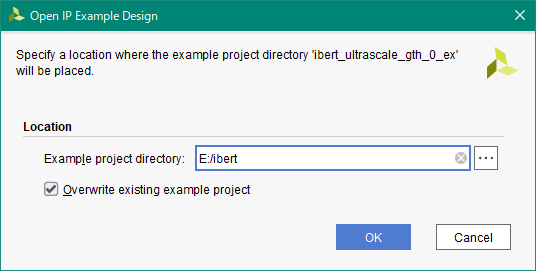

サンプルデザインは新しいプロジェクトとして開かれるので、サンプルデザインのプロジェクトを作成するフォルダを選択します。

出典:Vivado® ML Edition

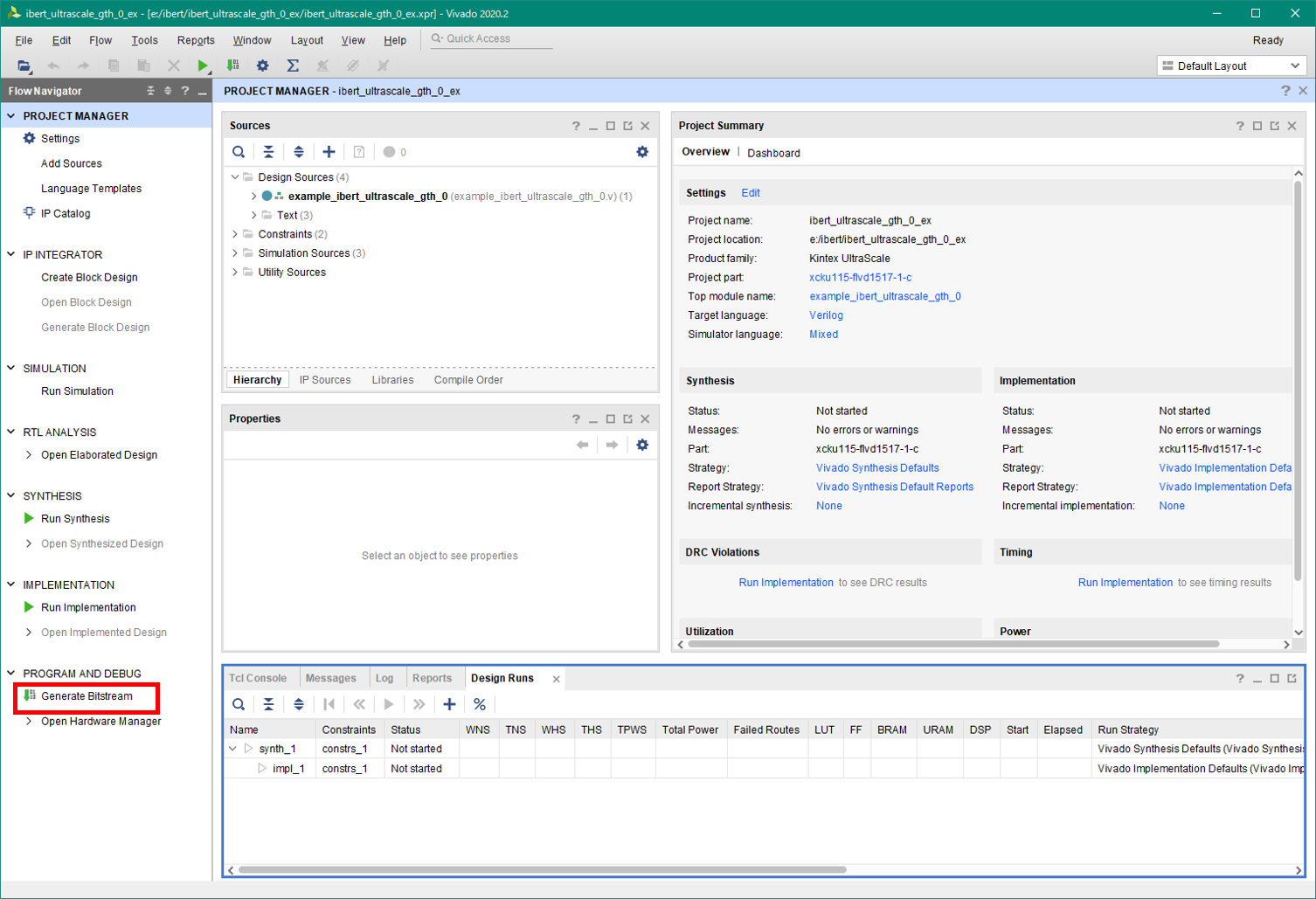

サンプルデザインを生成すると新しくコンパイル可能な環境のVivado®が開くのでGenerate Bitstreamを選択してBitファイルを生成します。

出典:Vivado® ML Edition

生成されたBitファイルは以下のフォルダに生成されます。

(選択フォルダ)\ibert_ultrascale_gth_0_ex\ibert_ultrascale_gth_0_ex.runs\impl_1\

書き込みに必要なデザインのBitファイルは以下の2つになります。

- example_ibert_ultrascale_gth_0.bit

- example_ibert_ultrascale_gth_0.ltx

おわりに

いかがでしたでしょうか。今回はIBERTデザインの生成を行いました。

次回はIBERTの使い方を紹介したいと思います。

最後までご覧いただきありがとうございました。

弊社ではFPGA設計や回路図設計、レイアウト設計、ソフトウェア設計、筐体設計などを受託開発しています。

サービス内容をWEBサイトに掲載していますので、ぜひご覧ください。

このブログは「FPGA設計ブログ一覧」の

6. 実機評価のひとつです。