IBERTデザインの使用方法 【第2回】

皆さん、こんにちは。

Vivado® ML Editionにはトランシーバを評価するためのIBERT(Integrated Bit Error Ratio Test)があります。 前回 はIBERTデザインの作成方法について紹介をしました。

今回は前回作成したIBERTデザインの基本的な使用方法を紹介したいと思います。

それでは始めましょう。

このブログは「FPGA設計ブログ一覧」の

6. 実機評価のひとつです。

目次

IBERTでできること

IBERTでは、トランシーバを使用した以下のような機能を評価することができます。

- 送受信カウント、BERの測定

- テストパタンの生成とチェック(PRBS等)

- 送信トランシーバのエンファシス設定

- 送信トランシーバの振幅設定

- 受信トランシーバのイコライザ設定

- ループバック設定

- 送信エラー挿入

- デザイン書き込み

デザイン書き込み

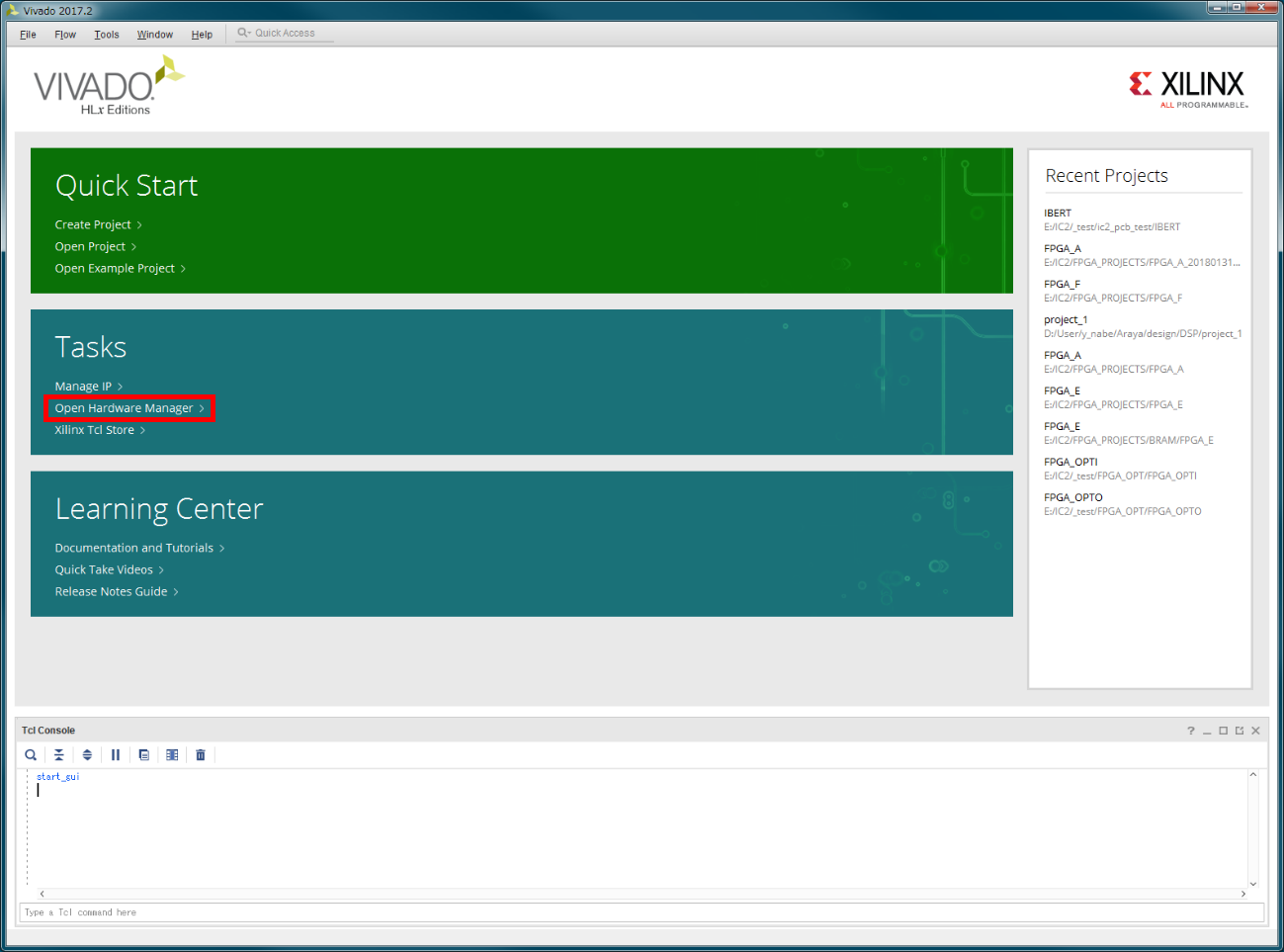

ターゲットとなる基板にJTAGを接続して電源を入れたあとOpen Hardware Managerを選択します。

出典:Vivado® ML Edition

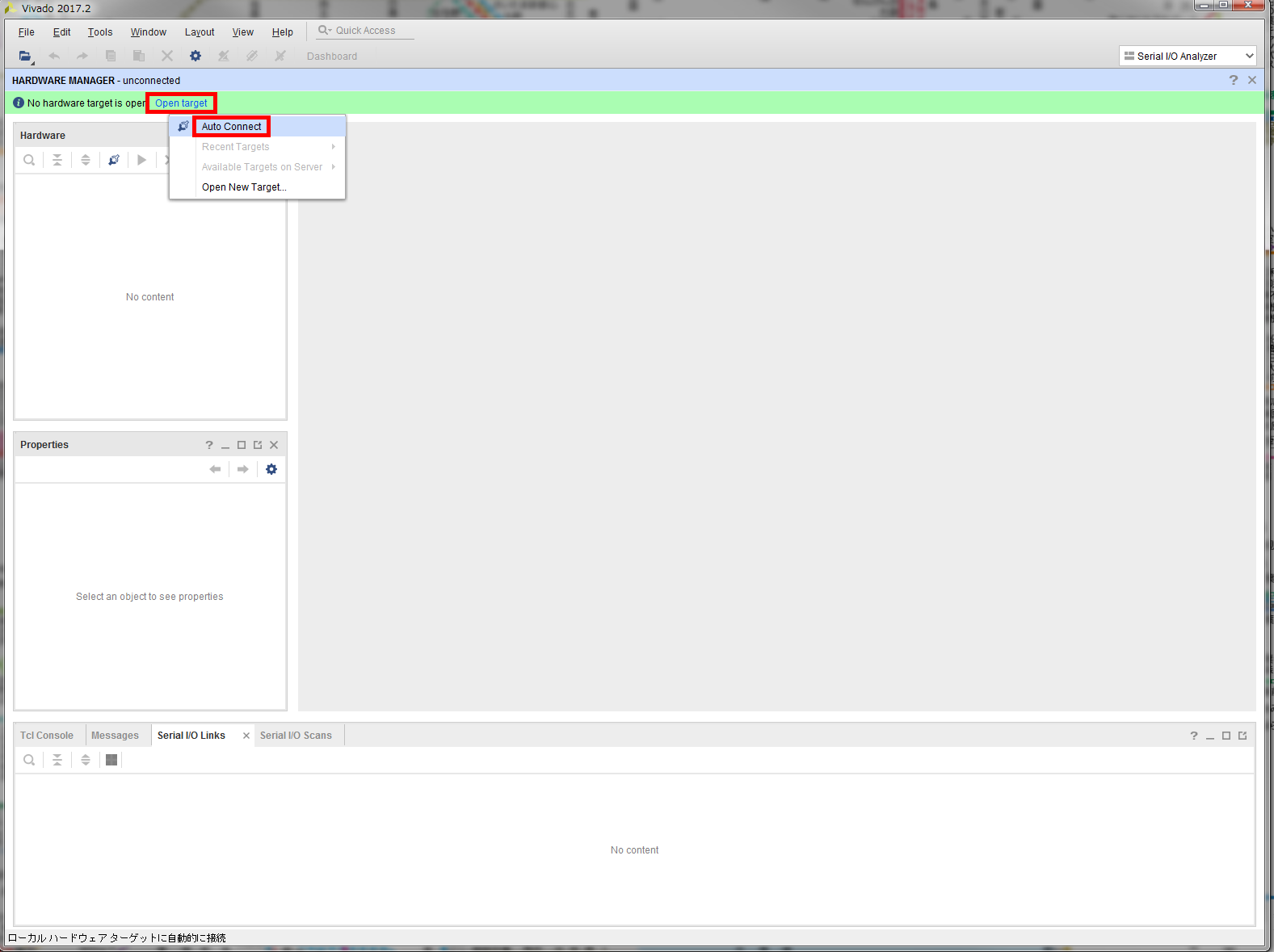

Hardware Managerが開くのでOpen target→Auto Connectを選択します。

出典:Vivado® ML Edition

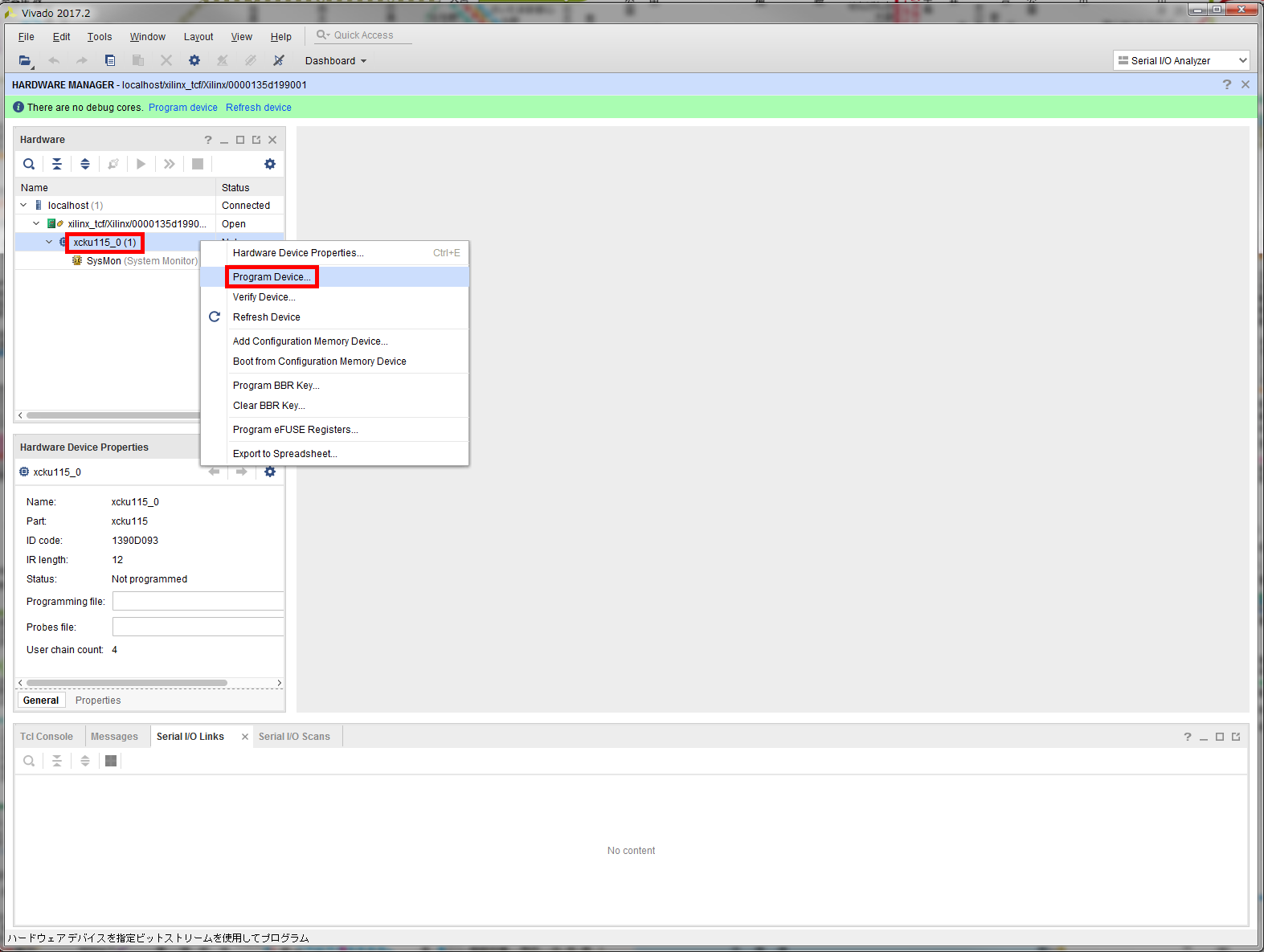

ツリーから対象FPGA(ここではxcku115)を右クリックしてProgram Deviceを選択します。

出典:Vivado® ML Edition

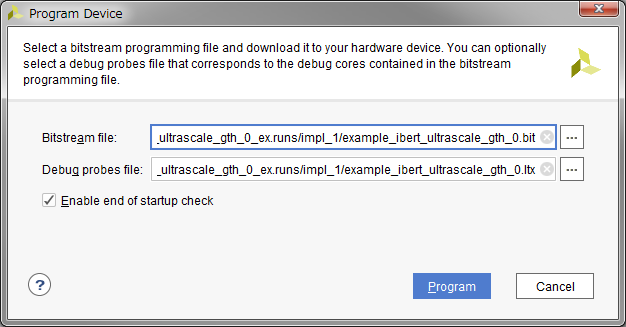

Program Deviceウインドウが開くのでIBERT作成で生成したBitファイルを選択してProgramを実行します。

書き込みファイル

- example_ibert_ultrascale_gth_0.bit

- example_ibert_ultrascale_gth_0.ltx

出典:Vivado® ML Edition

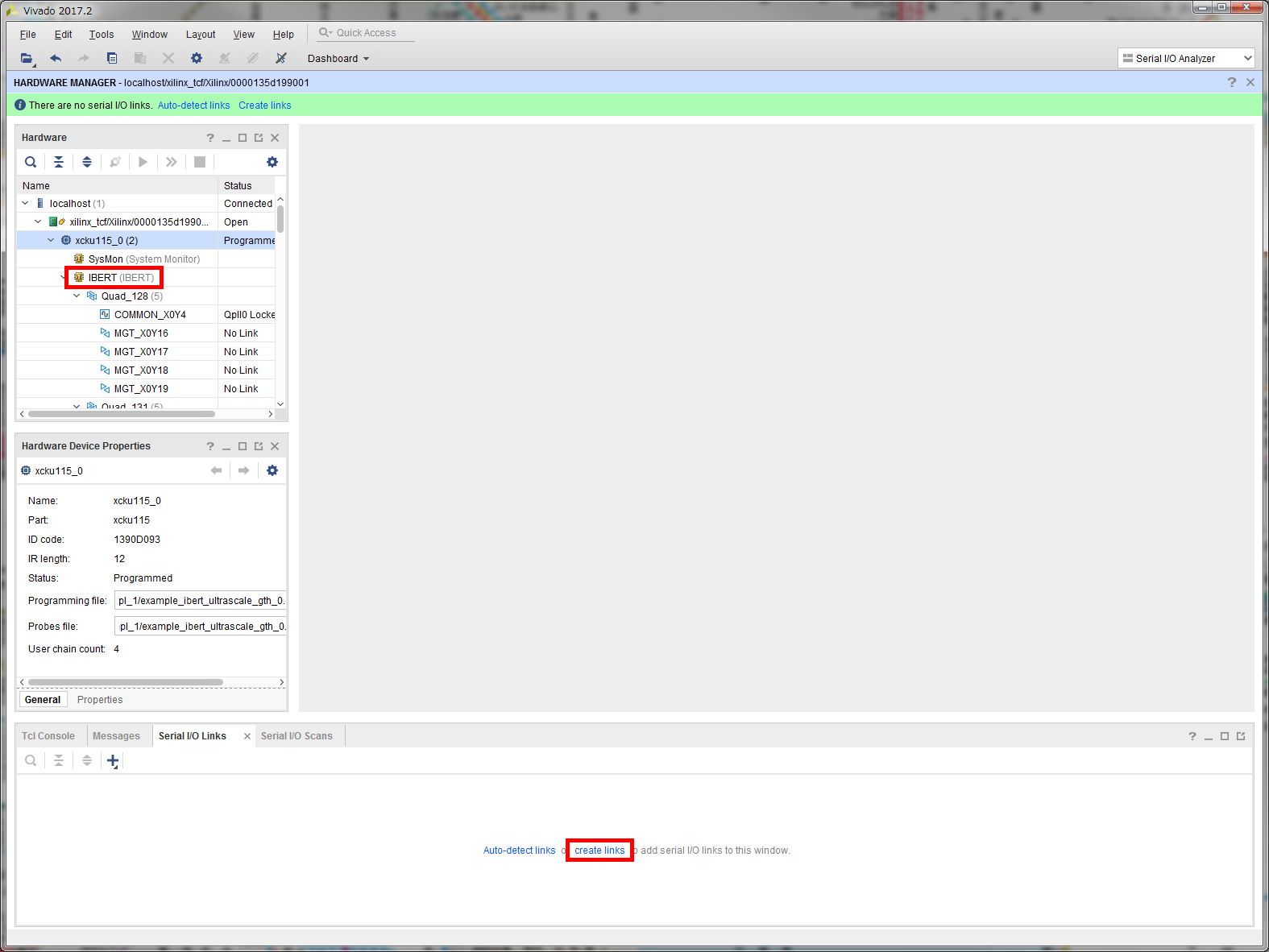

書き込みが完了するとツリー上にIBERTが表示します。

下部のSerial I/O Linksタブでcreate linksを選択します。

出典:Vivado® ML Edition

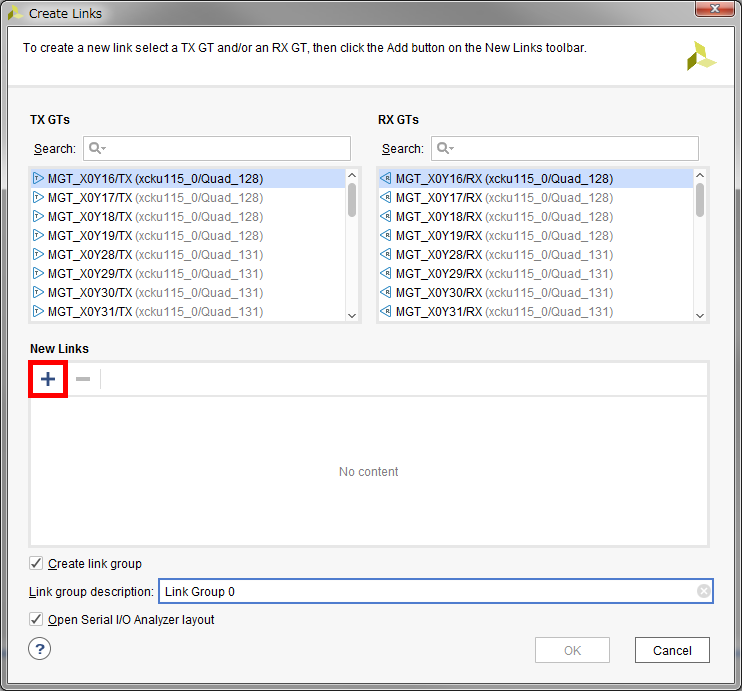

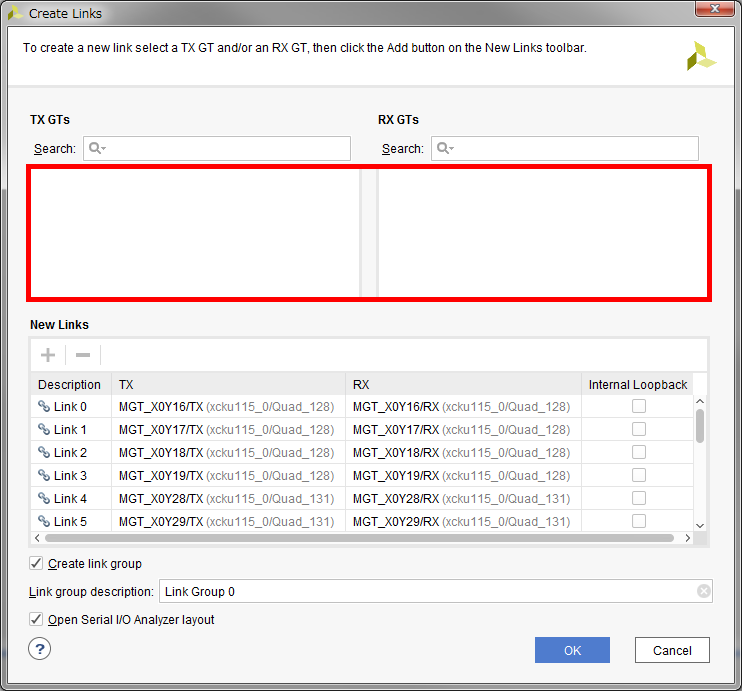

Create Linksウインドウが表示されるので、New Linksの下の+ボタンをLinkパートナーがなくなるまで押します。

出典:Vivado® ML Edition

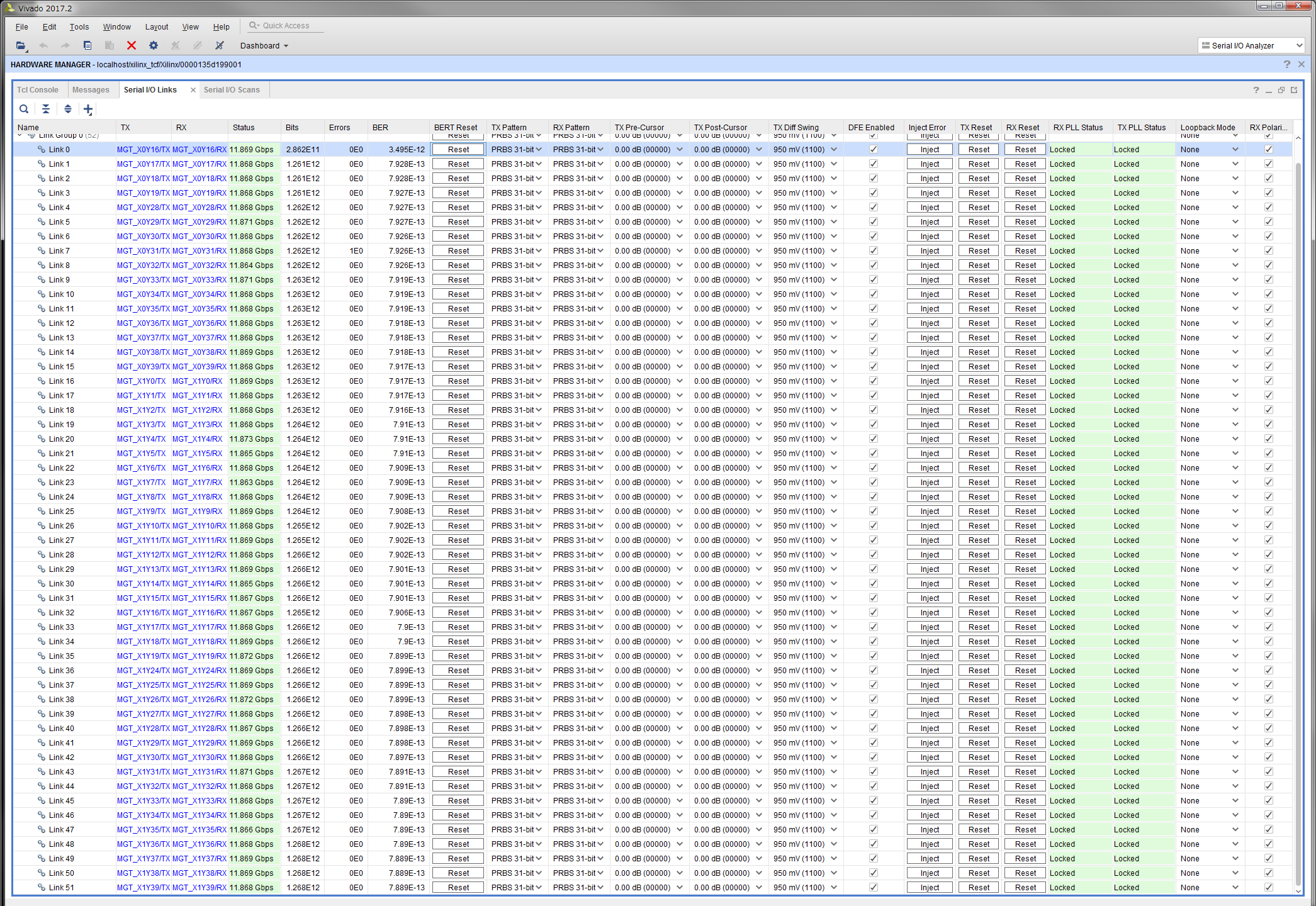

IBERTの画面が表示されてIBERTが使用可能となります。

それぞれのLinkで送受信のパタン、送信エンファシス、受信イコライザ、ループバックなどの設定が可能です。

出典:Vivado® ML Edition

おわりに

今回はIBERTの使い方について紹介をしました。

IBERTを使うことで伝送路の評価が可能になり、不具合の切り分けなどにも使用できるため積極的に活用してみてはいかがでしょうか。

最後までご覧いただきましてありがとうございました。

このブログは「FPGA設計ブログ一覧」の

6. 実機評価のひとつです。