HDL Designerは、世界中のエンジニアやエンジニアリングチームが複雑なFPGAおよびASIC設計を

分析、作成、管理するための強力なHDLベースの統合環境です。

多くのフローとタスクを自動化することで、プロジェクトの生産性を向上させ、エンジニアリング時間を節約します。

HDL Designer概要

HDL Designerは、複雑なFPGAおよびASIC設計を分析、作成、管理するための強力なHDLベースの統合環境です。

多くのフローとタスクを自動化することで、プロジェクトの生産性を向上させ、エンジニアリング時間を節約します。

自動化されたルールチェック、レジスタ生成、様々なグラフィカル・エディタ、およびツール統合によって、設計品質の向上とプロジェクト内で発生するエラーを最小限に抑えることができます。

HDL Designerを使用することで、設計の再利用、コーディングの一貫性、ドキュメンテーションの改善を通じて、自動化によるコスト削減を即座に認識でき、さらに将来のプロジェクトでも継続して使用できます。

HDL Designer機能

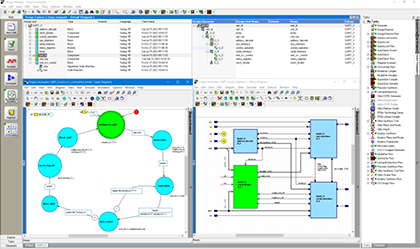

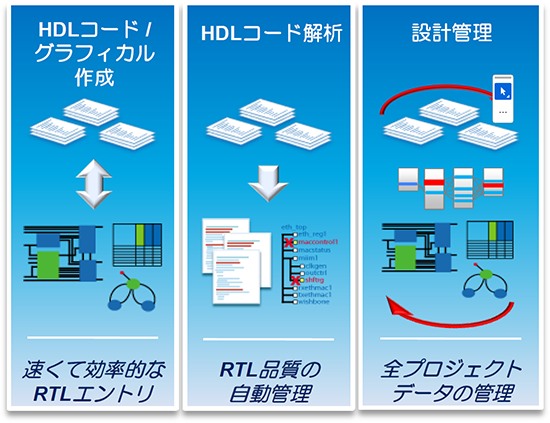

HDLコード/グラフィカル作成

多種のグラフィカル・エディタでRTLをエントリーしHDLコードを生成

サポートされるエディタ:

- グラフィカルエディタ(ブロックダイアグラム、ステートマシン、フローチャート、真理値表)

- 表形式のIBDエディタ(ブロックダイアグラムを等価な表形式に相互変換)

- インテリジェントなテキストエディタ

RTLエントリー用の機能:

- パラメータ化されたライブラリ(ModuleWare)

- 既存モジュールの再利用(コンポーネント化)

- FPGAベンダーツール用のIP生成

既存HDLコードのインポート&グラフィカル変換

- HDLインポート機能によりグラフィカル・エディタ(ブロックダイアグラム、ステートマシン、フローチャート)に変換

- IBDエディタ(ブロックダイアグラムを等価な表形式に相互変換)

HDLコード解析

自動デザインルールチェック

- 内蔵合成エンジンを通じた回路実装違反特定

- デザイン全体へのチェック適用によるモジュール境界を越えた違反特定

- コーディングスタイルルールの適用

- RMMやDO-254ルールセットを含む7つの事前設定されたルールセット

- パラメータ化可能なチェックによるカスタマイズされたルールセットとポリシーの作成機能

- デザインチェックレポートによる品質指標と違反結果の要約

設計管理

ドキュメント作成

- OLE、プリント、グラフィックスのエクスポート機能

- HTMLプロジェクトスナップショット機能

- HDLコードとグラフィカルソースビューの相互参照

プロジェクト管理とチームベースの設計

- 設計フロー全体を通じてプロジェクトとチームの管理を自動化および簡素化

- フロー内の他の設計ツール(ReqTracer、Questa/ModelSim、Precision、FPGAベンダーツールなど)へのインターフェイスを提供

- 自動コンパイル、シミュレーション、ツールの呼び出し機能

- 簡素化されたバージョン管理システムインターフェイス(Subversion、IBM® ClearCase、CVS、Git™/Git LFSをサポート)

設計保証コンプライアンス支援

- バージョン管理機能

- レジスタ自動化機能

- デザインチェック機能

- DO-254やISO 26262などのセーフティクリティカルへの設計支援

HDL Designer特長

構造化されたFPGA/ASICデザインフローを確保

一貫性のある設計プロセスを通じて、品質の高い成果物を実現します。

上流および下流ツールとの体系的なフローを提供

設計プロセス全体を通して一貫したツールチェーンを構築できます。

HDL記述の自動化とHDLからの自動グラフィカル生成

コーディング時間を短縮し、設計の視覚的理解を促進します。

柔軟なデザインチェックによる一貫したRTLコーディングをサポート

開発サイクルの早い段階(シミュレーション、合成、配置配線前)で設計の欠陥を特定できます。

SWおよびHWのアドレス指定可能なレジスタの一貫性を保証

設計エラーを減少させ、ハードウェア/ソフトウェアの統合を簡素化します。

デザイン再利用を促進

既存のHDLコードをインポートし、現在のプロジェクトに迅速に組み込むことができます。

HDLコードのグラフィカル化とHTMLスナップショット

迅速かつ簡単にドキュメントを作成し、デザインレビューの準備時間とドキュメント作成の労力を削減します。

安全基準への準拠を満たす自動デザインチェックを搭載

民間航空機、自動車エレクトロニクス、医療機器などの設計分野に必要な安全基準を確実に満たすための設計プロセスをサポートします。

チーム間での一貫性確保

チームは同じ設定、ツール、ツールバージョン、コーディングテンプレート、およびタスクを使用して、反復的なフローを自動化できます。

柔軟なプロジェクトインポートとAPI

既存の設計プロセスに簡単に適合し、カスタム設計フローを構築できます。

動作環境

- Windows 10 / 11

- Linux RHEL 7 / 8

HDL Designerのデータシートダウンロードはこちら

シーメンス EDAのことなら

PALTEKにご相談ください!