株式会社PALTEK > デザインサービス事業

デザインサービス事業

受託サービス

設計受託・ODM

仕様設計から量産製造まで、一貫したデザインサービスを提供します。

モデルベースデザイン設計受託

開発工程からテスト工程までを一貫して受託することで、V字プロセスに則ったモデルベース設計・検証フローを実現します。

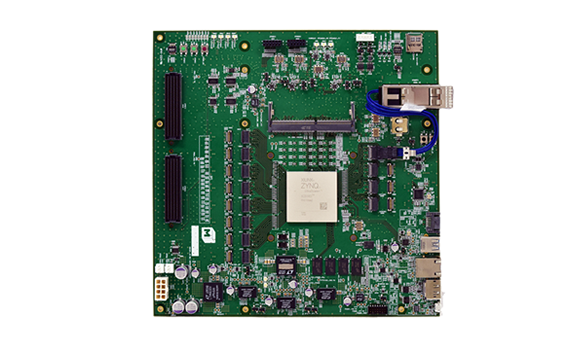

設計事例・保有技術

PALTEKがこれまで行ってきたハードウェア設計、ソフトウェア設計、システム設計の事例や、代表的な保有技術について紹介します。

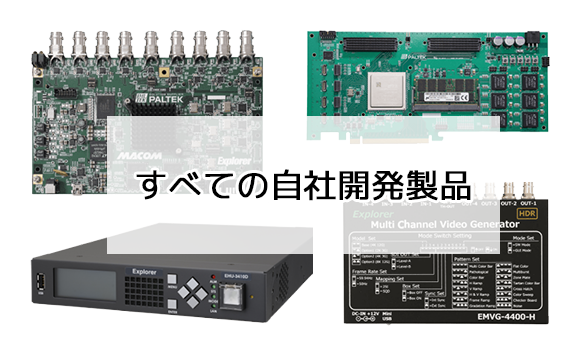

自社開発製品

PALTEKグループでは、培ってきた設計技術や設計ノウハウなどの技術資産をベースに、オリジナル製品を開発しています。

TECHブログ(設計)

製品・サービスに関する

ご相談・ご質問は

お気軽にどうぞ。