【回路設計ヒント】どうする?FPGAの端子アサイン ~インタフェース編~

皆さん、こんにちは。FPGAの端子アサインはどうやって決めていますか?

FPGA設計者が主体で決めている、回路 (基板)設計者が主体で決めている、FPGAも回路も一人で両方行っている、等々あると思います。

一人で両方を行っている場合には臨機応変に修正対応が行えそうですが、分業にしている場合には

FPGA設計者が決めている場合は「パターンの引き回しが考慮されない」

回路設計者が決めている場合は「FPGAの機能や仕組みが考慮されない」

といった問題が起きることがあるかと思います。

中でも一番困るのが、基板は出来上がったのに端子アサインが原因でVivado™やISE™がエラーで通らず、実機が動かせなかったり、基板が作り直しになったりする場合ですね。

そこで、FPGAを使い始めた方やFPGA内部をあまりご存じない方に向けて、FPGAの端子アサインに関するヒントをあげて行きたいと思います。

それでは、はじめましょう。

目次

ここで掲載している図表は例としてあげています。

全てのデバイスシリーズにはあてはまるわけではありません。

必ずご使用になるデバイスシリーズのデータシートで内容をご確認ください

インタフェース

端子にはSerDesやI/O Delayなど様々なインタフェースに対応するための機能が備わっています。

その代表がDDRメモリ(MIG)・LVDS・MIPI D-PHY・PCIeと言えます。

※ MIG = Memory Interface Generator

DDRメモリ・LVDS・MIPI D-PHY・PCIeなどのインタフェースを実装する際には、端子のオプション設定だけではなく端子近くにあるインタフェース関連のハードマクロを組み合わせることになるため、かなり複雑なルールをクリアする必要があります。

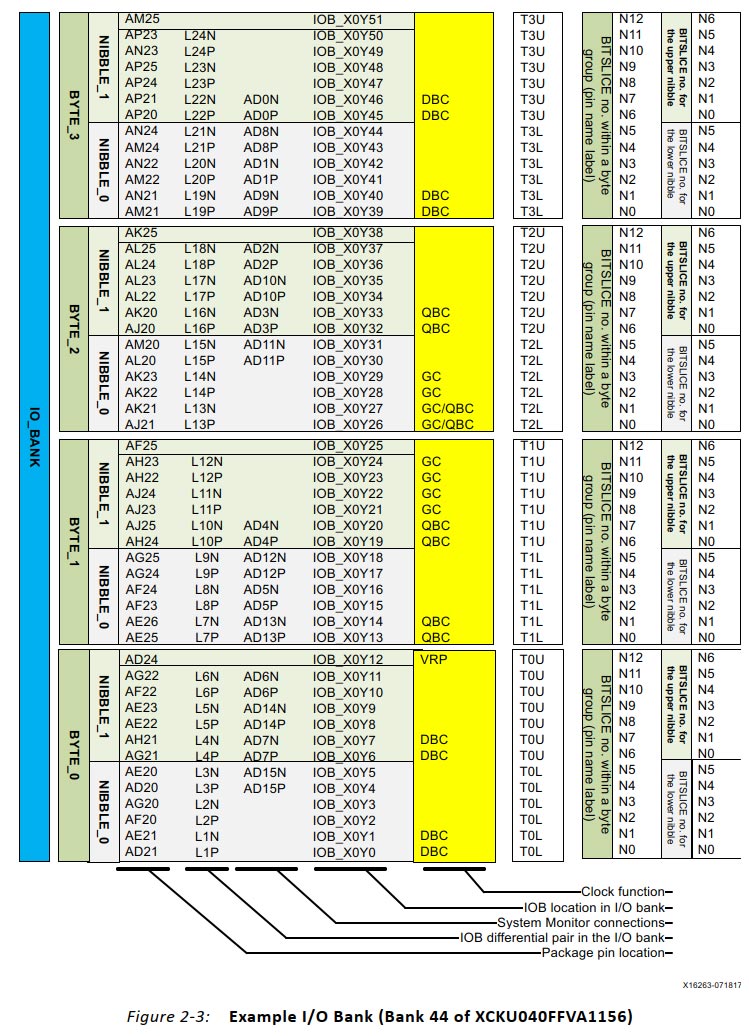

UltraScale+シリーズのDDRメモリの場合、端子部分だけ書き出しても接続関係は次の図のように

「ストローブのDQSペアはQBC/DBC(バイトクロック)に接続し、データのDQはそのDQSが所属するQBC/DBCのバイトもしくはニブルグループに接続する」

となります。

出典:

UG571 UltraScale Architecture SelectIO Resources User Guide <P.149>(参照 2026/04/17)

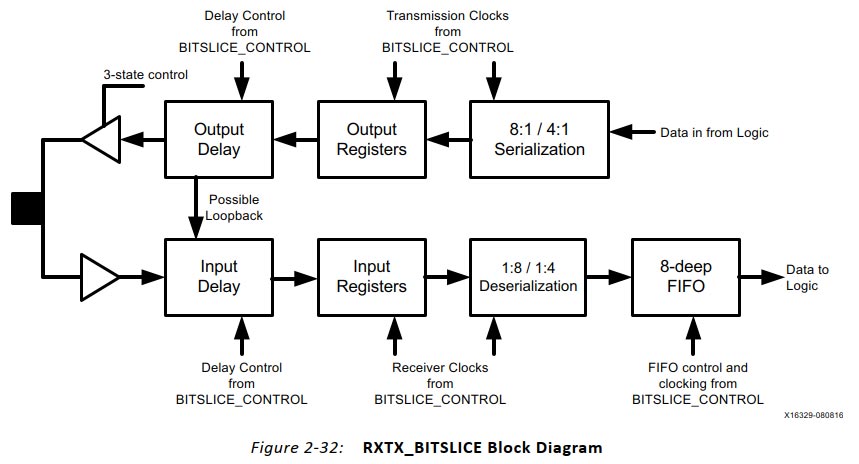

更にBITSLICEと呼ばれる場所にある、SerDesやI/O Delayなどのハードマクロにも接続するため、それらのルールもクリアする必要があります。

そのため、データシートを見て全てのルールを把握できるかわかりません。

参考までに、BITSLICEの中を簡易的に現すとこのようなハードマクロが存在しています。

出典:

UG571 UltraScale Architecture SelectIO Resources User Guide <P.199>(参照 2026/04/17)

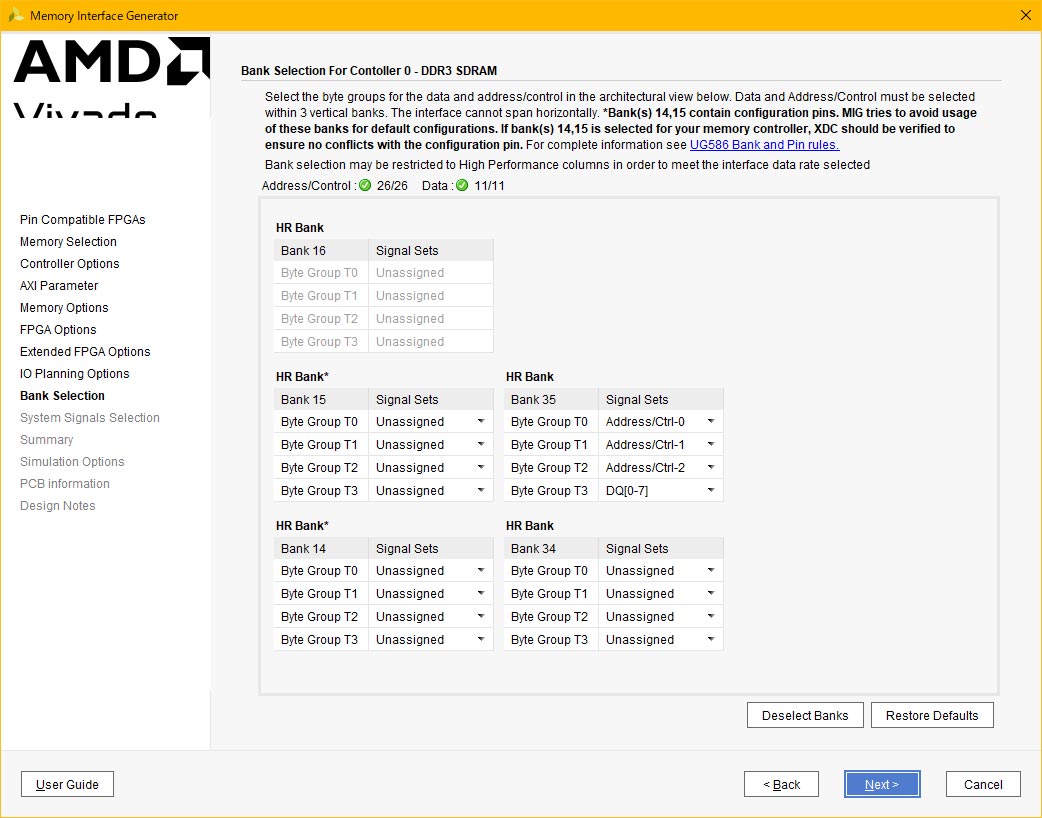

このようなインタフェースの場合IPが用意されており、ウイザードで端子の指定や確認ができるものがあります。

もし、パターン都合でピンスワップを行う場合には、スワップした内容で再度IPを作るか、ウイザード内でルール確認ができる場合にはそこで確認を行います。

MIGで新規に端子アサインを行うときのウイザード画面

出典:

VIVADO™ 2023.1 Memory Interface Generator (Ver 4.2) IP 設定画面(参照 2024/03/06)

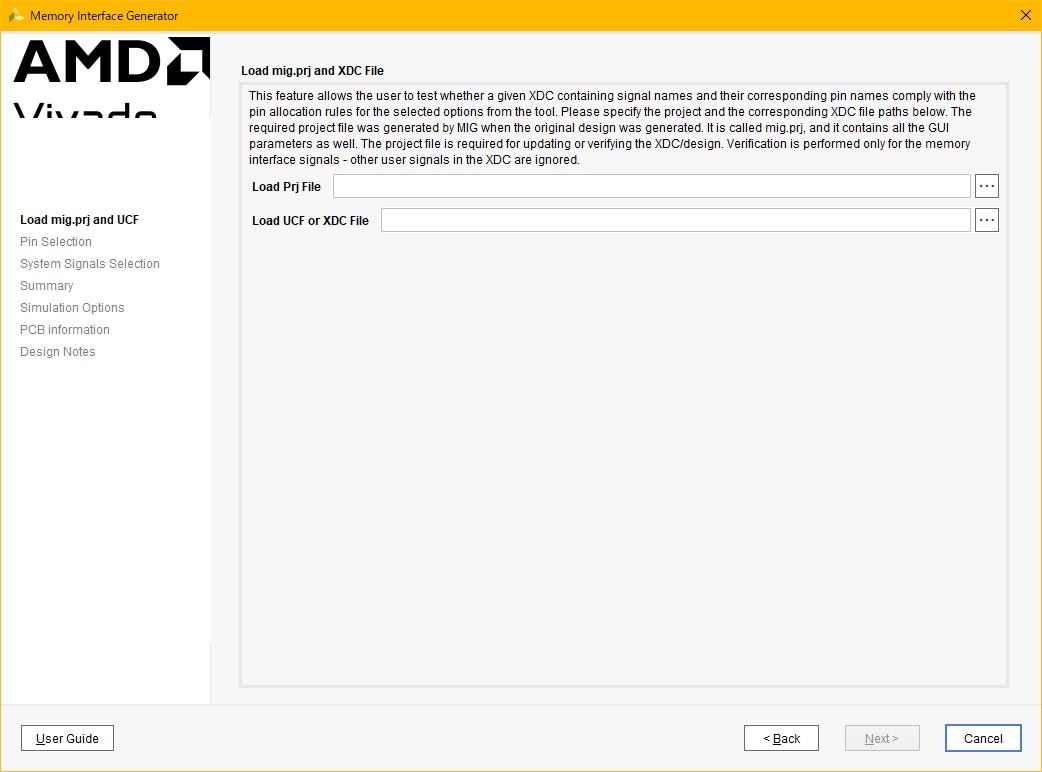

修正した端子アサインをMIGで確認を行うときのウイザード画面 ※確認を行うにはアサインを修正した設定ファイル(*.XDC/*.UCF)が必要になります

出典:

VIVADO™ 2023.1 Memory Interface Generator (Ver 4.2) IP 設定画面(参照 2024/03/06)

LVDSなど一部のインタフェースはリファレンスデザインが用意されている場合があります。

これを利用して仮デザインを作成し、端子とハードマクロ等との接続ルールを確認しましょう。

確認

IPでリファレンスデザインがある場合にはこれを利用して、インターフェースでリファレンスデザインが用意されている場合はそれを利用して今回使用する形にします。

内部ロジックが削除されないようにして、Vivado™やISE™でインプリを行うのが良いでしょう。

warning の確認も必要ですが必ず「Generate Bitstream」まで行ってください。

論理合成・配置配線ができていても最後の「Generate Bitstream」でルール違反が判明しエラーが出ることがあります。

まとめ

- ウイザードで端子アサインを行うものはウイザードの内容に従い、そうでないものは仮デザインをインプリしてルールを確認しましょう。

いかがでしたか?

このように、端子アサインに関連して色々と条件がありますので、FPGAでの実現性確認と、基板設計での最適化とを繰り返して端子を決めてゆくことが良いと思います。

最後までご覧いただきましてありがとうございました!

これからもTECHブログを通じて、皆様の設計にお役立てできればと思います。

次回のブログもどうぞよろしくお願いいたします。

弊社ではFPGA設計や回路図設計、レイアウト設計、ソフトウェア設計、筐体設計などを受託開発しています。

サービス内容をWEBサイトに掲載していますので、ぜひご覧ください。

FPGAの活用に際して設計検討などありましたら、お気軽にお問い合わせください。