【回路設計ヒント】トランシーバのリファレンスクロックをユーザークロックとして使用する方法

みなさん、こんにちは。

今回はトランシーバのクロック入力端子(MGTREFCLK)に接続されているクロックを、ユーザークロックとして使用する方法を説明します。

本ブログはAMD ザイリンクス社のUltraScale™ アーキテクチャ をベースに執筆しています。

それでは、始めましょう。

このブログは「FPGA設計ブログ一覧」の

1. コーディング・IP設定・プリミティブ設定 のひとつです。

目次

ユーザークロックへの分離方法

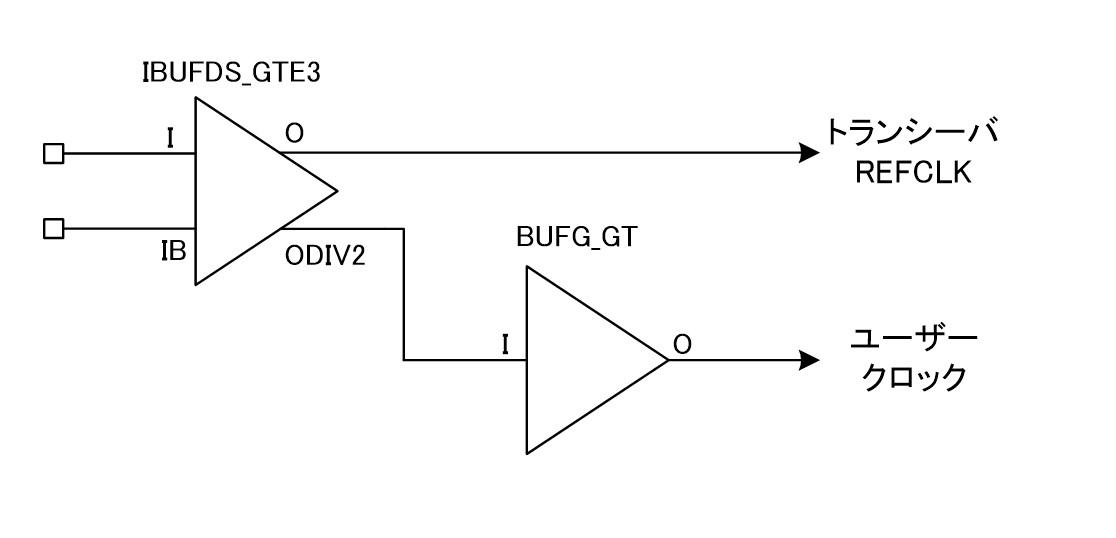

端子から入力されたクロックをIBUFDS_GTE3に入力して、O側はトランシーバへ接続、ODIV2側はBUFG_GTを介すことでユーザークロックとして使用することが可能です。

注意点としてはトランシーバウィザードを使用して出力した場合、IBUFDS_GTE3はトランシーバウィザードが出力した周辺回路のRTLに含まれてしまっています。

そのため、出力されたRTLを書き換える必要があります。

図1. ユーザークロックへの分離方法

Verilogでの記述方法

以下にVerilogでのサンプルコードを記載します。

module REFCLK_USER (

input wire RSTP , // Act-H Reset

input wire MGTREFCLK_P , // MGTREFCLK P

input wire MGTREFCLK_N , // MGTREFCLK N

output wire REFCLK , // Clock for GT

output wire REFCLK_USER // Clock for User

);

wire gtrefclk_user;

IBUFDS_GTE3 #(

.REFCLK_HROW_CK_SEL(2'b00)

) IBUFDS_GTE3 (

.I ( MGTREFCLK_P ),

.IB ( MGTREFCLK_N ),

.CEB ( 1'b0 ),

.O ( REFCLK ),

.ODIV2 ( gtrefclk_user )

);

BUFG_GT BUFG_GT (

.O ( REFCLK_USER ), // 1-bit output: Buffer

.CE (~RSTP ), // 1-bit input: Buffer enable

.CEMASK ( 1'b0 ), // 1-bit input: CE Mask

.CLR ( RSTP ), // 1-bit input: Asynchronous clear

.CLRMASK ( 1'b0 ), // 1-bit input: CLR Mask

.DIV ( 3'b000 ), // 3-bit input: Dynamic divide Value

.I ( gtrefclk_user ) // 1-bit input: Buffer

);

endmodule

パラメータ設定

サンプルコード内の以下のパラメータにより、ユーザークロックを分周して出力することが可能です。

IBUFDS_GTE3

- REFCLK_HROW_CK_SEL[1:0]

|

2’b00 : ODIV2を出力 2’b01 : ODIV2を2分周したクロックで出力 2’b10 : ODIV2を0固定 2’b11 : 予約 |

BUFG_GT

- DIV[2:0]

|

設定した値でO(出力)の分周率を決定 DIVの値+1で分周される 3’b000 : ÷1 3’b001 : ÷2 3’b010 : ÷3 ︙ 3’b110 : ÷7 3’b111 : ÷8 |

おわりに

いかがでしたでしょうか。

トランシーバのリファレンスクロックをユーザークロックとして使用する方法をご理解いただけますと幸いです。

最後までご覧いただきありがとうございました。

このブログは「FPGA設計ブログ一覧」の

1. コーディング・IP設定・プリミティブ設定 のひとつです。