【回路設計ヒント】Spartan®-6 FPGA ファミリから Spartan®-7 FPGA ファミリへの置き換え ~I/O編~

みなさんこんにちは。世界的な半導体の供給不足等で設計開発に影響が出ていて、 AMD ザイリンクス社のSpartan®-6 FPGAファミリから Spartan®-7 FPGAファミリへの置き換えの需要が高まってきています。

そこで5回にわたって、回路設計の観点で置き換え時のポイントをお伝えしていきたいと思います。

今回はI/Oに着目します。

※引用した参考資料のページ数はバージョンにより異なる場合がございますので、予めご承知おきください

それでは始めましょう。

このブログは「FPGA設計ブログ一覧」の

Spartan®-6 FPGAファミリの置換 の

ひとつです。

目次

はじめに

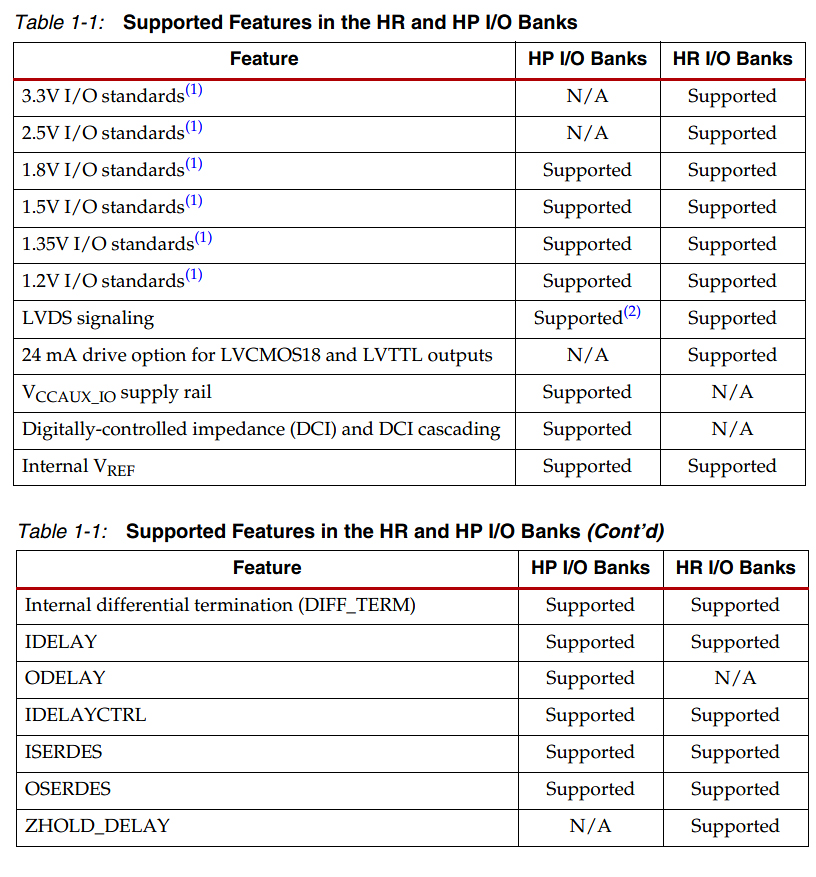

7シリーズのI/Oは、3.3Vや2.5V I/Oが使用できるHigh-Range (HR) I/Oと、1.8V以下の高速なI/Oが使用できるHigh-Performance (HP) I/O の2種類存在しますが、Spartan®-7は全BANKがHR となっています。

パッケージ

Spartan®-6 とSpartan®-7 、似たようなピン数やパッケージが存在していますが、互換はありません。

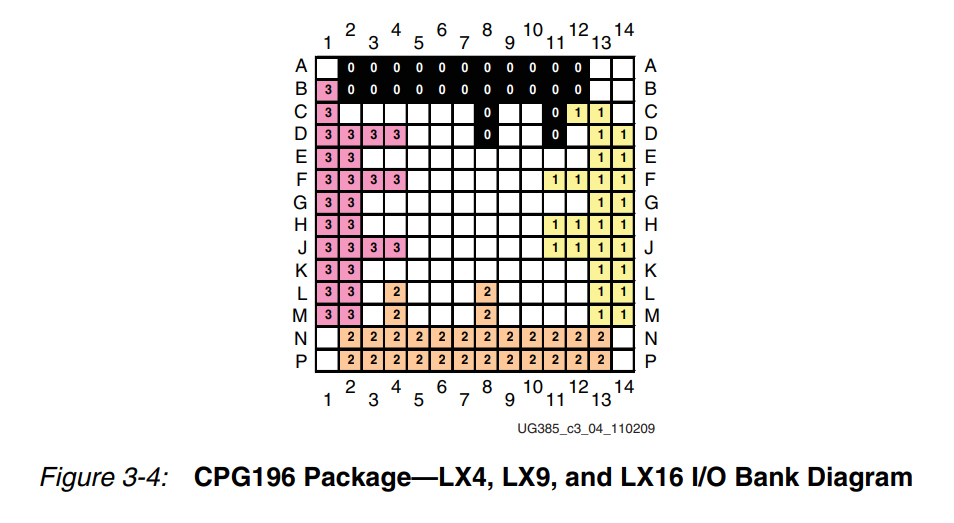

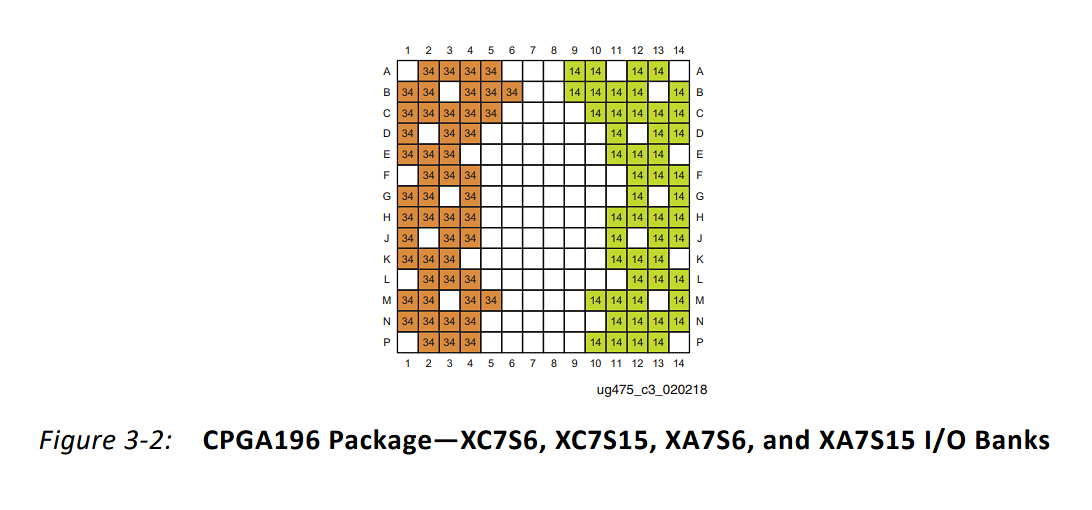

以下は似ているパッケージ、CPG196とCPGA196 のユーザーIOの状況を示した図です。そのため、回路シンボルの作り直しや端子アサインの仕直しが必須となります。

※画像クリックで大きな画像が表示されます。

出典:UG385 (v2.4) Spartan-6 FPGA Packaging and Pinouts Product Specification <P.276>

https://docs.amd.com/v/u/en-US/ug385 (参照 2022/6/1)

出典:UG475 (v1.19) 7 Series FPGAs Packaging and Pinout Product Specifications User Guide <P.75>

https://docs.amd.com/v/u/en-US/ug475_7Series_Pkg_Pinout (参照 2022/6/1)

なお、Spartan®-7にはトランシーバ搭載品がないため、Artix®-7 など他のFPGAをご選択いただくか、トランシーバICが別途必要になります。

I/O特性

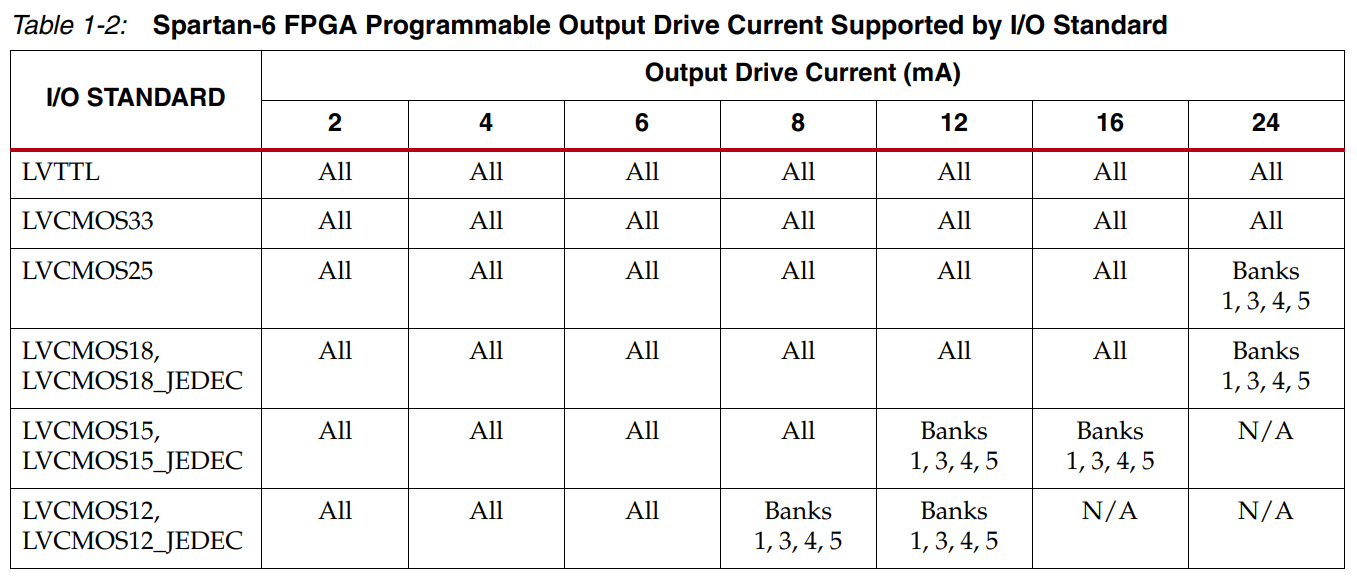

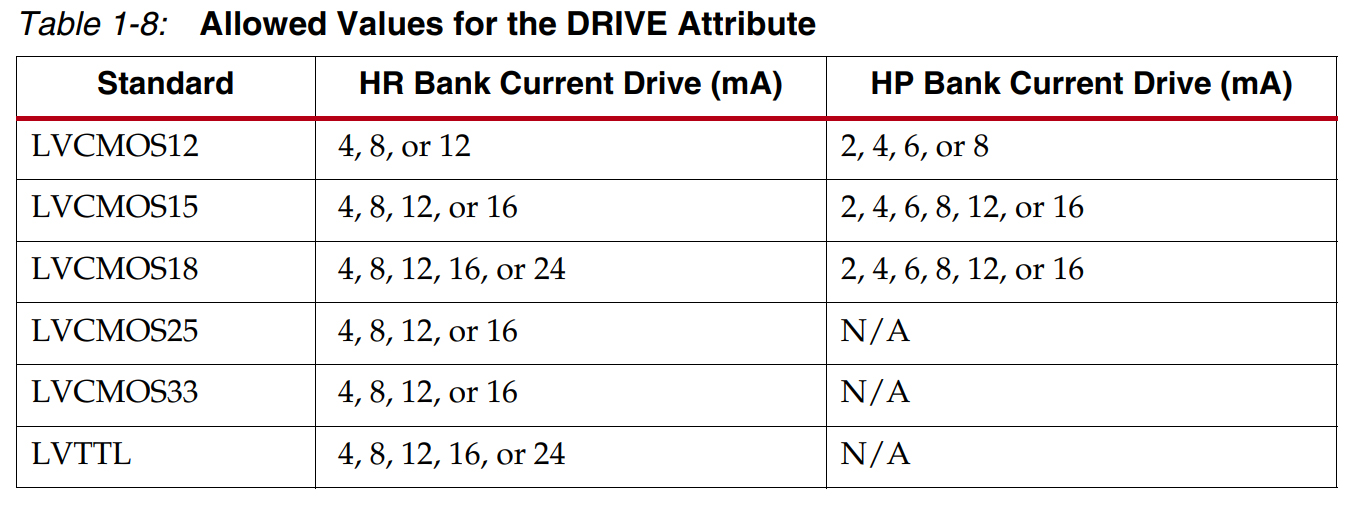

LVCMOSの2.5Vと3.3VのDrive Current 24mAがサポートされなくなっており、全体的に2mA・6mAがサポートされなくなっています。

※画像クリックで大きな画像が表示されます。

出典:UG381 (v1.7) Spartan-6 FPGA SelectIO Resources User Guide <P.31>

https://docs.amd.com/v/u/en-US/ug381 (参照 2022/6/2)

出典:UG471 (v1.10) 7 Series FPGAs SelectIO Resources User Guide <P.48>

https://docs.amd.com/v/u/en-US/ug471_7Series_SelectIO (参照 2022/6/2)

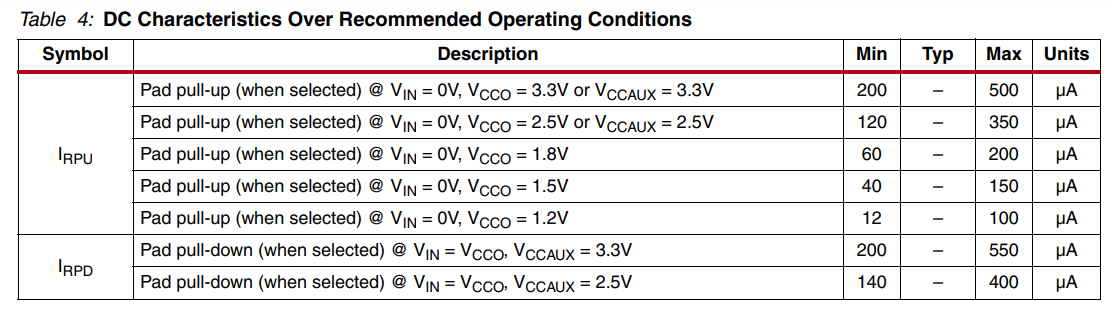

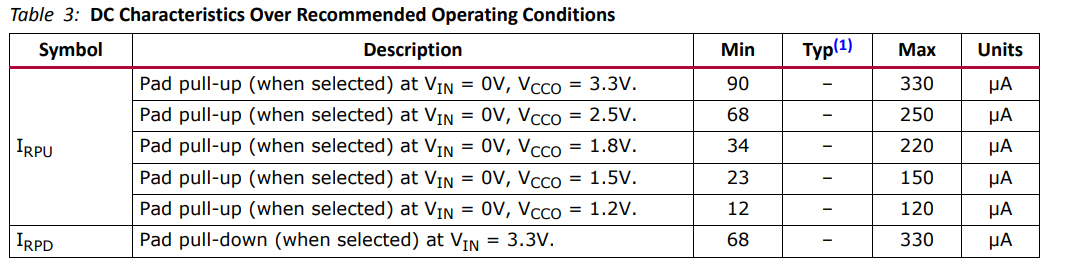

また、内部Pull-UP/DOWN で流せる電流値(抵抗値)が変更になっています。

※画像クリックで大きな画像が表示されます。

出典:DS162 (v3.1.1) Spartan-6 FPGA Data Sheet: DC and Switching Characteristics <P.5>

https://docs.amd.com/v/u/en-US/ds162 (参照 2022/6/2)

出典:DS189 (v1.9) Spartan-7 FPGAs Data Sheet : DC and AC Switching Characteristics <P.4>

https://docs.amd.com/v/u/en-US/ds189-spartan-7-data-sheet (参照 2022/6/2)

省電力機能

Spartan®-7にはSpartan®-6 でサポートされていた省電力機能がないため、関連端子の「SUSPEND,AWAKE,SCPn」はSpartan®-7 には存在しません。

I/O Standard

使用できる基本的なI/O Standardは変わりありませんが、 念のため [UG471] 7 Series FPGAs SelectIO Resources User Guideで同じものが使用できるかご確認ください。

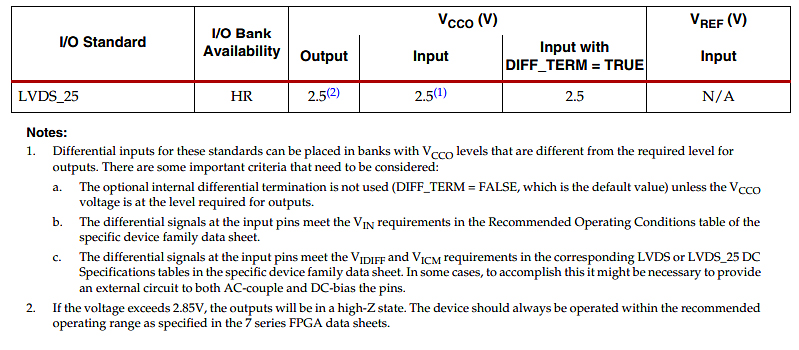

特に、Spartan®-6 で使えていたLVDS_33・MINI_LVDS_33が Spartan®-7では使用できませんのでご注意ください。

出典:UG471 (v1.10) 7 Series FPGAs SelectIO Resources User Guide <P.13~14>

https://docs.amd.com/v/u/en-US/ug471_7Series_SelectIO (参照 2022/6/9)

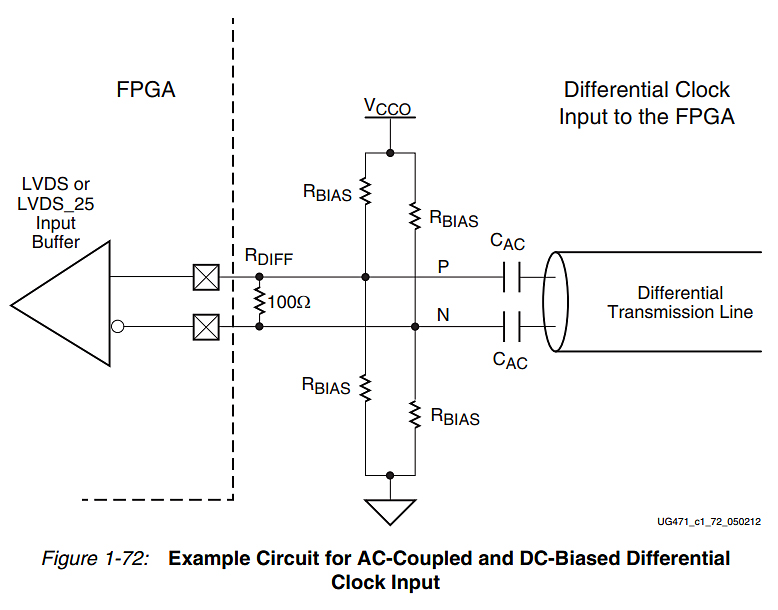

そのかわり差動入力のLVDS_25は、 出力の要求レベルと異なるVCCO レベルのバンクでも配置できますが、次のことに注意してください。

- 内部差動終端は使用できないため、基板上に終端を置きます

- VIN 要件を満たしている必要があります

- LVDS_25 のVIDIFF とVICM の要件を満たすように、ACカップリングやDCバイアスするための外部回路が必要になります

※画像クリックで大きな画像が表示されます。

出典:UG471 (v1.10) 7 Series FPGAs SelectIO Resources User Guide <P.98~100><P.93>

https://docs.amd.com/v/u/en-US/ug471_7Series_SelectIO (参照 2022/6/9)

I/O のオプション

7シリーズのHR BANKはODELAY とDCI がサポートされていません。

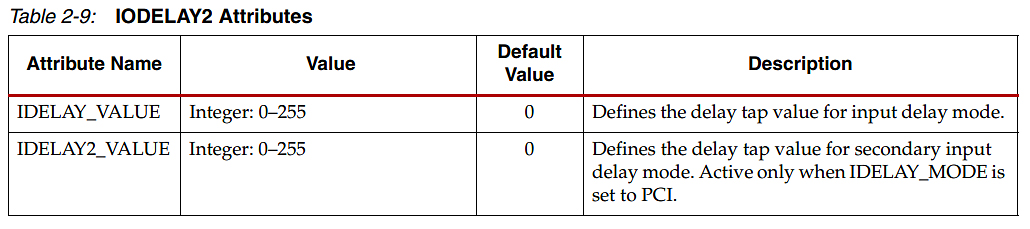

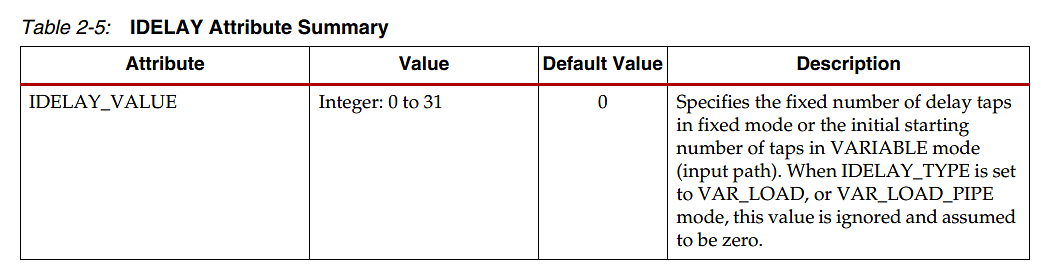

IDELAYはSpartan®-7でも使用できますが、Spartan®-6 と精度やTAP数が変わっていますので、接続先との関係が希望する調整範囲にあるかお確かめください。

※画像クリックで大きな画像が表示されます。

出典:UG381 (v1.7) Spartan-6 FPGA SelectIO Resources User Guide <P.74>

https://docs.amd.com/v/u/en-US/ug381 (参照 2022/6/9)

出典:UG471 (v1.10) 7 Series FPGAs SelectIO Resources User Guide <P.119>

https://docs.amd.com/v/u/en-US/ug471_7Series_SelectIO (参照 2022/6/9)

※画像クリックで大きな画像が表示されます。

出典:DS189 (v1.9) Spartan-7 FPGAs Data Sheet : DC and AC Switching Characteristics <P.28>

https://docs.amd.com/v/u/en-US/ds189-spartan-7-data-sheet (参照 2022/6/9)

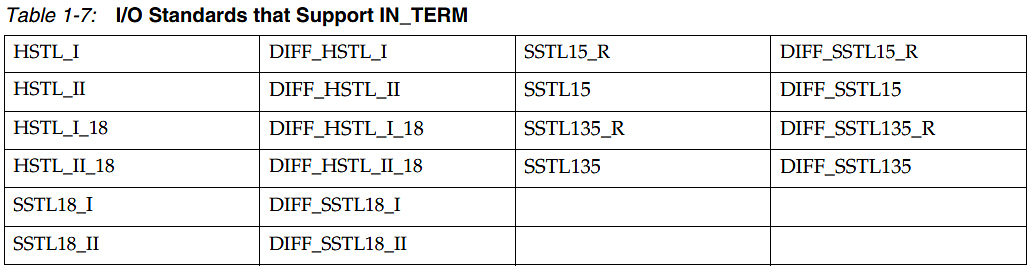

DCIの代わりに補正のない内部抵抗(IN_TERM)で終端を行うことができます。

選べるテブナン等価抵抗値は40Ω/50Ω/60Ωで、以下のI/O Standardで使用することができます。

※画像クリックで大きな画像が表示されます。

出典:UG471 (v1.10) 7 Series FPGAs SelectIO Resources User Guide <P.33>

https://docs.amd.com/v/u/en-US/ug471_7Series_SelectIO (参照 2022/6/9)

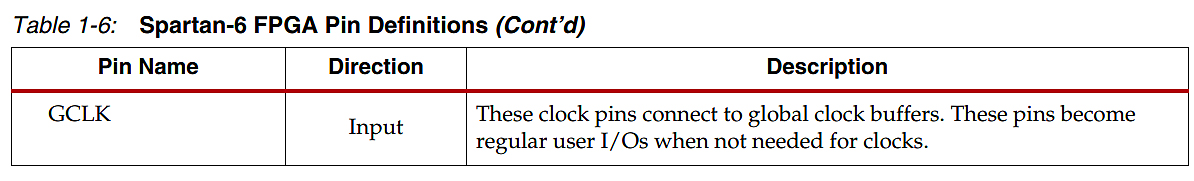

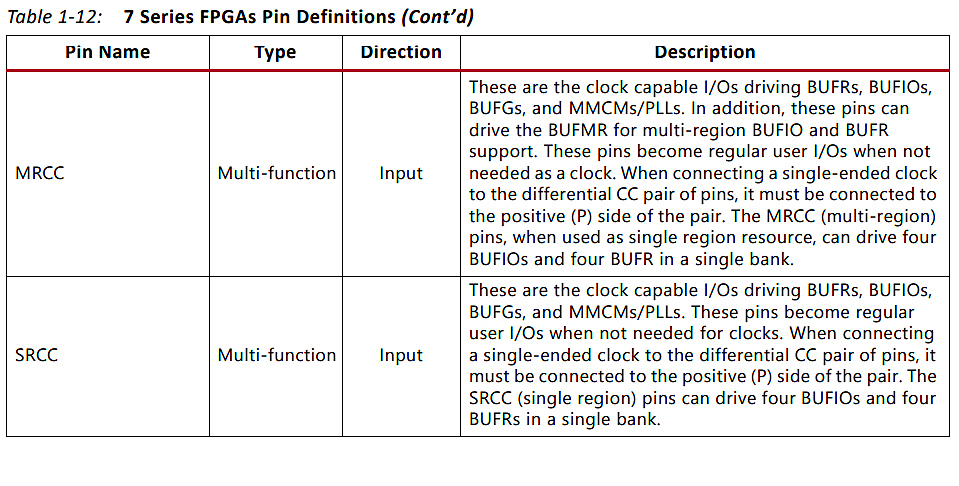

クロック入力

Spartan®-6 ではクロック入力対応端子は「GCLK」でしたが、Spartan®-7 では「MRCC」または「SRCC」と変更され細かい内部の機能も変わってきています。 グローバルクロックの入力として使用する場合はMRCC/SRCCどちらに接続しても構いません。ただし、[UG475]の説明でも書かれている通り、シングルエンドのクロック信号はMRCC/SRCC端子のPch側に接続してください。

※画像クリックで大きな画像が表示されます。

出典:UG385 (v2.4) Spartan-6 FPGA Packaging and Pinouts Product Specification <P.20>

https://docs.amd.com/v/u/en-US/ug385 (参照 2022/6/9)

出典:UG475 (v1.19) 7 Series FPGAs Packaging and Pinout Product Specifications User Guide <P.31~32>

https://docs.amd.com/v/u/en-US/ug475_7Series_Pkg_Pinout (参照 2022/6/9)

クロックの接続についてはVivado® Design Suiteで元デザインのインプリを行い、 クロック入力が問題なくMRCC/SRCC端子にアサインできること、動作周波数が選択したデバイスで使用できる範囲内であることをご確認ください。

まとめ

- ・パッケージの互換性はなし

- ・I/Oの特性が変わる

- ・LVDS_33・ODELAY・DCIは使えなくなる

- ・クロック入力対応の端子名が変更になる

- ・シングルクロックはPchに接続する

いかがでしたでしょうか。今回は以上となります。

次回はコンフィグレーションに着目します。最後までお付き合いいただきありがとうございました。

このブログは「FPGA設計ブログ一覧」の

Spartan®-6 FPGAファミリの置換 の

ひとつです。