FPGAの置換(Spartan®-6 FPGA ファミリ)第6回(置換可能なデバイス選定:メモリインタフェース編)

世界的な半導体の供給不足等で設計開発に影響が出ています。

AMD ザイリンクス社でも、Spartan®-6 FPGA ファミリの入手が困難になっています。

そこで、置換可能なデバイス選定について解説します。

FPGAの置換シリーズ最終回(6回目)となる今回は、デバイス置換することにより影響するメモリ選定、インタフェース部について記載します。

このブログは「FPGA設計ブログ一覧」の

Spartan®-6 FPGAファミリの置換 の

ひとつです。

目次

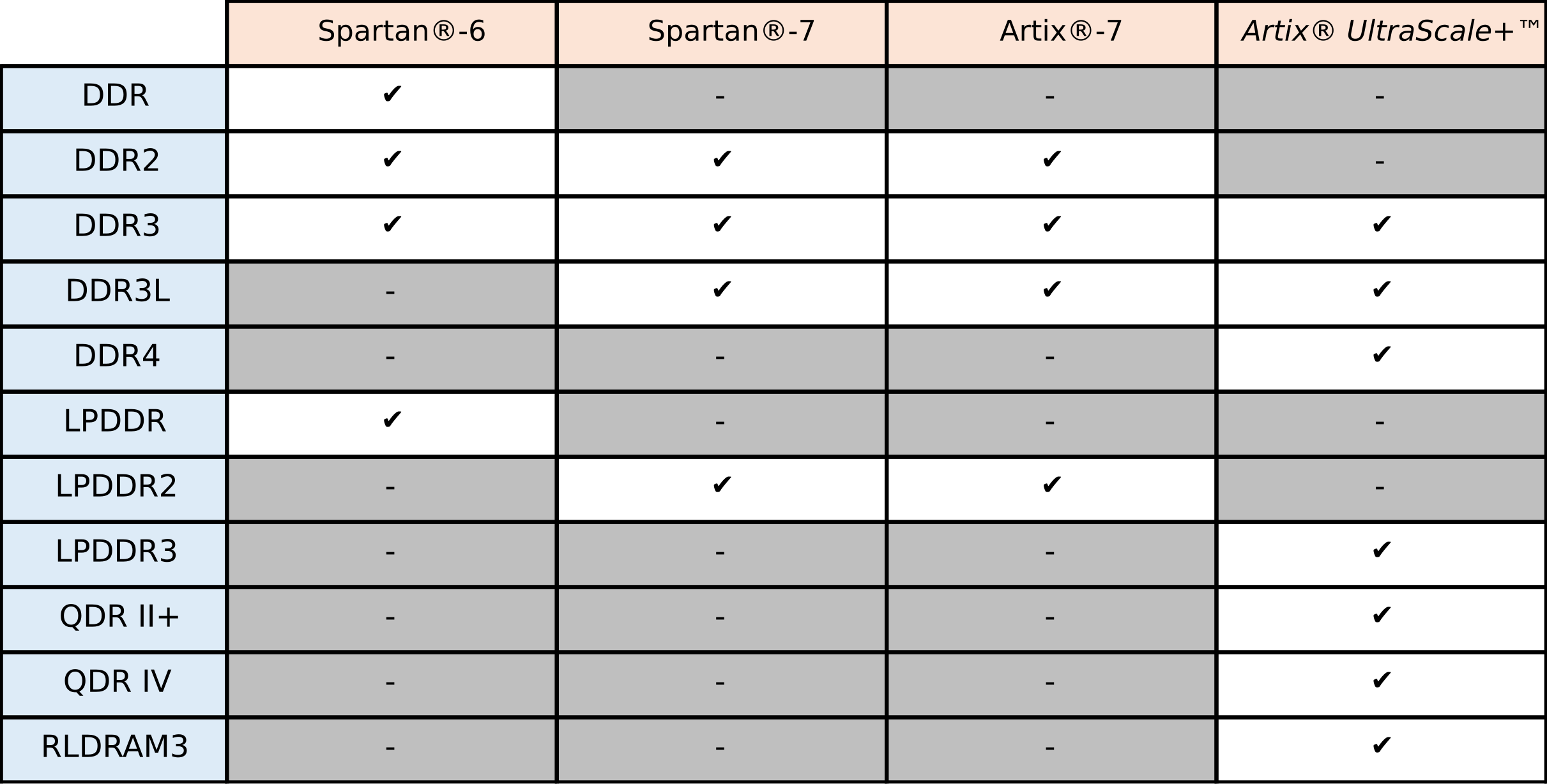

サポートしているメモリについて

各FPGAでサポートしているメモリについて記載します。

表1 サポートメモリ一覧

メモリの機能として以下に記載しますが、詳細については、各データシートをご確認ください。

DDR3の主な機能

- ・最大72bit幅のインタフェースをサポート

・シングル、デュアルランクのUDIMM、RDIMM、SODIMMをサポート

・DDR3(1.5V)、DDR3L(1.35V)

・1Gb、2Gb、4Gb、8Gbのデバイスをサポート

・8バンクをサポート

・x8、x16デバイスをサポート

・8:1のDQ:DQS比をサポート

・データバス幅(8の倍数)を指定可能

・8wordバーストをサポート

・オンダイ終端(ODT)をサポート

・DDR3のライトレベリングをサポート

・JEDEC®準拠のDDR3初期化をサポート

・内部VREFをサポート

DDR2の主な機能

- ・最大64bit幅のインタフェースをサポート

・シングルランクのUDIMM、RDIMM、SODIMMをサポート

・1Gb、2Gbのデバイスをサポート

・4、8バンクをサポート

・x8、x16デバイスをサポート

・8:1のDQ:DQS比をサポート

・データバス幅(8の倍数)を指定可能

・8wordバーストをサポート

・オンダイ終端(ODT)をサポート

・JEDEC®準拠のDDR2初期化をサポート

・内部VREFをサポート

QDR II+の主な機能

- ・QDR II+SRAMデバイスをサポート

・x18、x36デバイスをサポート

・データバス幅(x18、x36)を指定可能

・2、4wordバーストをサポート

・内部VREFをサポート

RLDRAM3の主な機能

- ・x18、x36デバイスをサポート

・データバス幅(x18、x36、x72)を指定可能

・2、4、8wordバーストをサポート

・オンダイ終端(ODT)をサポート

・内部VREFをサポート

LPDDR2の主な機能

- ・最大32bit幅のインタフェースをサポート

・2Gb、4Gbのデバイスをサポート

・8バンクをサポート

・x16、x32デバイスをサポート

・8:1のDQ:DQS比をサポート

・8wordバーストをサポート

・JEDEC®準拠のLPDDR2 SDRAMの初期化をサポート

・内部VREFをサポート

出典:Zynq-7000 AP SoC および 7 シリーズ デバイス メモリ インターフェイス ソリューション(v4.1)(DS176)

https://docs.amd.com/v/u/ja-JP/ds176_7Series_MIS

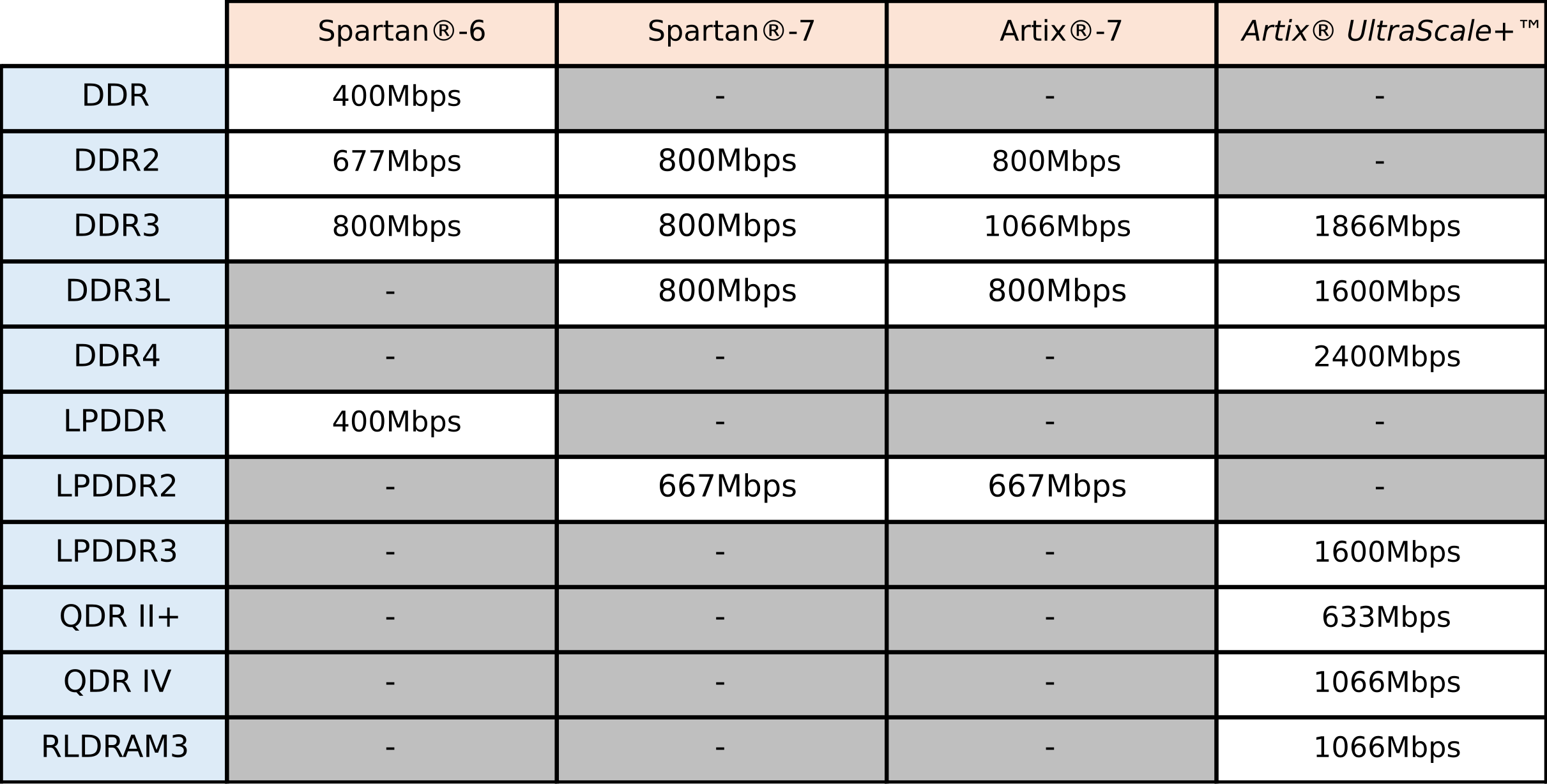

メモリのデータレートについて

表2に、FPGAのメモリのデータレートについて記載しています。

デバイスのスピードグレードによってMAXデータレートは異なるため、データシートによる確認を行ってください。

表2 データレート一覧

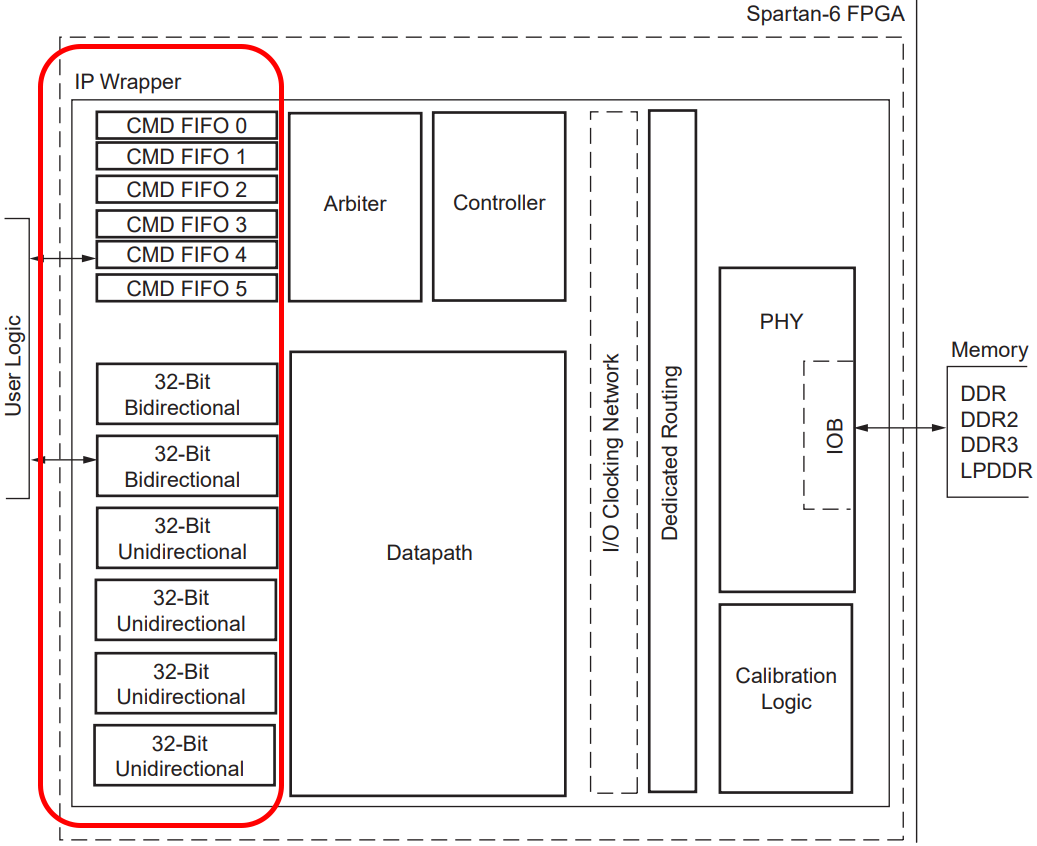

メモリコントローラについて

以降メモリコントローラについて記載します。Spartan®-6 FPGAシリーズから移行する場合、Memory Interface Generator(MIG)の再生成が必要になります。

Spartan®-6 FPGA ファミリではハードブロックIPでしたが、Spartan®-7 FPGA ファミリ、Artix®-7 FPGA ファミリ、Artix® UltraScale+™ FPGAファミリでは、ソフトブロックIPに変更となっています。そのため、ユーザーインタフェースの信号に違いがあるため、接続の変更が必要になります。

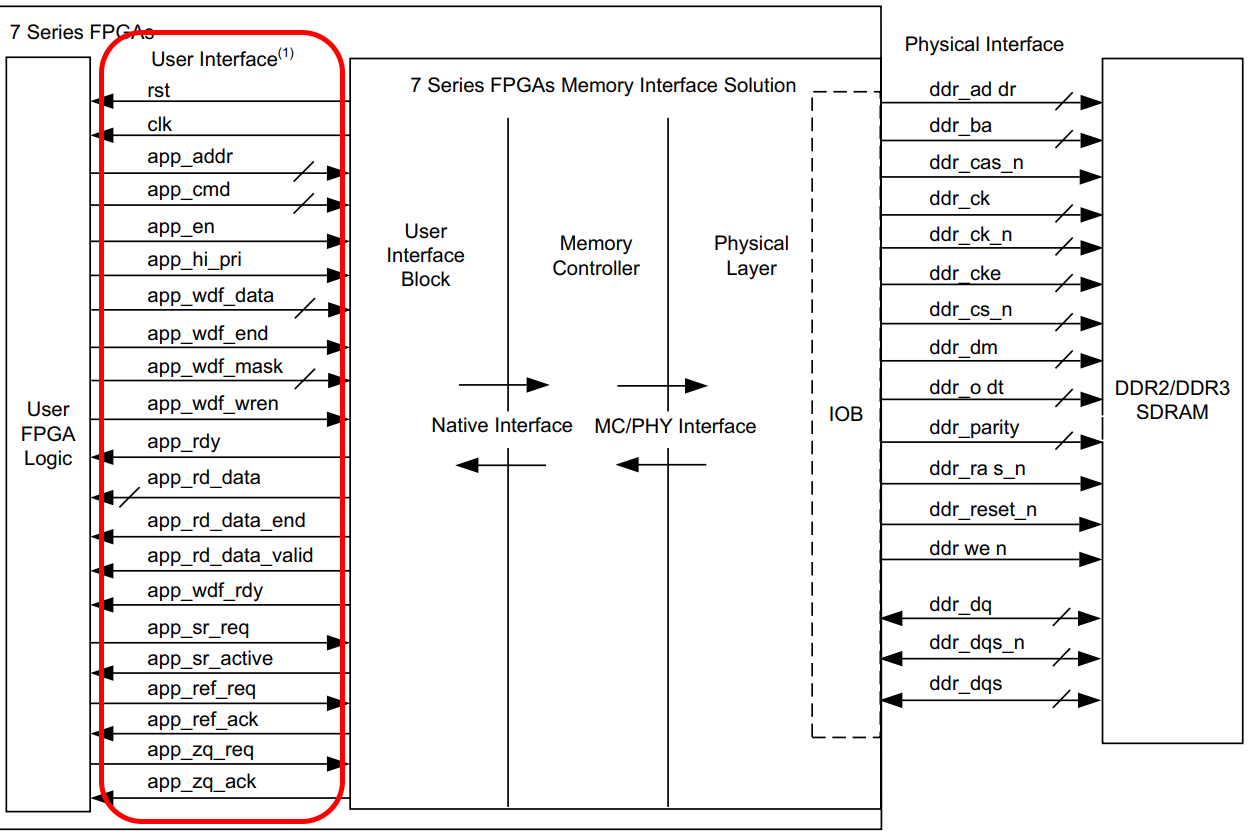

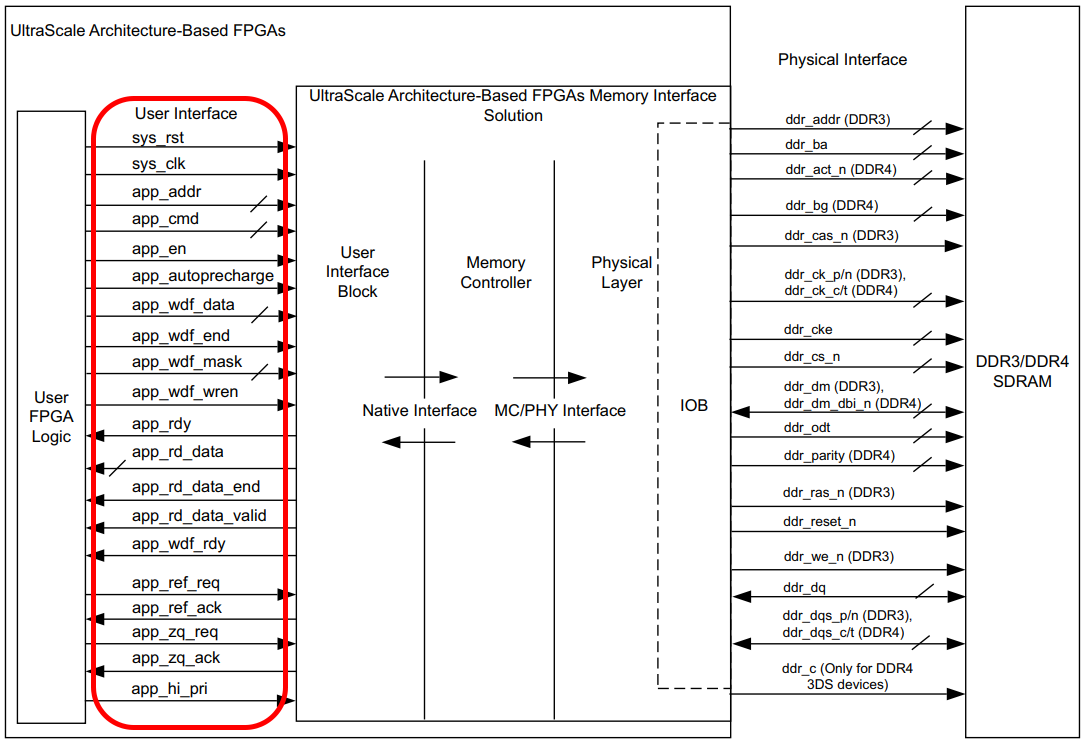

以下にSpartan®-6 FPGA ファミリ、 Spartan®-7 FPGA ファミリ、Artix®-7 FPGA ファミリ、 Artix® UltraScale+™ FPGAファミリそれぞれの構成ブロックを示します。

赤枠の部分がユーザー側のインタフェースになり、接続信号が異なりますので、接続変更が必要になります。

Spartan®-6 FPGA ファミリの場合

図1 Spartan-6 FPGA メモリ コントローラ ブロック (IP ラッパの図)

出典:Spartan-6 FPGA メモリ コントローラ ユーザー ガイド (UG388)(P11)

https://docs.amd.com/v/u/en-US/ug388

Spartan®-7 FPGA ファミリ、Artix®-7 FPGA ファミリの場合

図2 7シリーズ FPGA メモリ インタフェース ソリューション

出典:Zynq-7000 SoC および 7 シリーズ デバイス メモリ インターフェイス ソリューション v2.3 ユーザー ガイド (UG586)(P90)

https://docs.amd.com/v/u/en-US/ug586_7Series_MIS

Artix® UltraScale+™ FPGA ファミリの場合

図3 UltraScaleアーキテクチャベースのFPGA DDR3/DDR4メモリ インタフェース ソリューション

出典:UltraScale Architecture-Based FPGAs Memory IP Product Guide(PG150)(P15)

https://docs.amd.com/v/u/en-US/pg150-ultrascale-memory-ip

マルチポート機能について

Spartan®-6 FPGA ファミリでは、専用のマルチポート機能がサポートされていましたが、Spartan®-7 FPGA ファミリ、Artix®-7 FPGA ファミリ、Artix® UltraScale+™ FPGA ファミリは、非サポートとなっています。

そのため、Spartan®-7 FPGA ファミリ、Artix®-7 FPGA ファミリ、Artix® UltraScale+™ FPGA ファミリでは、ユーザーインタフェースを"AXI"とすることで、IPインテグレータ(IPI)を使用し、マルチポート機能を有するAXI Interconnect IPとの接続が可能となります。

今回は、以上です。

おわりに

いかがでしたでしょうか?

FPGAの置換シリーズとして6回にわたり、Spartan®-6 FPGA ファミリからの置き換えの際に注意すべき点についてお伝えしてきました。

これからもFPGA設計の際のお役立ちコンテンツを、ブログとして掲載していきたいと思います。

よろしくお願いします。

参考文献

参考文献

Zynq-7000 AP SoC および 7 シリーズ デバイス メモリ インターフェイス ソリューション(v4.1)(DS176)

Spartan-6 FPGA メモリ コントローラ ユーザー ガイド (UG388)(P11)

Zynq-7000 SoC および 7 シリーズ デバイス メモリ インターフェイス ソリューション v2.3 ユーザー ガイド (UG586)(P90)

UltraScale Architecture-Based FPGAs Memory IP Product Guide(PG150)(P15)

このブログは「FPGA設計ブログ一覧」の

Spartan®-6 FPGAファミリの置換 の

ひとつです。