FPGAの置換(Spartan®-6 FPGA ファミリ)第3回(置換時のSelectIO™移行注意点)

世界的な半導体の供給不足等で設計開発に影響が出ています。

AMD ザイリンクス社でも、Spartan®-6 FPGA ファミリの入手が困難になっています。

FPGAの置換(Spartan®-6)の第3回では、置換時のSelectIO™移行注意点をお伝えします。

このブログは「FPGA設計ブログ一覧」の

Spartan®-6 FPGAファミリの置換 の

ひとつです。

目次

それでは始めましょう。

SelectIO™のプリミティブ

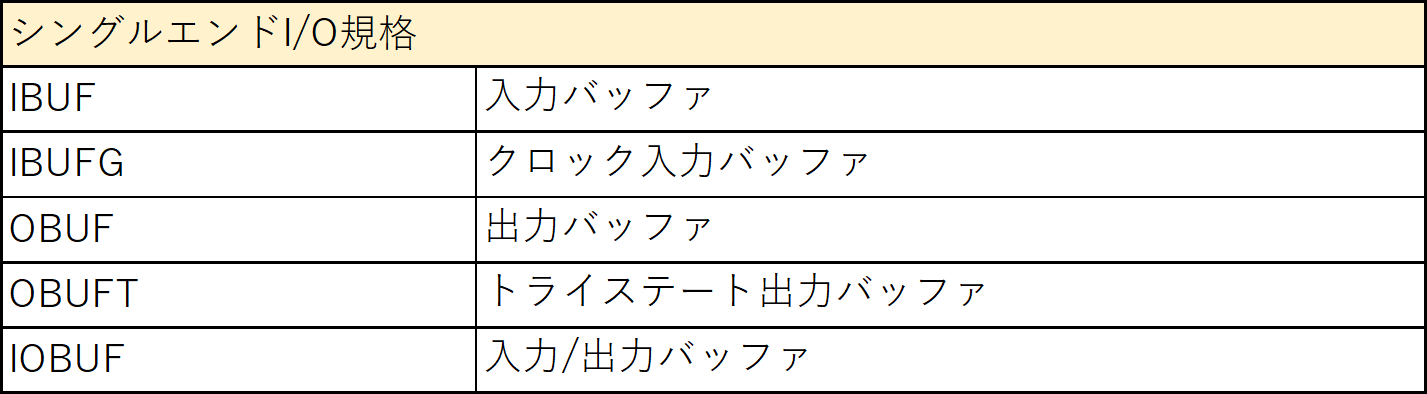

I/Oプリミティブでは、利用できる様々なI/O規格があります。

基本的なプリミティブを以下の表に示します。

(Spartan®-6 FPGA ファミリ、 7シリーズ FPGAの共通)

シングルエンドI/O規格

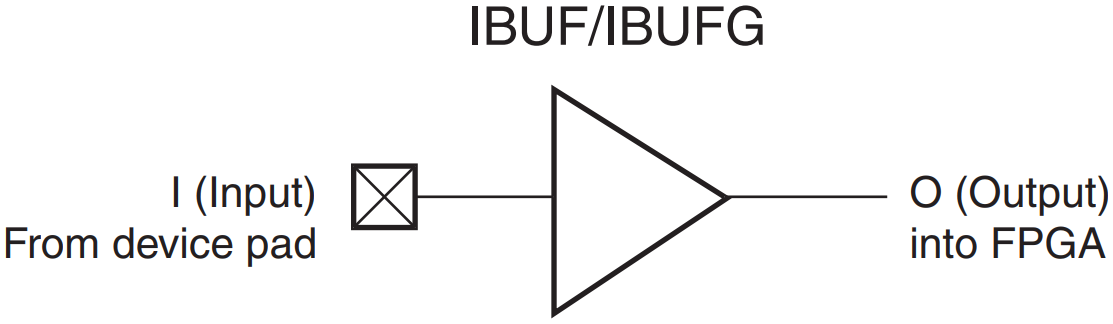

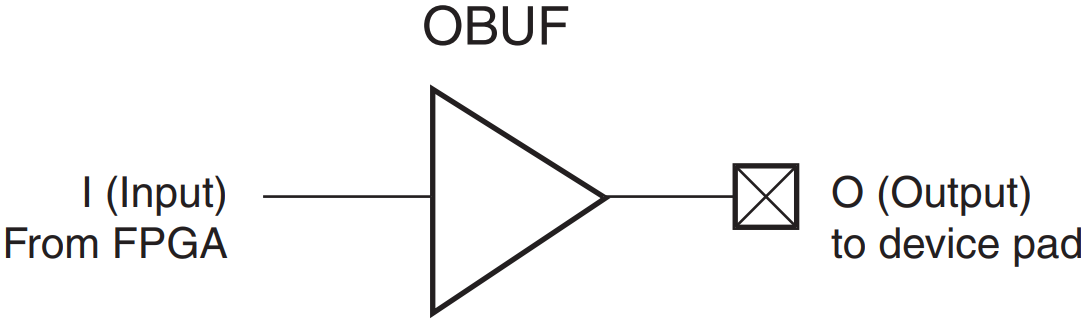

| 入力バッファ(IBUF/IBUFG) | 出力バッファ(OBUF) |

|---|---|

|

|

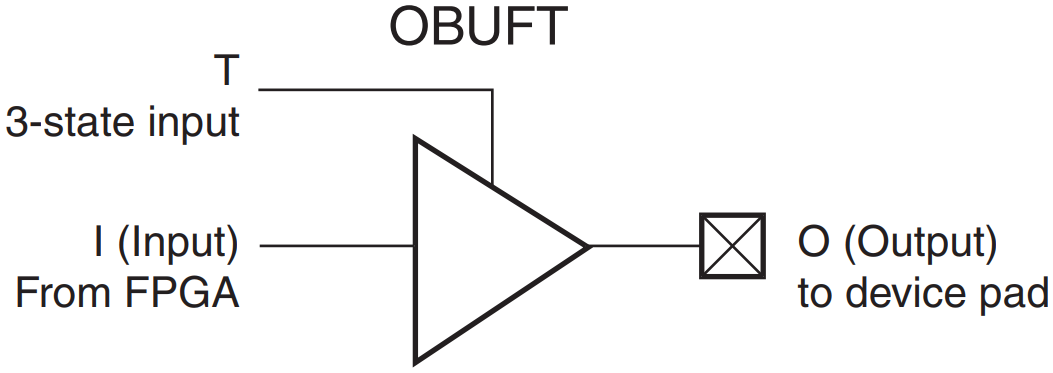

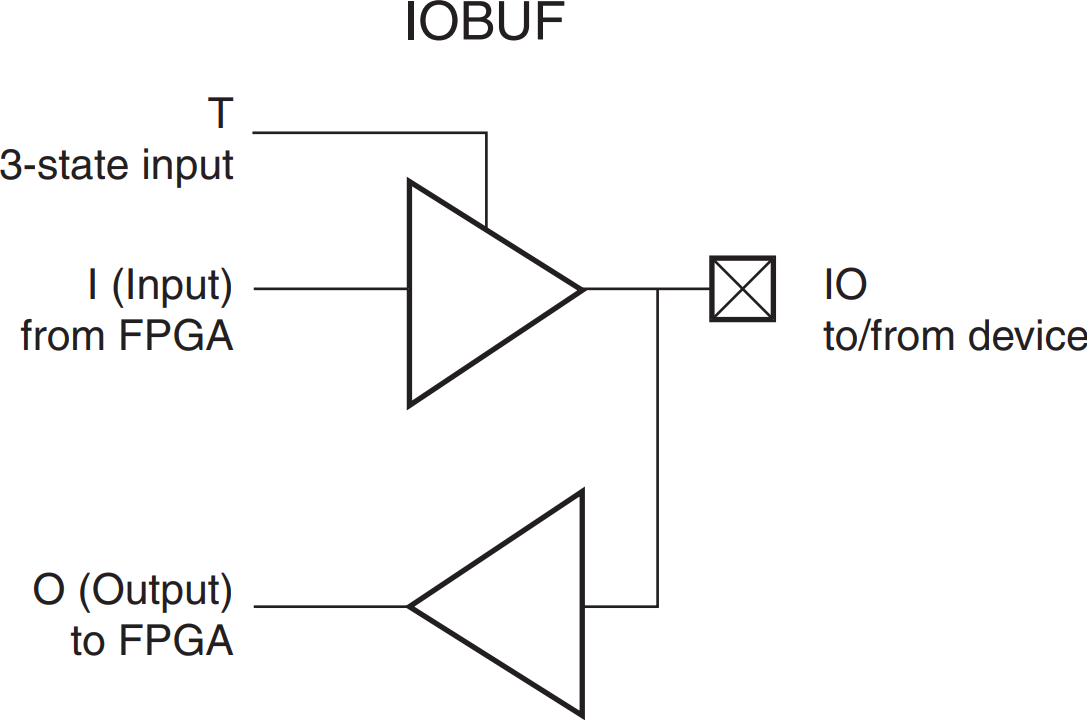

| トライステート出力バッファ(OBUFT) | 入力/出力バッファ(IOBUF) |

|

|

※画像クリックで大きな画像が表示されます。

出典:7 Series FPGAs SelectIO Resources UG471 (v1.10)

https://japan.xilinx.com/content/dam/xilinx/support/documentation/user_guides/ug471_7Series_SelectIO

(参照2022-06-30)

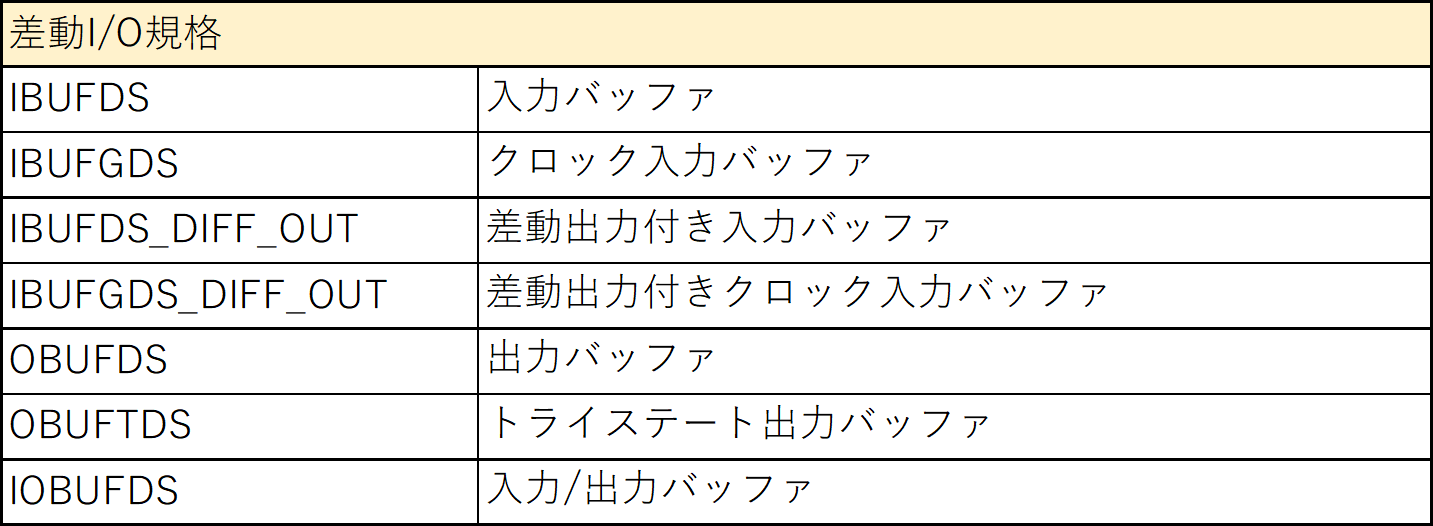

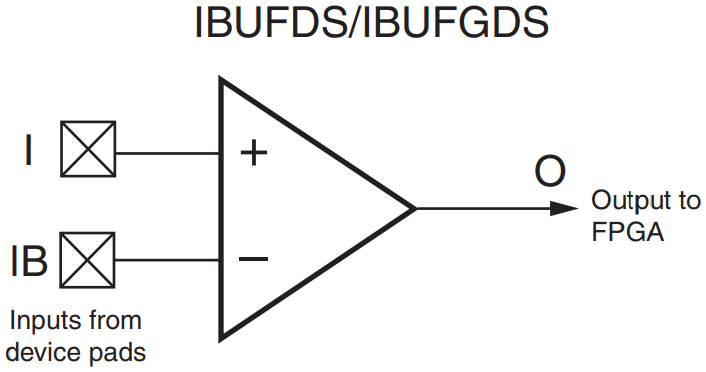

差動I/O規格

| 差動入力バッファ (IBUFDSおよびIBUFGDS) |

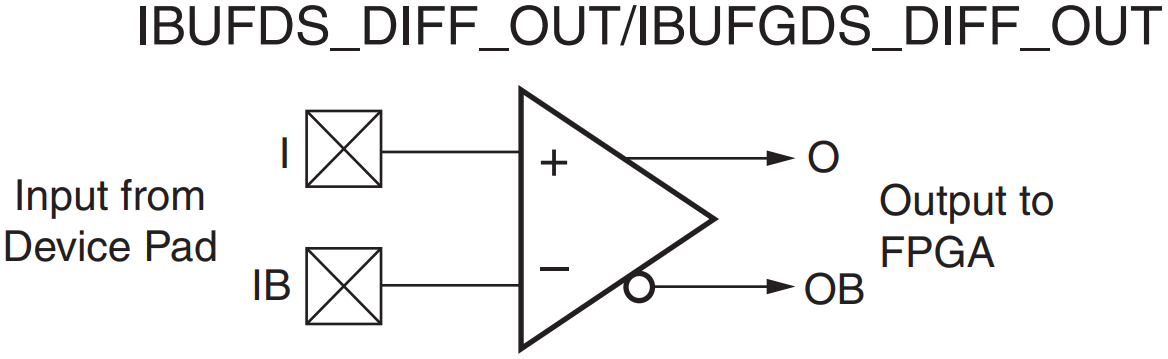

動出力を持つ差動入力バッファ (IBUFDS_DIFFOUTおよびIBUFGDS_DIFFOUT) |

|---|---|

|

|

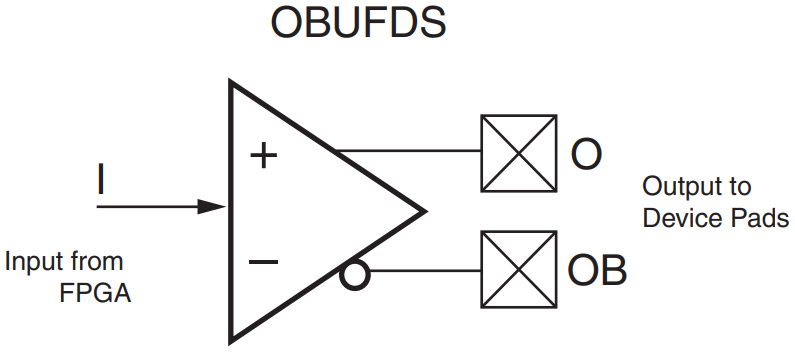

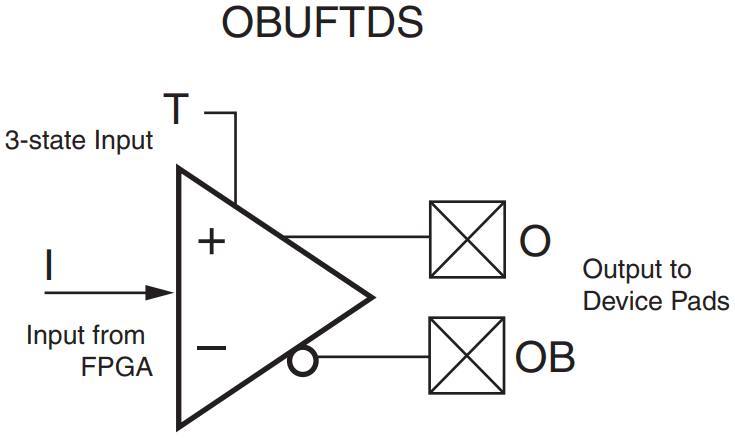

| 差動出力バッファ(OBUFDS) | 差動トライステート出力バッファ (OBUFTDS) |

|

|

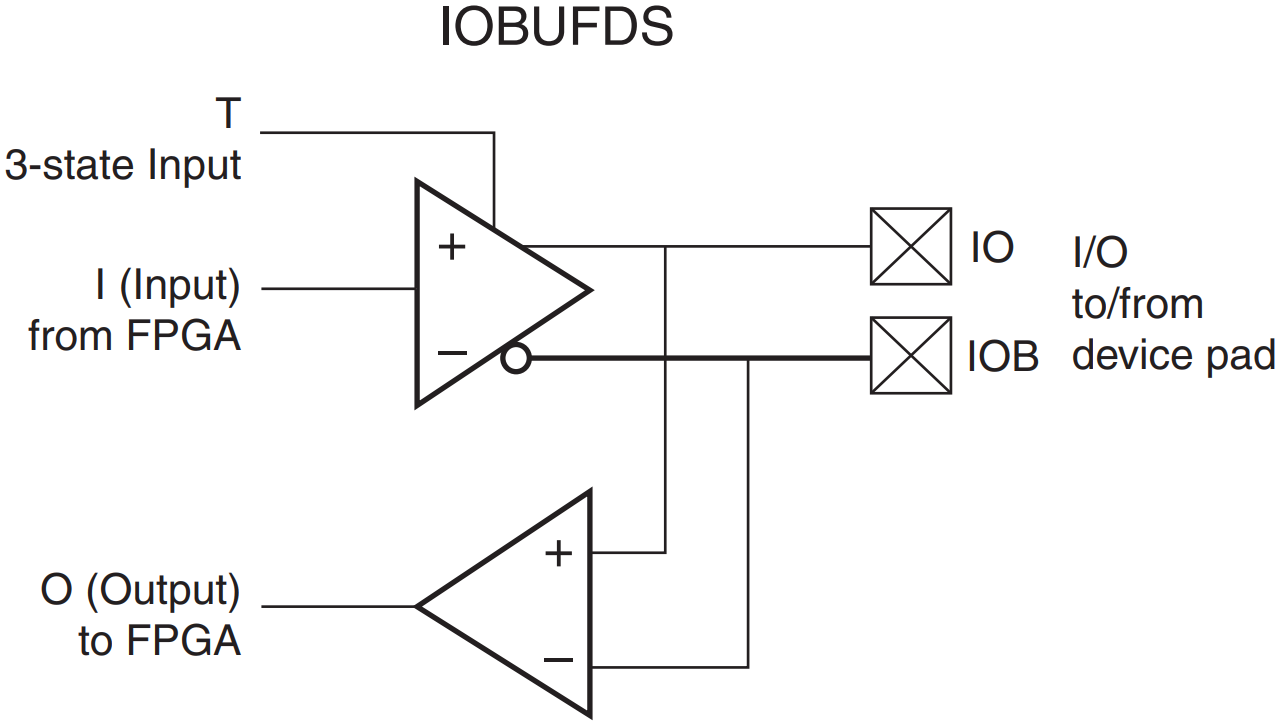

| 差動入力/出力バッファ(IOBUFDS) | |

|

※画像クリックで大きな画像が表示されます。

出典:7 Series FPGAs SelectIO Resources UG471 (v1.10)

https://japan.xilinx.com/content/dam/xilinx/support/documentation/user_guides/ug471_7Series_SelectIO

(参照2022-06-30)

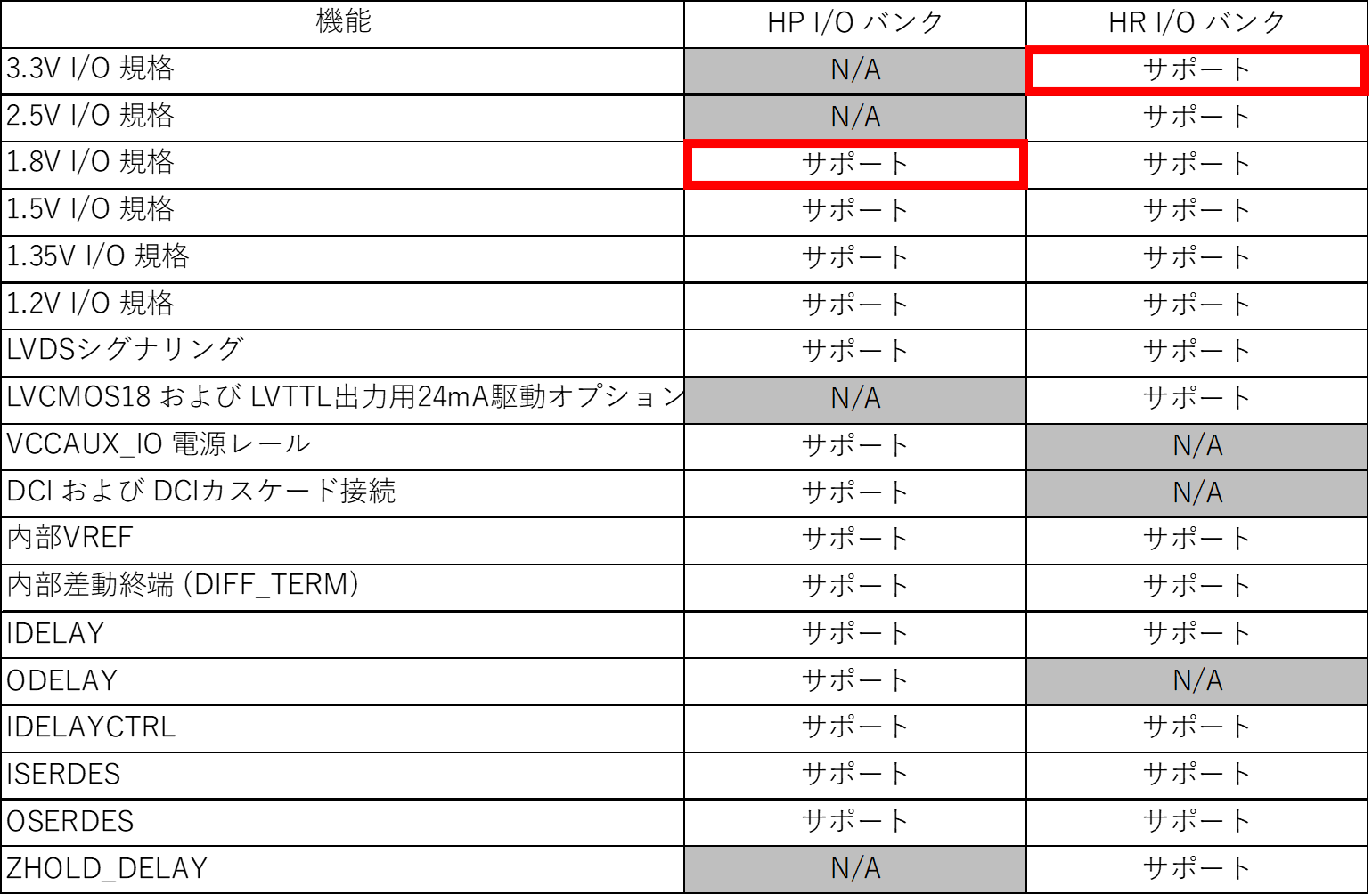

7シリーズのバンク構成

7シリーズでは、ハイパフォーマンス(HP)バンクとハイレンジ(HR)バンクがあります。

HPバンクは、最大1.8Vまでの高速メモリインタフェースを満たすように設計されています。

7シリーズのバンク構成

HRバンクは、最大3.3Vまでの幅広いIO規格をサポートするように設計されています。

Spartan®-7 FPGA、Artix®-7 FPGAには、上記で述べているHPバンクはありません。

HRバンクのみの構成となります。

7シリーズとは

7シリーズとは

Spartan®-7 FPGA、Artix®-7 FPGA、Kintex®-7 FPGA、Virtex®-7 FPGA ファミリのこと

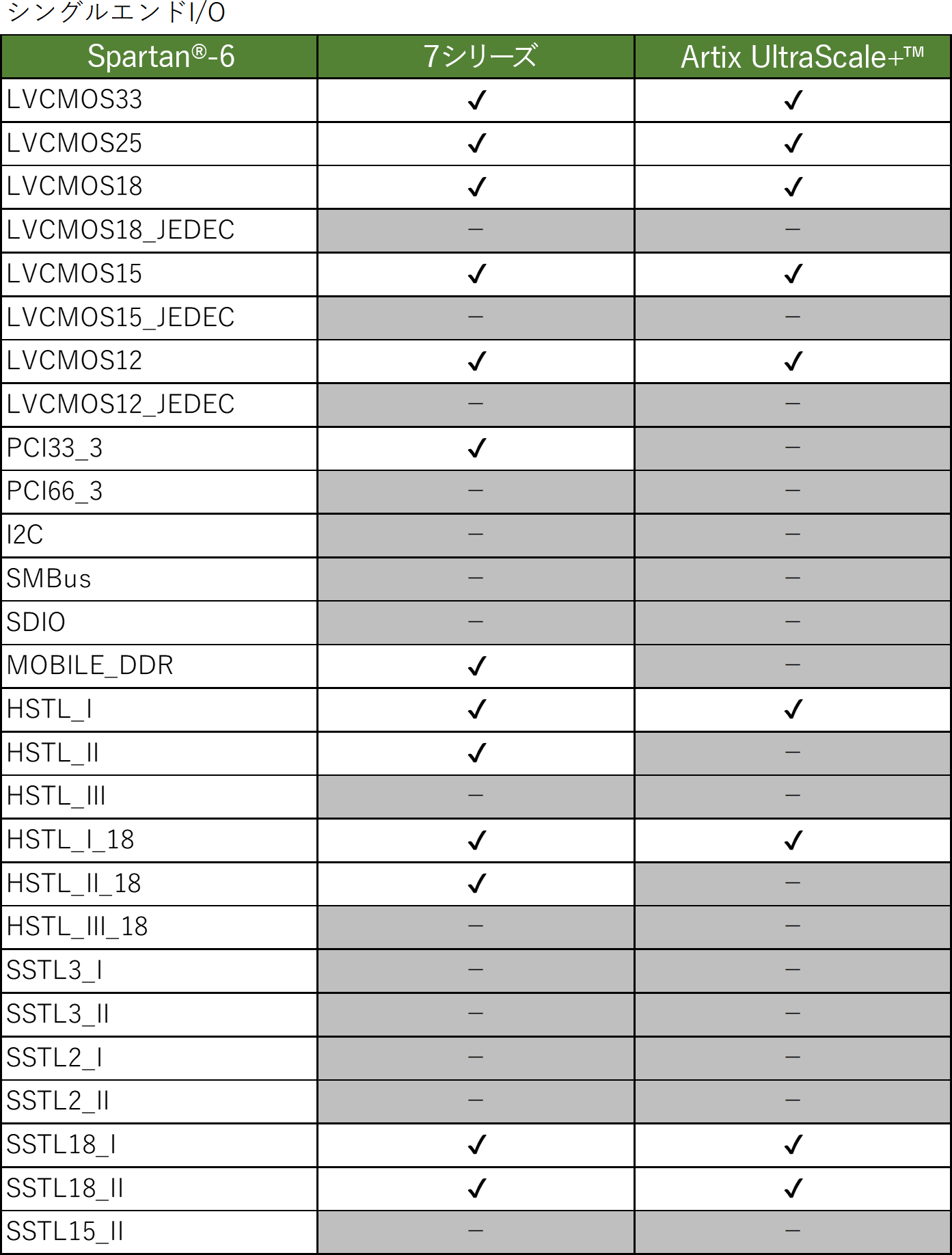

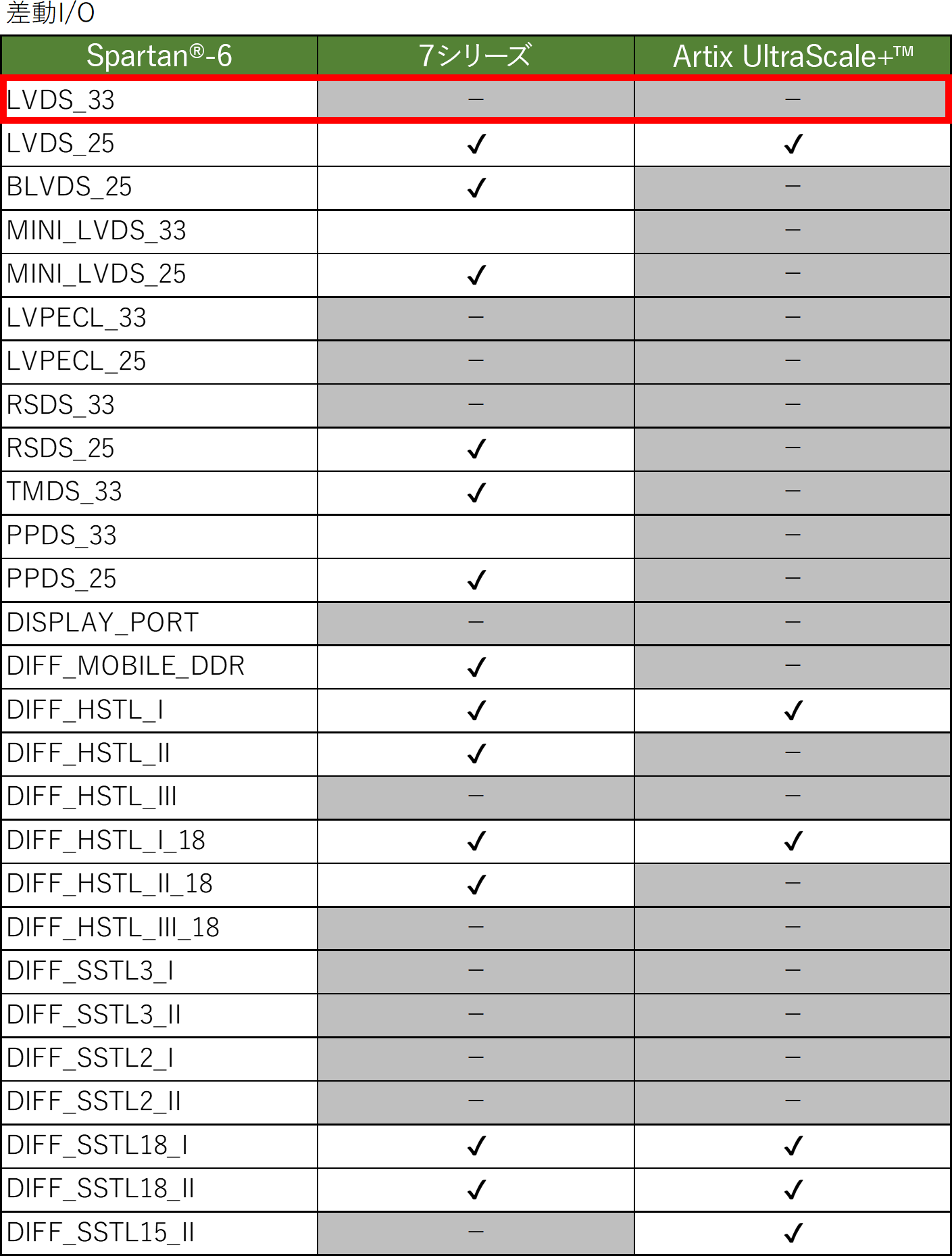

SelectIO™の信号規格について

Spartan®-6 FPGAで使用できていたIO規格が7シリーズ または Artix® UltraScale+™ FPGA ファミリで使用できない場合があることに注意が必要です。

詳細は、各デバイスのデータシート参照ください。

以下にSpartan®-6と比較したIO規格の表を示します。

上記表より「LVDS_33」は、7シリーズ または、Artix® UltraScale+™ FPGA ファミリではサポートされていないことが分かります。

HRバンク、HDバンク、HPバンクいずれも、VCCO端子に3.3Vの給電はできません。

補足

補足

VCCO=1.8VでなくてもHPバンクのLVDS入力は許容されますが、出力側は1.8Vで給電されるバンクのみで使用可能となります。

同様に2.5Vも同じで、VCCO=2.5VでなくてもHR or HDバンクのLVDS入力は許容されますが、出力側は2.5Vで給電されるバンクのみで使用可能となります。

DIFF_TERM属性=FALSEとし、外部差動終端抵抗(100Ω)を行う必要があります。

デザイン環境のインタフェースが必須で、使い方によっては基板の構成にも影響があります。ご注意ください。

最後までご覧いただきありがとうございました。

参考資料

参考資料

7 Series FPGAs SelectIO Resources UG471 (v1.10)

Spartan-6 FPGA SelectIO Resources UG381 (v1.7)

このブログは「FPGA設計ブログ一覧」の

Spartan®-6 FPGAファミリの置換 の

ひとつです。