機械学習の導入で設計チームの強化を(Design and Verification LANDSCAPE 2021-Vol3)

機械学習やAIは、金融や保険、医療、流通、製造、サービスとあらゆる業種に対して導入が進み、高い効果が示されている。EDAツールやツールフローも例外ではない。AIはArtificial Intelligenceの略であり、日本語では人工知能である。人間の脳では当たり前の学習や推論、認知、知覚、判断をコンピュータに行わせる。その中核となる学習方法やシステムに関する技術が機械学習である。

機械学習はMachine Learningの対訳であり、膨大なデータをもとに分析を行ない、精度の高い予測や判断を実現する技術である。さまざまなデータを繰り返し学習する中から、相関関係を見出し、それを基に高精度な結果予測を可能にする。

近年のめざましいAI活用に大きく寄与しているのが機械学習の進化であり、中でも深層学習 – Deep Learningは、人間の神経細胞であるニューロンの仕組みを真似たニューラル・ネットワークを基盤に、教師付き学習を行う技術であり、特に膨大な量のデータを扱う分野においては、人間の認識能力をはるかに超えた成果が期待される。

目次

EDAツールの技術

一方でEDA分野においてはさまざまなツールがあるが、なかでも配置配線や機能検証には非常に多くの解法やアルゴリズムが採用されてきた。ランダム化とランダムソルブ、ナレッジベースによる解法、アニーリング手法、BDDベースのSATラーニングなど枚挙に遑がない。そして実際には、例えばランダムシードとアニーリング手法の組合せや、複数の解法のシーケンスが適材適所で使われる。Design Automation ConferenceやICCADといった学会では、毎年のように多くのアルゴリズムや適用のための手法が考案され、実際の設計データに基づく評価などを含め、議論されている。

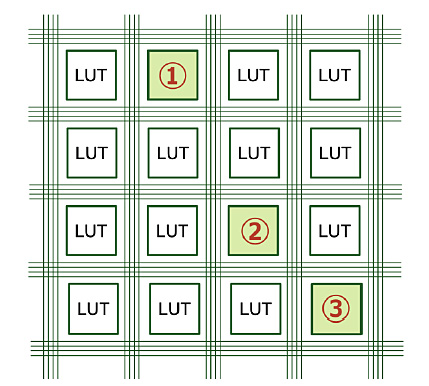

EDAでは扱う設計データ量が膨大で、いわゆる「総当たり戦」に基づく解法は少ない。例えば図1.に示すようなFPGAのごく一部を切り出して、ここにある16個のLUTブロック内にマッピングする組合せを考えてみる。

図1. FPGAの一部を構成する16個のLUT

この16個のLUTから、最初のLUTにマッピングする可能性としては16とおりある。ここでは仮に①にマッピングされたとする。次のLUTにマッピングする可能性としては①以外の15とおりとなる。仮に②にマッピングされたとする。さらに次のLUTにマッピングする可能性としては、①と②を除く14とおりある。仮に③にマッピングされたとする。このように考えていくと、組合せ、つまり総当たり戦による組合せの数は16x15x14x… という計算、つまり16の階乗であり、その数はおよそ20.9兆にもなる。今日、多くのユーザが使用するFPGAの規模は、わずか16個のLUTを遥かに凌ぐものであり、さらに配線の経路も含めて考えると、この組合せ数は気の遠くなる数になることは間違いない。

そこでFPGAの配置配線ツールでは、ランダム配置を始め、さまざまな技術を駆使してFPGAの配置配線を行うことになる。しかし同時にユーザによるコントロールも欠かせない。そこで配置配線ツールに対してTCL環境から制約を与えることになる。しかし、XILINXのVirtex Ultrascaleなどのデバイスを例にとると、VIVADOで与えることができる制約やオプション値のすべての組合せ数は、40x1021個、つまり40垓という膨大な数になってしまっている。

総当たり戦による解法は英語ではbrute forceと表現され、いわゆる力ずくの対応方法を意味する。しかし現実的な設計においては、その組合せ数や処理能力、対応するステート空間が天文学的な数字となるなど、NP/NPTと呼ばれる問題にクラス分類される。これはNon-deterministic Polynomial Timeというクラスであり、アルゴリズムを構成するPolynomial – 多項式を解く方法としては決定的であるものの、それを妥当な時間内や計算機資源で解こうとすると現実的な解決が期待できない問題を指す。

このような問題に対して使われる手法の代表はヒューリスティック・アプローチと呼ばれる手法である。このアプローチの特徴は経験則に基づき、試行錯誤的な手法を取ることである。必ずしも正解を出せるわけではないが、ある程度、求める解に近いものが得られる。機械学習の多くのエンジンでは、ヒューリスティック・サーチと呼ばれる探索方法が使われている。

EDAにおける機械学習の適用

EDAにおいても、ヒューリスティック・サーチを用いた機械学習の適用が始まっている。例えばLintのコード解析やCDCの構造解析などはスタティックに行われるため、どうしても擬似エラーが混入し、ノイズとなってしまう。設計者はレポートされた内容に沿って1つずつ、擬似エラーか真のエラーかを判定しなくてはならないため、デバッグ解析機能におけるCause & Effectのように、根本となる原因にさかのぼる機能が求められる。この部分に対して、人が判断する部分を少しでも機械学習が補うことで、効率を上げようとするツールも使われている。

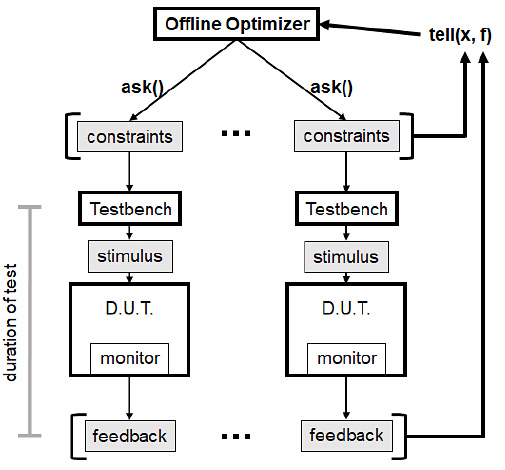

またEDAツールの内部に機能として備わっていなくても、ユーザが機械学習をフローに対して適用する事例も出てきている。2021年3月に開催されたDVCon USでNVIDIAが発表した事例では、UVMを用いた制約付きランダム検証のフローにおけるテスト生成に対して機械学習を適用している。具体的にはランダム変数に対する制約を自動的に調整するために、ベイズ最適化(BayesOpt)や勾配ブースティング回帰ツリー(GBRT)といった機械学習モデルを活用している。機械学習を用いたフローでは、人手によるフローに対して、同じイタレーション数において活性化できた機能カバレッジを6.3倍にまで引き上げることに成功している。この機械学習モデルはPythonのライブラリとして呼び出すことができ、このリグレッションテストにもPythonが組み込まれている。図2にそのフローを示す。

図2. 機械学習によるランダム制約最適化のフロー

機械学習をどこに適用するか、どのような機械学習モデルやエンジンを採用するか、データ加工方法や特徴抽出はどのように行うか、評価方法と精度向上のプロセスをどのように策定するかなどは、この例ではNVIDIAがトライアル的な作業を繰り返し、実用に至っている。そこにはUVMによる共通検証環境の上で適用可能な機械学習のノウハウが詰まっている。しかしそのノウハウは、必ずしも汎用性を目指したものではないため、他社の設計スタイルに対しては当てはまらないかも知れない。

一方で、機械学習のノウハウを汎用化しているツールもある。例えばFPGAの論理合成や配置配線といったコンパイルフローに機械学習を適用して最適化するものである。この場合、なぜ汎用化ができるのかと言えば、そこにはFPGAが持つプラットフォーム性がある。前出のNVIDIAの検証フロー例とは異なり、FPGAのコンパイルフローはベンダとデバイスシリーズ、パッケージ、スピードグレードが決まれば、個別の設計フローへの依存度は低く、むしろ大多数のユーザに共通な開発プラットフォーム上で実行されるフローとなる。

前出のとおり、VIVADOなどのコンパイルフローで指定可能な制約やオプションの組合せは40垓にもなっている。コンパイルを数時間も走らせた結果、あるブロックにおいてタイミングが間に合っていないとレポートが出された場合、ユーザはどのオプションを変更して再コンパイルすべきか、直感的に分かるものではない。仮にそれが分かったとしても、変更した制約やオプションによって、今度は別の箇所でタイミングエラーになることも考えられる。いわゆる「もぐらたたき」である。プロジェクトによっては、タイミング要件が満たされずに、終わりが見えないまま1ヶ月も2ヶ月もコンパイル作業を継続し、挙げ句の果てに高価なスピードグレードへの変更を決断したり、もしくはRTLの変更に戻って機能検証からやり直す、といった予測不可能なプロセスに陥る場合もある。

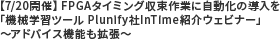

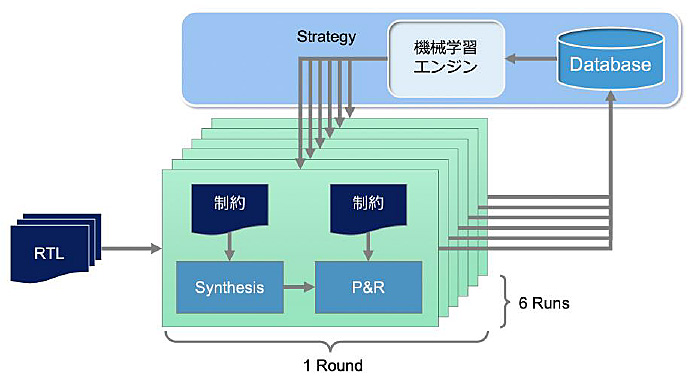

そこで、FPGAのコンパイルフローに対して機械学習を適用するプロジェクトが増えてきている。図3は、そのフローの概要を示している。

図3. 機械学習を用いたFPGA最適化フロー

このフローでは、論理合成ツールにも配置配線ツールにも、機械学習のエンジンを搭載したツールが制約を設定している。この例ではコンパイルを6つ平行して実行しているが、それぞれ異なる制約が与えられている。そしてコンパイルが終了すると、その結果であるレポートが集約されデータベースに加えられる。機械学習エンジンは自分が与えた制約に対して、結果がどのように分散するのかを学習している。

※画像クリックで大きな画像が表示されます。

図4. 機械学習による最適化フローの自動化

Round-1のフローから学習した結果はR1としてデータベースに蓄積し、そこから次のRound-2用の6つの異なる制約を設定する。この制約条件はRound-1のものとも異なっている。そしてRound-2のフローから学習した情報はデータベースにさらに蓄積される。これを何回か繰り返すことで、最適化フローを自動化しようというものである。制約設定、コンパイルの実行、結果の集約、学習、データベースへの蓄積というシーケンスが自動化されているため、ユーザは最初にツールをキックすれば、あとは指定したラウンド数が終わるまで、あるいはタイミング要件をすべて満たすまで、最適化が繰り返される。

このフローを実際に適用した、あるプロジェクトでは、FPGAベンダの社員でタイミング収束を得意とする熟練したエンジニアが3ヶ月かかっても収束させることができなかったデザインに、図3、図4の機械学習フローを適用させることで、6日間でタイミング収束させている。また、すでに製品化を終えた別のプロジェクトでは、FPGAに対して同フローを適用させ、1ランク下のスピードグレードのデバイスでのタイミング収束に成功し、その後の製品ロットから大幅にコストを削減することに成功している。

このような機械学習によるフローの実現は、FPGAの論理合成や配置配線に詳しいエンジニアを一人追加する事に等しいか、それ以上の価値が得られることを意味する。人手不足やエンジニア育成が課題となっているプロジェクトであれば、大きな導入効果が期待される。またFPGAの最適化フローから開放されることにより、エンジニアは、より創造性に富んだ仕事に専念できることも期待される。

まとめ

機械学習やAIなどの技術は、私たちの生活にも入り込んでいる。EDAツールや開発フローもその例外ではない。機械学習の適用例として、EDAツールの内部に組込む方法もあれば、EDAツールの外側でPython環境と機械学習エンジンを使ってノウハウを蓄積しながらフローを構築する方法もある。また特にFPGAのコンパイルと最適化のように、FPGAのユーザであれば誰もが行わなければならない共通のプロセスに対して、その最適化と自動化を実現する商用のEDAツールもある。そのノウハウはツールベンダが持つことになるが、適用の汎用性は非常に高く、誰でもが恩恵を得られる。

機械学習の活用や適用は、すでに黎明期ではなく、実用化が進んでいる。今後ますます多くのEDAツールや開発環境に適用されることが予測される。従来は人が行っていた作業が機械学習に取って変わられてしまうという発想ではなく、機械学習にできることは機械に任せて、人はより創造性に富んだ価値創造の分野に注力するという発想が必要になってくる。

参考文献

[1] Rajarshi Roy, Mukhdeep Singh Benipal, and Saad Godil, NVIDIA, “Dynamically Optimized Test Generation Using Machine Learning,” in DVCon US 2021.[2] O. Guzey, L.-C. Wang, University of CA, and J. Levitt, H. Foster, Mentor Graphics Corporation, “Functional test selection based on unsupervised support vector analysis,” in 2008 45th ACM/IEEE Design Automation Conference.

[3] Bruce Talley, former VP of Software at Xilinx and PLUNIFY Technical Advisor, “Timing Closure in FPGAs is critical”, on PLUNIFY White Paper

「アサーションベース 検証立ち上げ支援サービス」のご案内

アサーションを導入する際の障壁を取り除き、誰もがプロジェクトでアサーションを使った検証ができるようにすることを目的としたサービスです。

-

「Design and Verification LANDSCAPE」技術情報メールニュース

-

PALTEKでは本ブログ「Design and Verification LANDSCAPE」シリーズの技術情報をメールで年に3-4回発信しています。

ご登録いただいた方には、最新の情報をメールニュースとしてお届けします。

ご希望の方はこちらのフォームよりご登録ください。※競合製品取り扱い企業様の申込については、お断りする場合がありますので予めご了承ください。

このブログのシリーズ

Design and Verification LANDSCAPEシリーズ一覧は下記になります。是非あわせてお読みください。