アサーション検証のすすめ〜パート1(Design and Verification LANDSCAPE 2020-Vol4)

Jay. K

商用のアサーション検証ツールが発売されたのが2001年の4月、今年で20年にもなるが、一体どのくらいの設計者/検証者または設計プロジェクトで使用されているのだろうか?定かではないが、ここ10〜15年で大規模かつ複雑なASIC開発を行っている会社の多くが新規設計プロジェクトで導入、運用をしているようである。

アサーションの標準言語が存在せず、ベンダー固有の言語のみだった時代には一部の先進的なユーザだけが使用していたが、現在ではSystemVerilog Assertions (SVA)やProperty Specification Language(PSL)等がIEEEの標準言語として存在しており、使用環境は整ってきている。そして、近年では大規模かつ複雑なFPGAデバイスがリリースされており、FPGAユーザにも以前よりアサーション検証導入の波が押し寄せている。

Wilson Research Groupが2018年に世界規模で行った調査によれば、FPGAプロジェクトの67%でアサーションベース検証が採用されている。

目次

おさらい、アサーション検証のメリット!

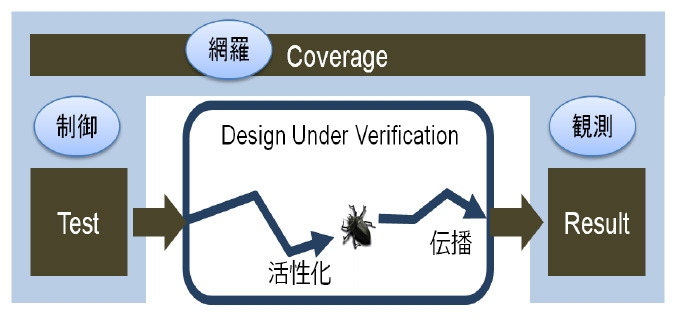

設計者や検証者がよく誤って理解しているのが、アサーション自体がバグを見つけに行くと思っていることである。

実際はアサーションがバグを見つけるのではなく、シミュレーションを行った時のバグ発見の加速、バグに伴う起因を簡単に知るための環境を提供するものである。

既存シミュレーションとアサーション付きシミュレーションの比較

ここから図1.と図2.を用いて、アサーション検証の一般的なメリットについて簡単に解説する。

図1.は既存のシミュレーション環境を表している。基本的なシミュレーション作業はテスト入力を作成して出力側で結果を観測する。この手法では、設計の大規模化と複雑化が進むにつれ、内部で発生したバグが出力まで伝搬させる時間とその制御が大きな問題となる。

図1. 既存のシミュレーション環境

図2.は既存のシミュレーション環境にアサーション手法を取り入れたイメージである。

内部で発生したバグを赤いパトランプでイメージしたアサーションが検出し、出力まで伝搬されるのを待つことなく即座に状況を捉えることができる。そしてバグの近傍でその原因を知ることができる。このメカニズムにより出力まで伝搬させる時間を短縮し検証効率を上げることが可能になる。

図2. アサーション手法を取り入れたシミュレーション環境

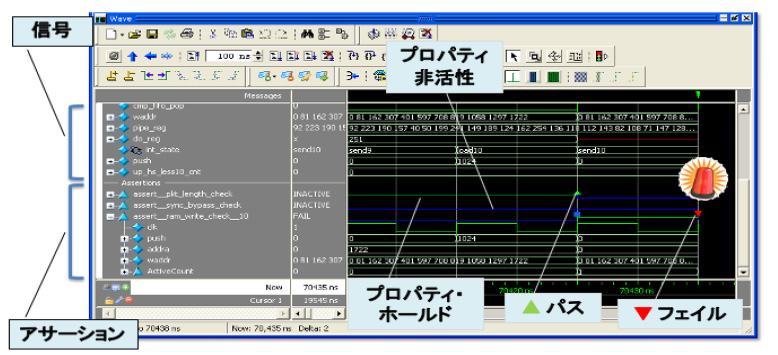

図3.にアサーション付きシミュレーションを実施しているシミュレータの波形ウィンドウの例を示す。シミュレータのGUIではアサーションがいつ活性化しパスしたか、またはフェイルしたかなどを、アサーションを構成する信号とともに簡単に知ることができる。

図3. アサーション付きシミュレーションの波形表示例

前出のアサーション検証のメリットも含め、アサーション検証によってもたらされるメリットを以下に示す。

- バグ検出時間の短縮

・バグに起因する動作違反を即座に警告 - バグ修正時間の短縮

・バグに関連する信号を即座に特定 - バグ修正後の確認時間の短縮

・バグ検出を最終出力まで伝搬させる時間を短縮、シミュレーション時間も短縮可能 - 検証労力の省力化

・シミュレーション結果の検証を波形目視確認ではなく、自動で行える - 問題の切りわけが容易

・自分が担当するブロックへのイリーガルな入力や、ハンドシェイクのタイムアウトなどを容易に特定可能 - 検証資産の再利用

・テストベンチやデザインを変更した時にも再利用ができる

アサーション検証手法〜初期導入の提案

設計者や検証者の中には「アサーション検証手法は色々メリットがありそうだが、どのような箇所にアサーションを書くのが有効なのか?」という疑問があり、なかなか最初の一歩が踏み出せないでいる人もいる。

そこで今回は前出のアサーション検証のメリットのリストで4番目の「検証労力の省力化」について、その例とともに解説する。その効果は、今まで波形の目視確認で行っていたシミュレーション結果のチェック作業の担い手をアサーションに置き換えることで自動化を図り、チェック時間を削減し、人為的なミスの混入を低減しようとするものである。

シミュレーションの目視検証をアサーションへ置き換え

現在FPGA設計者や検証者が一般的に行っているシミュレーション作業は、入力テストパターンを作成してシミュレーションを実行し、その結果の波形を目視で確認するというものである。しかし対象デザインの大規模化や複雑化によって、目視確認作業は検証労力の増大を招いている。

例えば、ロングシーケンスが入力された後、あるきっかけとなる信号がアクティブになった後に動作が始まるような論理の振舞いを目視チェックする場合、ヒューマンエラーが起こりやすく、検証の質が低下しやすくなる。

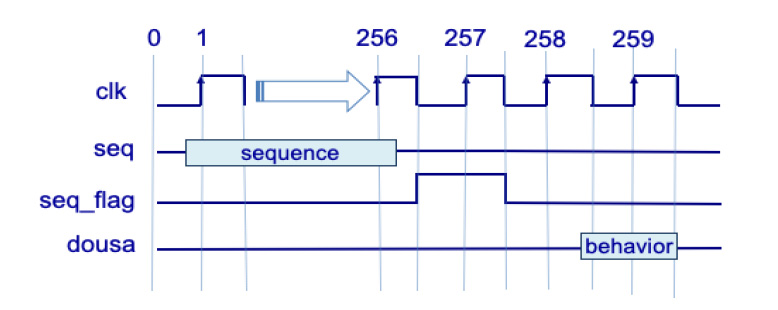

図4.に長いサイクルのシーケンスを伴う動作のチェックをイメージしたタイミングチャートを示す。

seq信号のシーケンス入力が256サイクル期間あり、次のサイクルでシーケンス入力が終わったことを知らせるseq_flag信号がアクティブになってから2サイクル後にdousa信号をチェックする。このようなチェックは目視で行うには多大な労力を要する。

図4. ヒューマンエラーを起こしやすい長いサイクル数の目視チェック例

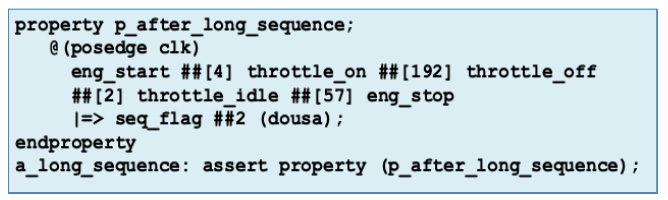

そこでこのチェックを図5.のようなアサーション記述に置き換えることによって、目視チェックを自動化し、ヒューマンエラーを防ぐことが可能となる。

図4.でsequenceと表記されている部分は、図5.にあるようにシーケンスのプロトコルを明記する。

図5. 目視チェックを自動化するアサーション記述

図5.の記述内容は、eng_start信号がアクティブになり、その4サイクル後にthrottle_on信号がアクティブ、192サイクル後にthrottle_off信号がアクティブ、2サイクル後にthrottle_idle信号がアクティブ、そして最後に57サイクル後にeng_stop信号がアクティブになりシーケンス部の記述が終わる。そして次のサイクルでシーケンス終了合図のフラグseq_flag信号がアクティブになり、2サイクル後にdousa信号がアクティブになる。

このように目視でチェックする内容をアサーションに置き換えることによって、チェックする信号が多く、サイクル数が長いシーケンスを含む動作を簡単にチェックすることが可能となる。

まとめ

アサーション検証手法は既存のシミュレーション環境を変えることなく、アサーション記述を追加するのみで簡単に取り込める検証手法である。またテスト入力の変更やデザインの変更によって再度シミュレーションする際に、アサーションを再利用することも可能である。

まだアサーション検証手法を取り入れていないプロジェクトでは、是非導入されることを推奨したい。また今後の「Design and Verification LANDSCAPE」でもアサーションの再利用性やアサーションの効率的な記述方法などについても取り上げる予定である。

「アサーションベース 検証立ち上げ支援サービス」のご案内

アサーションを導入する際の障壁を取り除き、誰もがプロジェクトでアサーションを使った検証ができるようにすることを目的としたサービスです。

-

「Design and Verification Landscape」技術情報メールニュース

-

PALTEKでは本ブログ「Design and Verification Landscape」シリーズの技術情報をメールで年に3-4回発信しています。

ご登録いただいた方には、最新の情報をメールニュースとしてお届けします。

ご希望の方はこちらのフォームよりご登録ください。※競合製品取り扱い企業様の申込については、お断りする場合がありますので予めご了承ください。

このブログのシリーズ一覧は下記になります。是非あわせてお読みください。