FPGA機能検証の課題と機会(Design and Verification LANDSCAPE 2020-Vol1)

Harry Foster – Mentor, A Siemens Business

Verification Horizons, 2018年11月 – Volume 14より

目次

はじめに

IC/ASICの機能検証トレンドに関する調査については、長年にわたり複数の調査結果が発表されてきた。[1] [2] [3] [4] しかしながらFPGA(Field-Programmable Gate Array)に特化した機能検証トレンドについては調査研究がされていないか、少なくとも公開されていない。この点を鑑みて本稿では「2018 Wilson Research Group Functional Verification Study」の結果から、FPGAに関する主要な調査結果を取り上げる。本調査における機能検証の観点から、今日のFPGA市場の状況に関する貴重な洞察を得ることができる。

世界の半導体市場

世界の半導体市場は2017年に4,447億ドルと推測され、そのうち47億ドルはFPGAによって占められている。[5] [6] FPGA市場は2027年までに88億ドルに達すると予想され、この予測期間中におけるCAGR(年平均成長率)は6.4%で推移すると見られている。この市場の成長は新規および拡張する既存のエンドユーザ・アプリケーションによって促進され、それには自動車、IoT、通信、産業機器、航空/防衛、コンシューマ、およびアクセラレーションが必要とされるデータセンター上のAIアプリケーションが含まれる。

歴史的に、FPGAはASICに対する2つの利点を提供してきた。まずNREが低いため[7]、FPGAは通常は少量生産向けにはIC/ASICよりも費用対効果が優れている点である。

第二に、FPGAのラピッドプロトタイピング機能と柔軟性により、検証や検証サイクルの大部分において実機使用による開発スケジュールの短縮である。最近では、FPGAによるハードウェア並列処理の特徴を活かすことにより、特定のアプリケーションの高速化という面において性能上の利点をもたらす。 (例:AIニューラルネットワーク)

高まる設計の複雑度

2000年半ばから後半にかけてのIC/ASIC市場では、ますます複雑化を遂げた機能検証が大きく立ちはだかる課題であった。同様に今日のFPGA市場においては、今日の複雑なFPGAの規模と機能面が大きな問題となっており、特に高性能プログラマブルSoCであるFPGA(Xilinx® Zynq®、Intel® Arria®、Cyclone®、Stratix®、Microsemi® SmartFusion®など)では、その複雑度への対応を余儀なくされている。従来から行われている実機ベースのFPGA検証や正統性評価のアプローチは、その効果が低下している。本稿では今日のFPGA検証プロセスの非効率性を、深刻なバグの市場流出という観点から定量化する。

FPGA検証の有効性

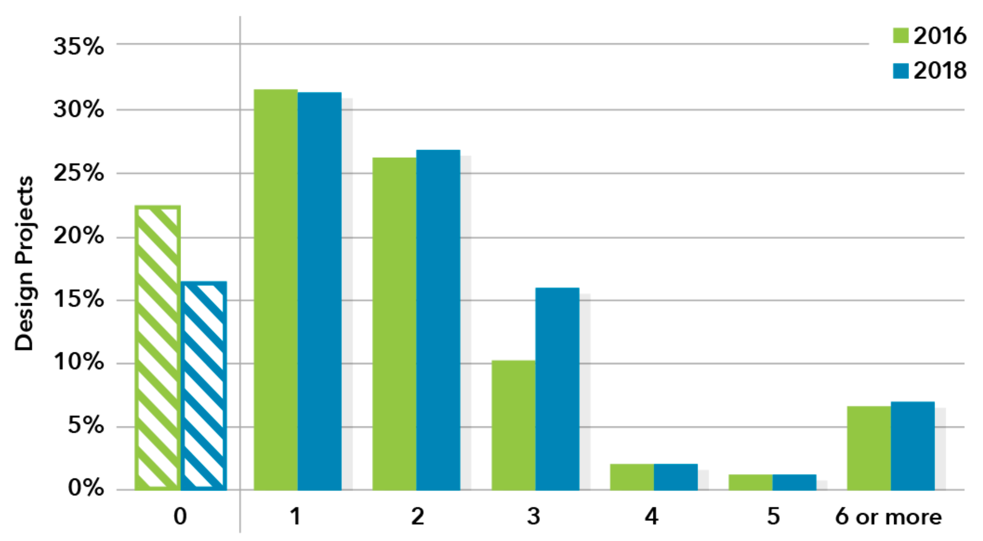

IC/ASICプロジェクトでは、プロジェクトにおける検証の有効性を評価するための指標として、「量産開始前に必要となったスピン数」が広く使用されている。歴史的にIC/ASICプロジェクトの約30%が初回シリコンでの成功を達成することができるものの、ほとんどの設計では2回目のシリコンスピンを経て製品化される。

図1. 製品として流出した無視することのできないバグ数

残念ながらFPGAプロジェクトには同等の指標が存在しない。

そこで我々の研究ではIC/ASICのスピンに代わる指標として、FPGAプロジェクトに対して「無視することのできないバグが、どれほど製品として流出したか?」という設問を加えて調査した。

図1に示す調査結果からは、気掛かりな様相を呈している。2018年の調査結果では、すべてのFPGAプロジェクトのうち、製品へのバグ混入を回避できたのは、ほんの16%にすぎなかったこれは、初回シリコンでの成功という点からするとIC/ASICよりも低い数字である。市場分野によっては、フィールドにおける改修コストが高くつく可能性もある。例えば航空/防衛の分野では、FPGAを改修するためにシステムのカバーを一度取外したら、再びシステム全体を検証しなくてはならない。

FPGA 検証に費やされる労力

このセクションでは、FPGAプロジェクトの時間と資源に関する傾向について説明する。

プロジェクト時間のうち検証に費やされる時間の割合

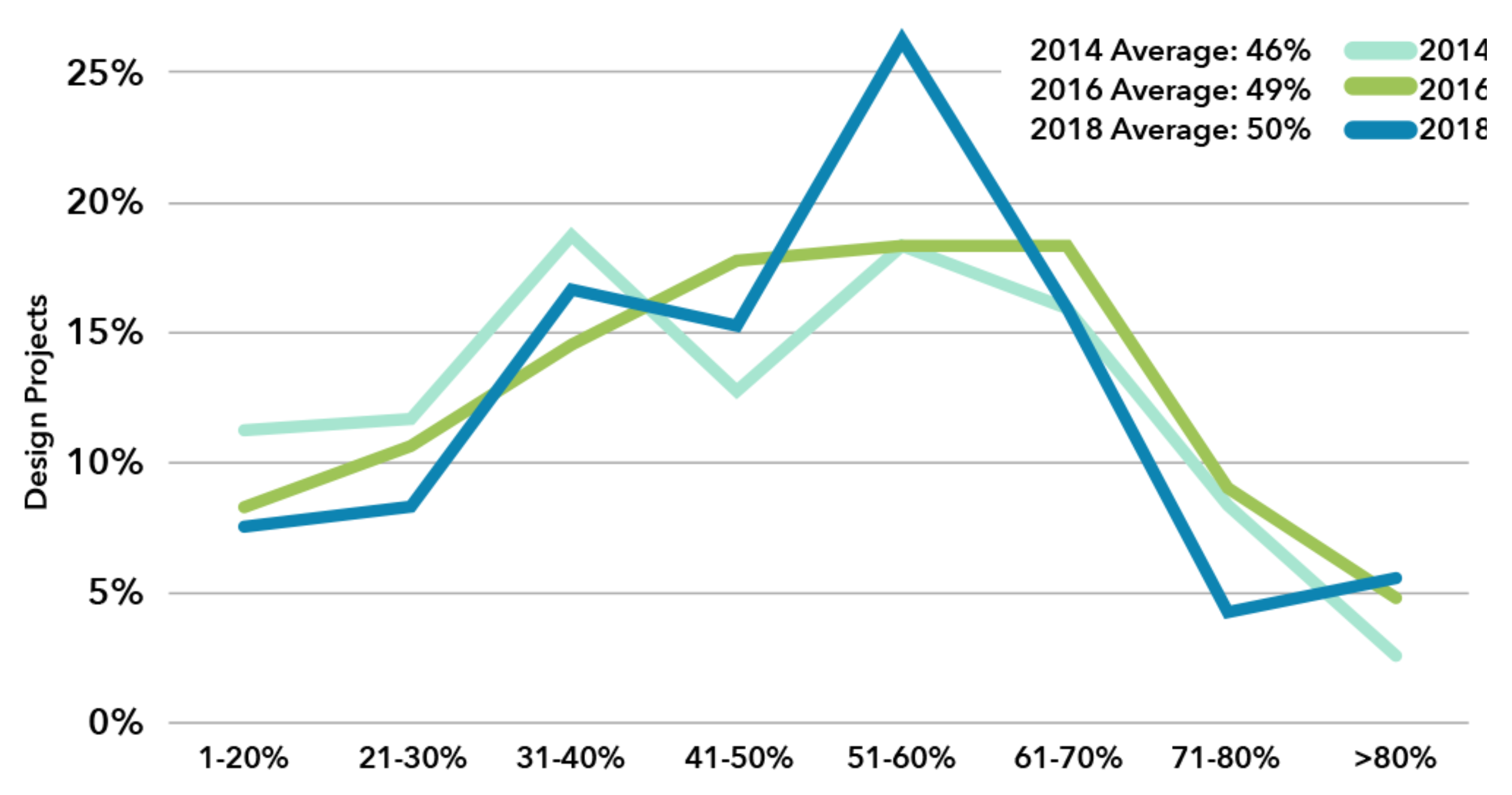

図2は、FPGAプロジェクト時間のうち、検証に費やされた合計時間の割合を示している。このグラフには2つの極端な例がある。一般的に検証にほとんど時間を費やさないプロジェクトでは、すでに検証された既存の設計IPを大量に使用して新規設計とする場合が多い。一方で極端に多くの時間を検証に費やすプロジェクトでは、検証する必要のある新規設計IPの割合が高いことが多い。

図2. FPGAプロジェクトのうち検証に費やされた時間の割合

全体として見ると、2014年から2016年、2018年へと、検証に費やされた時間の平均割合が増加していることもわかった。ここから設計と検証の複雑度が高まっていることが伺える。

平均ピークエンジニア数

今日の最大の課題の1つは、おそらくコストとエンジニアリングの人員を管理しコントロールすることであろう。つまりFPGAの設計と検証の生産性を高めるソリューションを特定することである。生産性向上の必要性を説明するために、技術者数の増加という観点から傾向を探る。

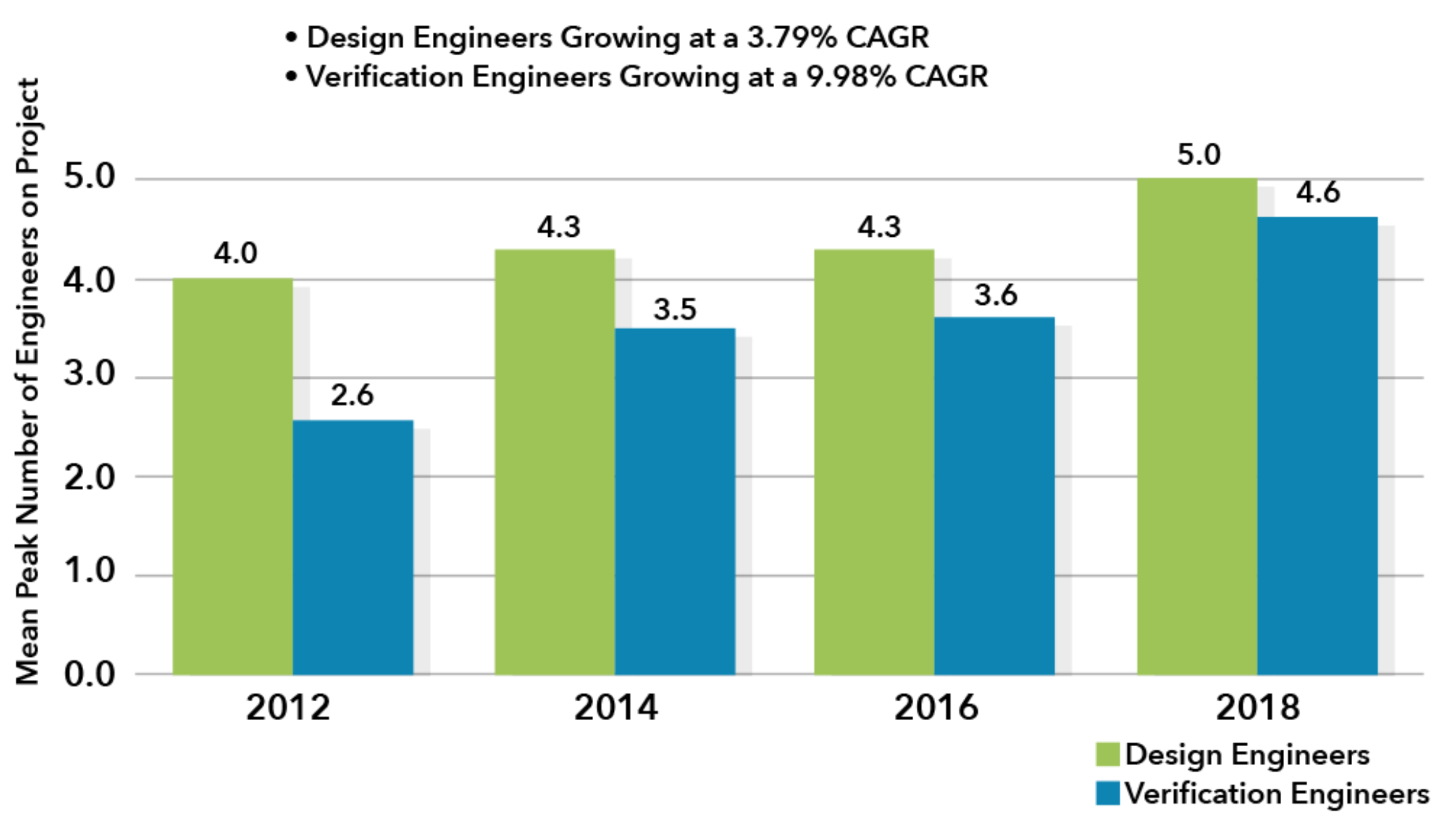

図3は、FPGAプロジェクトに取組んでいるエンジニアの平均のピーク値を示している。

図3. プロジェクトにおけるピーク時のエンジニア数の平均

平均して、設計エンジニアのニーズは約4%のCAGRで成長しており、これはIC/ASICの成長率と同様である。しかし検証エンジニアの需要は約10%のCAGRで成長している。IC/ASIC市場で2007年から2014年の間に、検証エンジニアに関する同様の成長需要の増大を経ていることを鑑みると、増大する検証の複雑さに対応してきたことは注目に値する。[3]

FPGA 検証技術導入のトレンド

検証の複雑化に対応すべく、多くのFPGAプロジェクトでは検証プロセスの成熟度向上を余儀なくされている。このセクションでは、今日のIC/ASICプロジェクトではかなり標準的な手法となっているさまざまな検証手法がFPGAプロジェクトでどのような採用トレンドにあるかを紹介する。

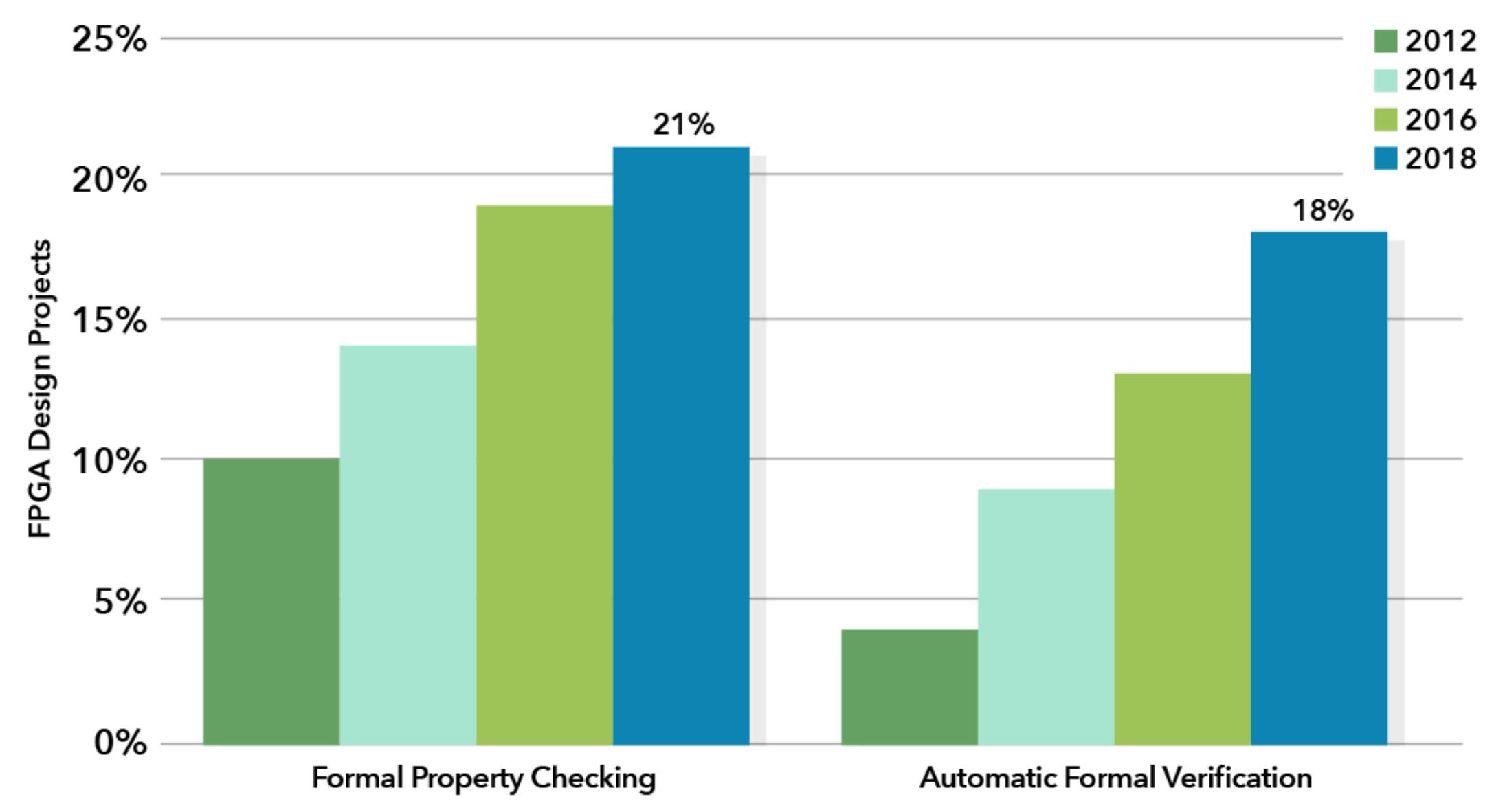

フォーマル検証のプロパティチェック(モデルチェックなど)とオート・フォーマルアプリケーションの導入トレンドを図4に示す。FPGAプロジェクトでのフォーマル・プロパティチェックの導入は、そのCAGRが21%と驚くほど増加しており、オート・フォーマルアプリケーションは29%のCAGRで成長している。フォーマル・プロパティチェックの導入プロセスには、高度なスキルと専門知識が必要だったという歴史がある。しかしながら近年のオート・フォーマルアプリケーションの出現などにより、適用の焦点が絞られたソリューションが提供され、導入への特別なスキルが不要となった背景がある。一般にフォーマルソリューション(フォーマル・プロパティチェックとオート・フォーマルアプリケーションの合計)は、機能検証で最も急速に成長しているセグメントの1つである。

図4. FPGAプロジェクトにおけるフォーマル検証の導入トレンド

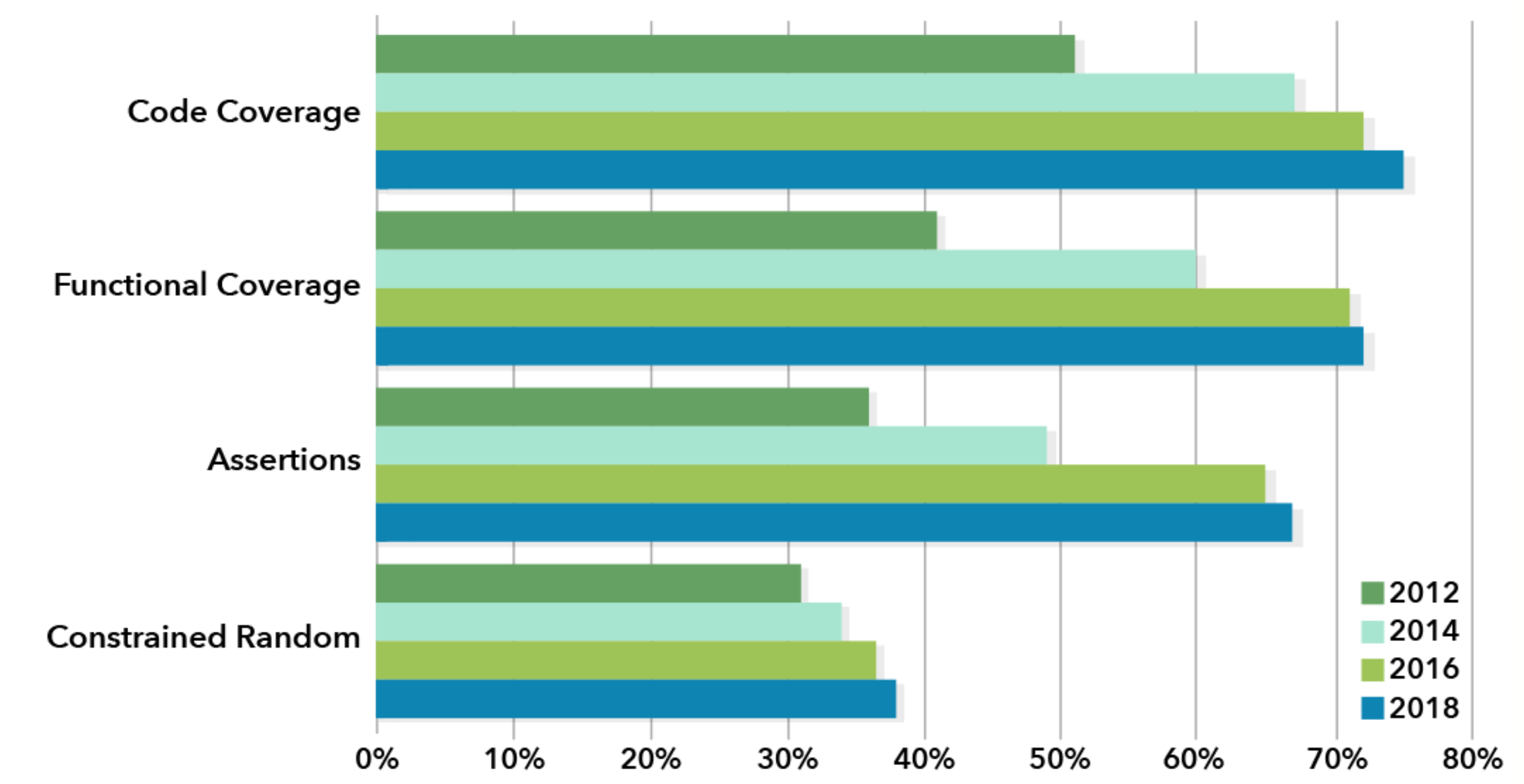

図5にコードカバレッジ、機能カバレッジ、アサーション、および制約付きランダムシミュレーションなど、シミュレーションを基盤とした検証技術のFPGAプロジェクトへの導入トレンド(2012年〜2018年)を示す。

図5. FPGAプロジェクトにおけるシミュレーション基盤の検証技術導入のトレンド

これらの導入トレンドから得られる1つの考察は、FPGA市場において検証プロセスが成熟していることである。この成熟度は設計の複雑度が増していることが背景にあると見られる。

結論および考察

本稿では近年行われてきた大規模な業界調査に基づき、FPGAの設計と検証におけるトレンドを示した。FPGAの複雑度は今日の多くのIC/ASIC設計の複雑度に匹敵する。検証の有効性と労力の観点から、この複雑度の影響を定量化した。

おそらく、今回の調査で得られた洞察において最も懸念される点は、FPGAプロジェクトにおいて製品に混入し市場流出してしまった重大なバグの数に関するものであろう。重大なバグの市場流出の原因となる機能的欠陥の削減努力と、FPGAプロジェクトにおける機能検証プロセスの成熟度との間に興味深い相関関係が見つかった。

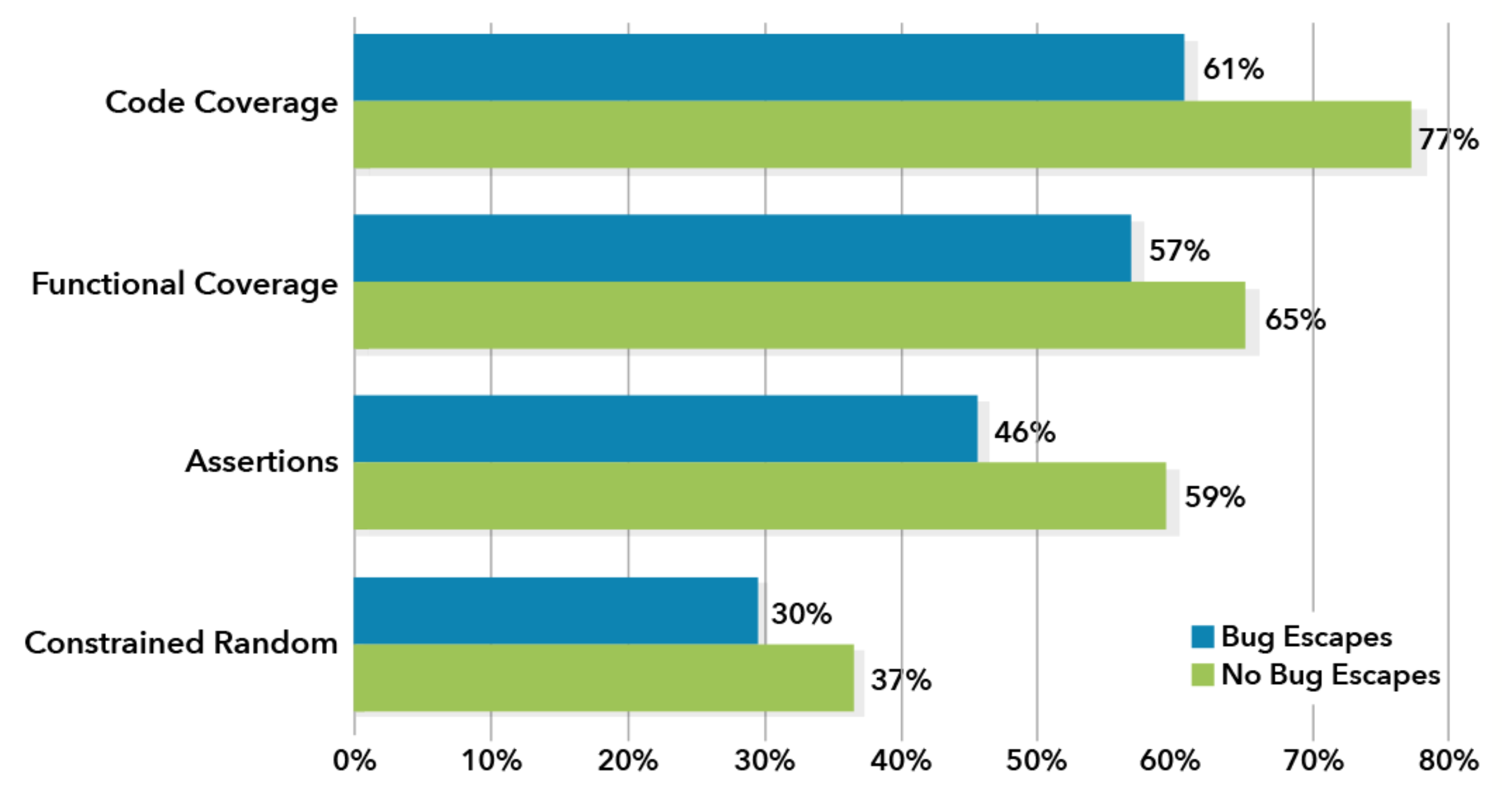

データは、機能検証プロセスがより成熟しているプロジェクトでは、バグの市場流出が低減される可能性が高いことを示唆している。この真偽を確認すべく、今回の調査参加者を2つのグループに分割した。バグ市場流出のないFPGAプロジェクトと、バグ市場流出が発生したFPGAプロジェクトである。次にさまざまな検証手法の導入率を調査した。その結果を図6に示す。

図6. シミュレーション基盤の検証技術導入率と重要なバグ市場流出との関係

この調査結果から、バグ市場流出のないグループの方がさまざまな検証手法の導入率が高い傾向があることが分かり、これは統計的には有意である。しかし、調査から測定できない点は、プロジェクトがこれらの検証プロセスを導入したことが実際にどれだけ効果的だったかである。たとえば、バグ市場流出を経験したグループにも、機能カバレッジを導入しているとするプロジェクトがある。しかし機能カバレッジモデルの有効性は経験不足により不十分である可能性もある。調査データから、特定の検証手法が成功したかどうか、あるいは検証技術の導入が効果的であったかどうかを評価することはできない。

参考文献

[1] R. Collett, “2002 IC/ASIC functional verification study,” Industry Report from Collett International Research, Inc. 2003.

[2] R. Collett, “2004 IC/ASIC functional verification study,” Industry Report from Collett International Research, Inc. 2005.

[3] H. Foster, Trends in functional verification: a 2014 industry study, Proceedings of the 52nd Annual Design Automation Conference, p.1-6, June 07-11, 2015, San Francisco, California.

[4] H. Foster, Trends in functional verification: a 2016 industry study, DVCon 2017, San Jose, California.

[5] IC Insights, The Mid-Year Update to the McClain Report, 2018.

[6] International Business Strategies, Semiconductor Market Analysis, 2017 Review, 2018 Projections, February 14, 2018.

[7] S. Trimberger, Three ages of FPGAs: a retrospective on the first thirty years of FPGA Technology, Proceedings of the IEEE, Vol 103, Issue 3, March 2015.

著者:Harry D. Fosterについて

Harry D. Foster氏はMentor, A Siemens Business、Design and Verification Technology部門のチーフサイエンティストです。

機能検証の優良サイト- Verification Academyの共同創設者であり編集長でもあります。彼は機能検証において複数の特許を取得しているほか、機能検証に関する6冊の書籍を共同執筆しています。

彼はエレクトロニクス業界標準の開発に貢献したことで2006年にAccellera Technical Excellence Awardを受賞しています。また、Accellera Open Verification Library(OVL)標準の最初の作成者でもあります。2019年のDAC – Design Automation Conferenceではテクニカルプログラムコミッティー主査を、2020年のDACではカンファレンス全体の副主査を務めています。

-

「Design and Verification Landscape」技術情報メールニュース

-

PALTEKでは本ブログ「Design and Verification Landscape」シリーズの技術情報をメールで年に3-4回発信しています。

ご登録いただいた方には、最新の情報をメールニュースとしてお届けします。

ご希望の方はこちらのフォームよりご登録ください。※競合製品取り扱い企業様の申込については、お断りする場合がありますので予めご了承ください。

このブログのシリーズ一覧は下記になります。是非あわせてお読みください。