【入門】ModelSimの使い方 <GUI編>~ModelSim 2021.1 ModelSim Intel Edition, Microsemi Edition, ModelSim DE/PE/SE, QuestaSim対応版 ~

当ブログは、保守契約者様向け「ModelSimウェビナー ~ 一連の操作を学ぶ入門編 ~」より一部抜粋してお伝えしております。

ModelSim簡易チュートリアル【GUI編】の

ダウンロードはこちらから

ModelSimを使い始めたけど日本語マニュアルがなくて困ることありませんか?

本ブログは、ModelSimを主にGUIを使いHDLソースコードのコンパイル、シミュレーション、波形確認に至る使い方について説明します。内容はバージョン毎に異なる部分もございますのでご注意下さい。本ブログはModelSimバージョン2021.1をターゲットに記述されていますがmodelSim v6.0以降であれば本ブログをご利用いただけます。本ブログの内容より詳細な情報はツールに付帯するユーザガイドなどをご参照下さい。

本ブログの内容はModelSim Intel Edition, MicroSemi Editionでもご利用頂く事が出来ます。 またModelSimDE/PE/SEやQuestaSimでもご利用可能です。

Modelsimに関する詳細はこちらをご覧ください。

https://www.paltek.co.jp/semiconductor/maker/mentor/modelsim/index.html

ModelSim/Questa エディション比較表はこちらをご覧ください。

https://www.paltek.co.jp/semiconductor/maker/mentor/modelsim_questa/index.html

ブログと同内容を動画でもご覧いただけます。

YouTube動画はChromeまたはFirefoxでご覧ください。

<内容>

- ModelSimシミュレーション実行フロー(0:58)

- ModelSim実行方法(1:39)

- まとめ(9:06)

目次

1.ModelSim シミュレーション実行フロー

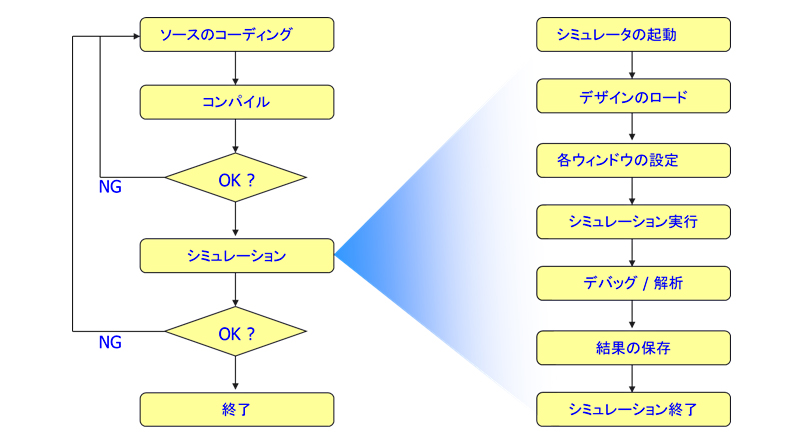

ModelSimのシミュレーション実行フローは、記述されたHDLをコンパイルしてシンタックスチェックを行い内部データベース(デフォルトはworkライブラリ)に取り込みます。その後トップモジュール(通常はテストベンチ)を指定してデザインをロードしシミュレータを起動します。起動後、波形表示や各種設定を行いシミュレーション実行します。さらにシミュレーション後、波形や各種デバッグコマンドを使いデバック作業を行う事ができます。

2.ModelSim 実行方法

2-1. ModelSimの起動

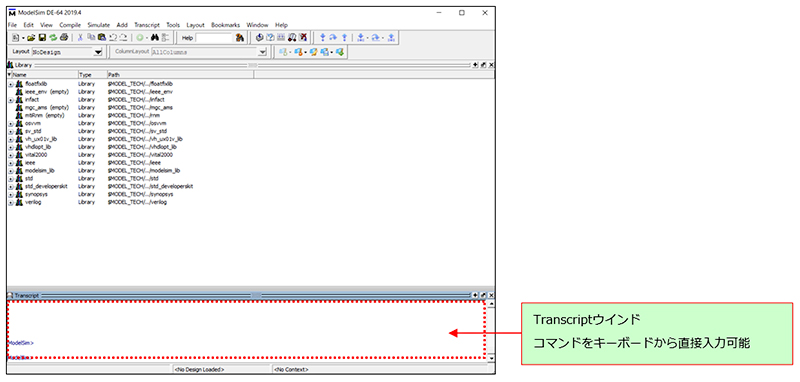

Windows版はデスクトップのアイコンをダブルクリック、またはStartメニューからModelSimDE-64 2021.1 > ModelSim を選択(ModelSimバージョン、エディションにより異なります)して実行します。Linux版はターミナルからvsim コマンドを実行します。画面上にModelSimのメインウインドが表示されます。初期状態のメインウインドにはLibraryウインドとTranscriptウインドが表示されます。初期状態でVHDLのstd/ieeeなどのライブラリは登録されております。

2-2. ライブラリ作成とマッピング

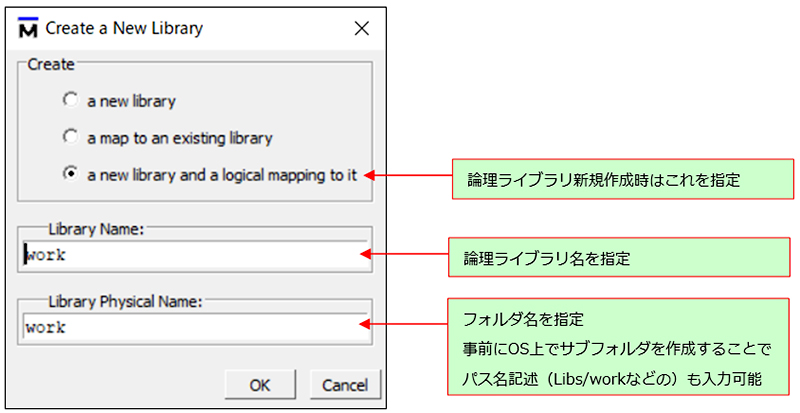

File > New > Library… メニューを選択してライブラリを作成します。このメニューではライブラリの新規作成のみ、既存ライブラリをシミュレーション環境へマッピング、ライブラリ新規作成とマッピングの3種類の処理が実行可能です。

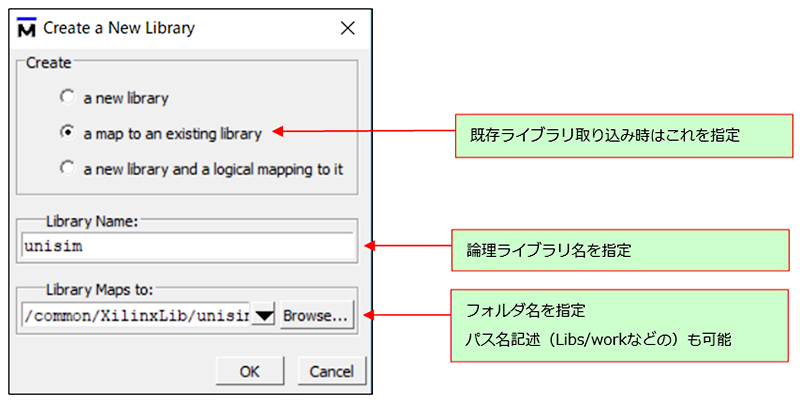

また既存のライブラリ(例えばFPGAベンダライブラリや過去の設計資産など)をシミュレーション環境に取り込む場合にはa map to an existing library を選択し、ライブラリ名、フォルダ名とそのパス名を入力します。

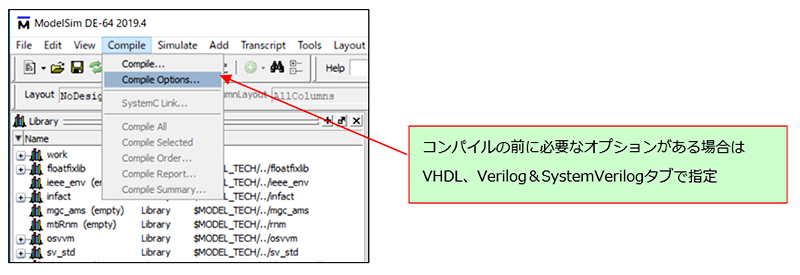

2-3. コンパイルオプション指定

コンパイル時にオプション設定が必要な場合(Verilogの+includeやVHDLの規格87/93/2002/2008など)は、メインメニューのcompile > compile optionsを選択し指定を行います。VHDL、Verilog&SystemVerilogタブで言語毎にオプション設定が可能です。またコンパイルオプションはコンパイル実行前に設定を行って下さい。

2-4. デザインコンパイル

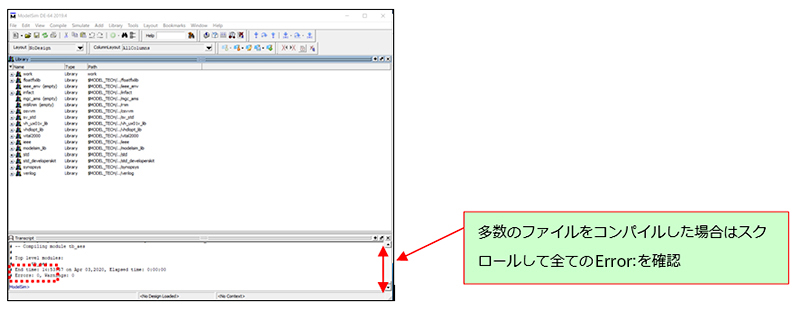

コンパイルオプション設定後コンパイルアイコンを押し、表示されるメニューからコンパイルを行うソースコードを指定します。コンパイル時にHDLの存在するフォルダやコンパイルの保存先(ワーキング・ライブラリ)の指定が可能です。VHDL/Verilog/SystemVerilogの言語はHDL指定時に意識せず全て同時に指定可能です。ファイルタイプ(**.v, **.vhd, **.sv)で自動識別しコンパイルを行います。

全てのコンパイルが問題なく終了したかの確認は、Transcriptウインドに表示される”Error:”のカウントを見て判断します。カウントが”0”の時、コンパイルでエラーが1つも無く次のステップへ進むことが出来る事を意味します。エラーの有無は必ず確認を行ってください。

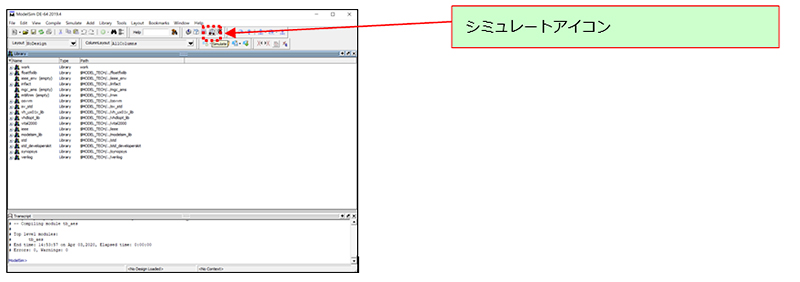

2-5. シミュレータの起動

テストベンチを含め全てのHDLがコンパイル出来たらシミュレータを起動します。シミュレータの起動はシミュレートアイコンを押します。

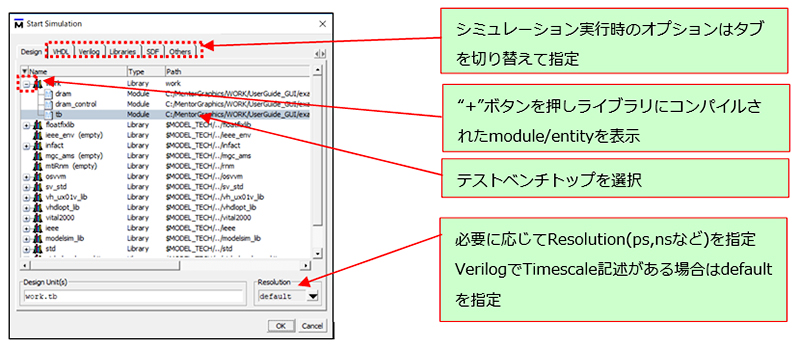

シミュレートアイコンを押すとメニューが表示されますので、テストベンチトップをコンパイルしたワーキング・ライブラリ(以下の例ではworkライブラリ)の”+”ボタンを押し、表示されるmodule/entityの中から指定します。また必要に応じてResolutionでps,nsなどを設定します。その他言語依存のオプション等の指定はタブから設定可能です。

OKボタンを押すとシミュレータが起動します。

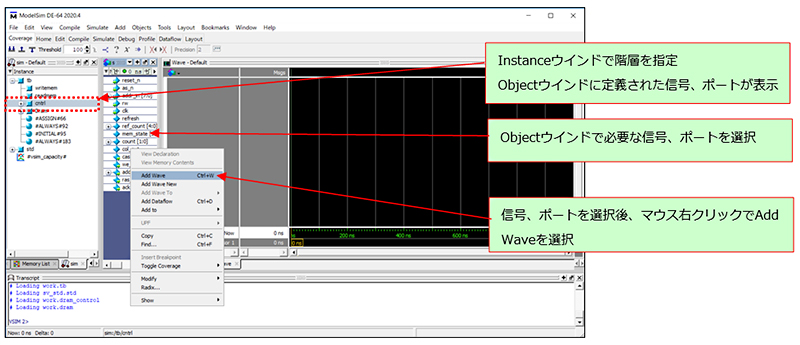

2-6. 波形表示設定

シミュレータが起動したら次に波形観測を行う信号やポートを指定します。指定方法はInstanceウインドで階層を選択します。階層を選択するとその階層に定義された信号やポートがObjectsウインドに表示されます。Objectsウインドで必要な信号を選択しマウス右クリックでadd Waveを選択すると波形ウインドに登録されます。もしObjectsウインドが画面に無い場合はView>Objectsで表示します。

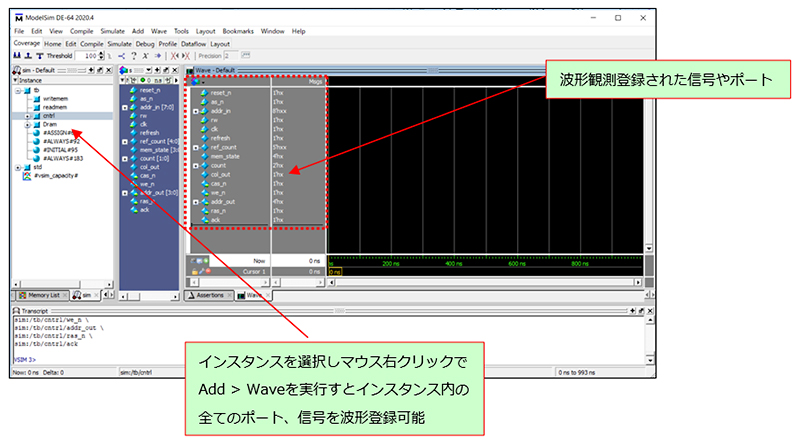

波形観測を行う信号、ポートを指定すると次のように波形ウインドに登録されます。

波形観測の指定はシミュレーション実行前に必ず実行下さい。指定がされていない信号はシミュレーション後に波形観測指定をしても内容を見る事ができません。

2-7. シミュレーション実行

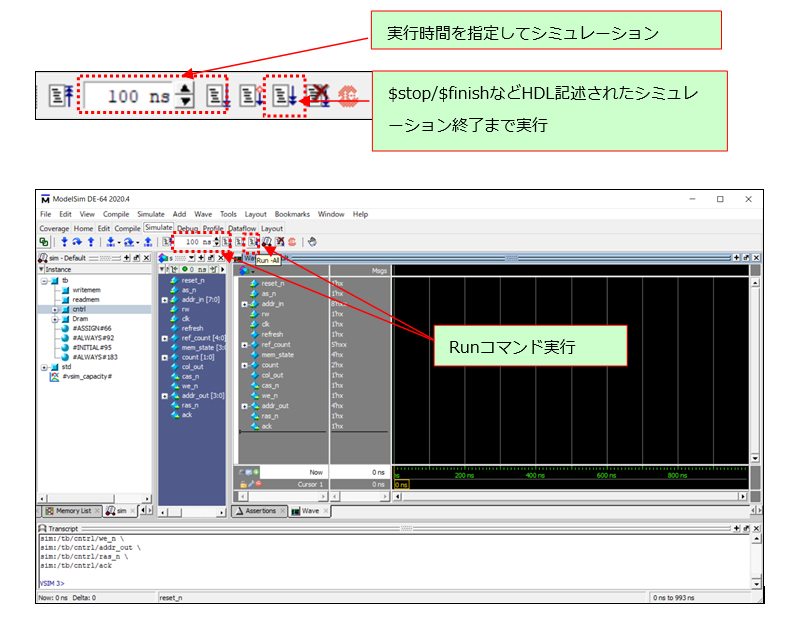

波形観測の指定が終了したらシミュレーションを実行します。実行はrunコマンドアイコンを押します。

runコマンドにはいくつか種類があります。シミュレーション時間(100nsなど)を指定し実行するコマンドやHDLに記述されたシミュレーション終了(Verilog の$stop/$finishやVHDL assertなど)まで実行するコマンドがあります。必要に応じてコマンドを使い分けてください。

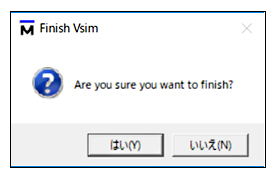

*ご注意: $finishなどでシミュレーションが終了した場合、以下のダイアログが表示されます。

「はい」を押すとGUIを閉じシミュレーションセッション全てを終了してしまいます。

「いいえ」を押すとシミュレーションは終了しますがGUIはそのまま使い続けられます

シミュレーション終了後に波形確認を続けて行いたい場合は「いいえ」を押してください。

-

シミュレーション終了後、波形が表示され確認を行います。$displayなどのプリントはTranscriptウインドにその内容が表示されます。

シミュレーション実行結果はデフォルト設定で波形情報はvsim.wlfファイルに保存され、Transcriptウインドの内容はtranscriptファイルに保存されます。

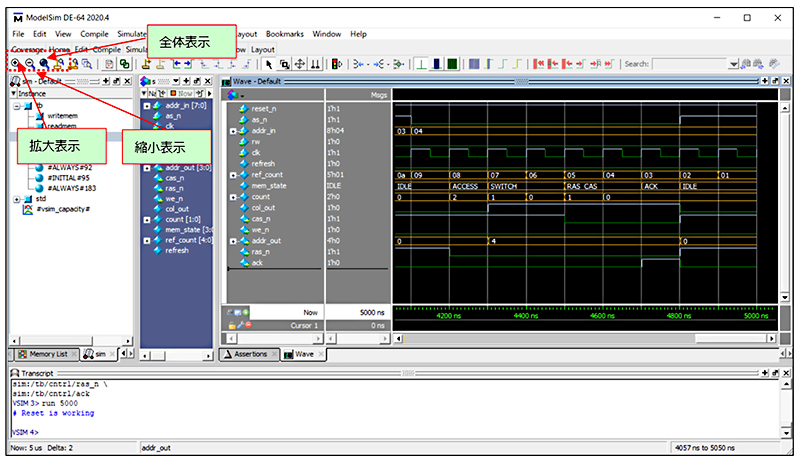

2-8. 波形ウインドの操作

アイコンコマンドで波形表示の拡大、縮小、全体表示を行います。

波形に表示される結果を確認し、不具合が確認された場合はソースコードを修正、コンパイル、シミュレーション、波形確認の作業を繰り返します。

2-9. シミュレーション終了

メインメニューからSimulate→End Simulateを選択しシミュレーションを終了させます。

GUIはそのまま保持され波形確認などが続けて行えます。

ModelSim簡易チュートリアル【GUI編】の

ダウンロードはこちらから

3.さいごに

今回はModelSimを主にGUIを使いHDLソースコードのコンパイル、シミュレーション、波形確認に至る使い方について説明しました。

他にもModelSimをバッチコマンドで、HDLソースコードのコンパイル、シミュレーション、デバッグに至る使い方について説明しているブログもございますので、そちらもご覧ください。

Xilinx社が提供するVivado® プロジェクトで作成された設計データやテストベンチは、Exportコマンドを用いてVivado® 環境外に出力することが可能です。この機能を用いれば、Vivado® 環境外でModelSim/QuestaSimを使用してシミュレーションを実行することができます。

このExport機能を使ったModelSim/QuestaSimシミュレーション実行方法を説明したブログもぜひご覧ください。

Xilinx社Vivado® とModelSimの連携 ~Vivado® Export機能を用いたModelSim/QuestaSimシミュレーション実行方法~

弊社では設計と検証に関する技術や市場動向の情報をご紹介する「Design & Verification LANDSCAPE」という技術ニュースレターを年に3-4回刊行しています。

ご希望の方はニュースレターお申込フォームよりご登録ください。

https://www.paltek.co.jp/design/subscribe_davl_mn/index.html