【FPGAテストベンチ/検証ノウハウ】DDRメモリモデルの初期値設定方法

皆さんこんにちは。

FPGAなどを使用する際にDDRメモリも組み合わせて使用することはございますか。

そのような場合、ロジックを組み立てて動作確認を行う際にDDRメモリと一緒にシミュレーションを行う必要が出てきますよね。

シミュレーションを行うとき、動作開始時にメモリに値を書き込まないとその後の動作が行えない場合もあるかと思います。

実は、Micron社のメモリモデルにはメモリの初期値をあらかじめファイルに設定して読み出すことが可能なものがございます。今回はその方法についてお伝えします。

AMD ザイリンクス社 Vivado® 2020.2 のIP、Memory Interface Generator (MIG) のExample Designと、そこに一緒に出力されるMicron社DDR3メモリモデル「ddr3_model.sv」を使用し、Siemens社 ModelSim® でシミュレーションを行う場合を例に説明をいたします。

なお、Micron社から直接メモリモデルをダウンロードした場合には、ファイル名や内部の記述などが異なる場合がありますのであらかじめご了承ください。

それでは、はじめましょう。

このブログは「FPGA設計ブログ一覧」の

2. シミュレーションのひとつです。

目次

メモリモデルの確認

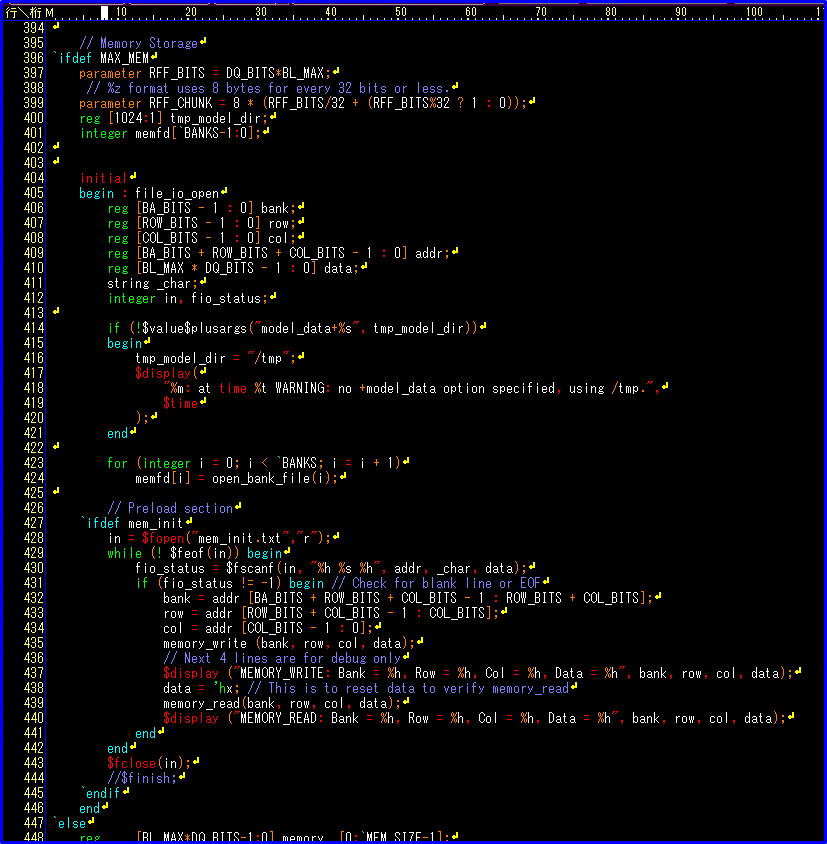

メモリモデル「ddr3_model.sv」の中を見てみましょう。

出典:Micron社 DDR3メモリモデル ddr3_model.sv ファイルより抜粋 (参照 : 2022/12/26)

428行目に 「$fopen("mem_init.txt","r");」とあり、ファイルの読み出しが記述されていることが分かります。

また、396行目と427行目に「ifdef」が記載されているので、両方を有効にすればこのファイル読み出しが実行されることが分かります。

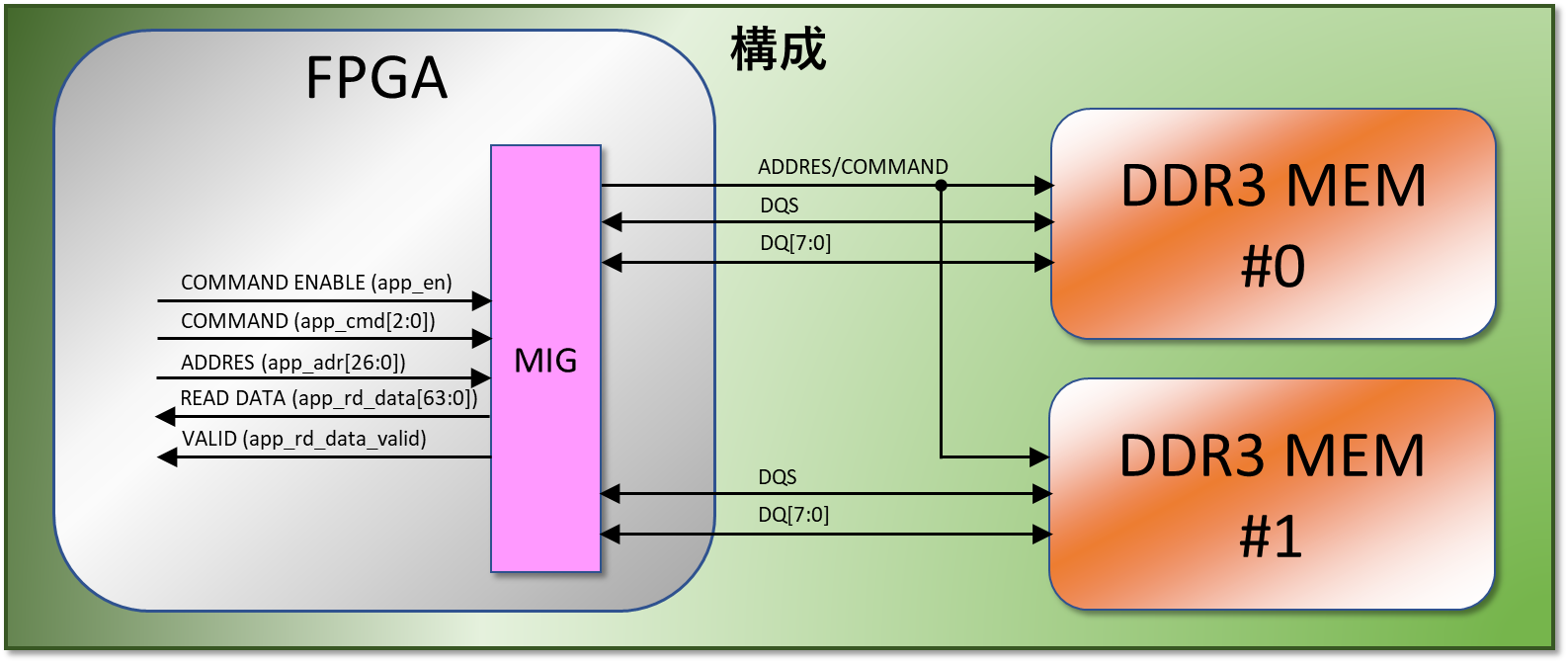

シミュレーション構成

今回の構成はこのようになっています。

MIGのローカル側は、アドレス 27bit、データ 64bitです。

コマンドは 3’b001 がリードで、

コマンド・イネーブルとデータ・バリッドはHigh が有効、バースト・レングスは8です。

DDR3メモリ側は、バンク 3bit、アドレス 14bit(ROW 14bit、COL 10bit)、DQ 8bit です。

これを2個使用します。

メモリの初期値設定

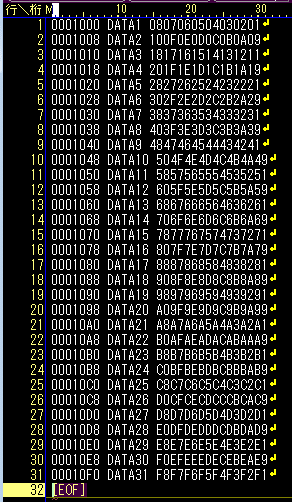

今回使用するメモリモデル428行目に 「$fopen("mem_init.txt","r");」とあるので、初期設定のままファイル名は「mem_init.txt」とします。

ここを書き換えれば任意のファイル名やディレクトリに設定できます。

なお、今回は同じメモリモデルを2個使用するため、両方のメモリモデルから同じ値が読み出されます。

メモリモデル428行目に 「fio_status = $fscanf(in, "%h %s %h", addr, _char, data);」とあるので、

ファイルに設定する内容は「アドレス□メモ□データ」(□は半角スペース)となり、アドレスとデータはヘキサで記載します。

- ※

- このメモリモデルではメモ(_char)の部分は使用されないようです。

アドレス幅はメモリモデル409行目に「reg [BA_BITS + ROW_BITS + COL_BITS - 1 : 0] addr;」とあるので、バンク+ROW+COL の27bit、

データ幅はメモリモデル410行目に「reg [BL_MAX * DQ_BITS - 1 : 0] data;」とあるので、最大バースト・レングス×DQ幅 の64bitになります。

mem_init.txtにアドレス0x000_1000~0x000_10F0 に値を設定した例

今回は、ディレクトリを指定していないため、mem_init.txt はmodelsim.ini と同じディレクトリに置きます。

メモリモデルのコンパイル

この初期値ファイルを使用するには、メモリモデルをコンパイルする際にオプションを設定する必要があります。

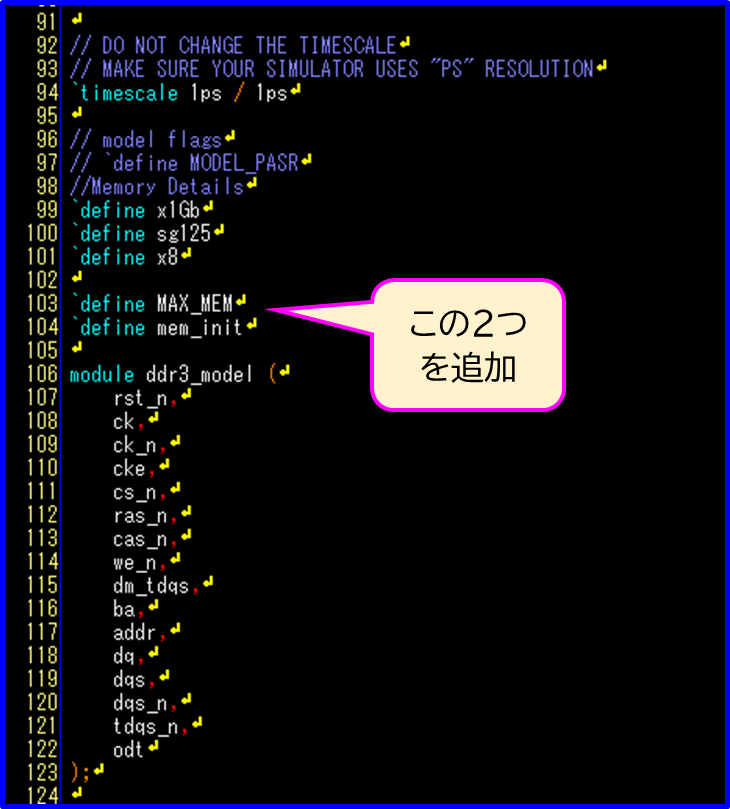

① メモリモデルに「define」を設定

メモリモデルに次の2行を追加してコンパイルします。

`define MAX_MEM

`define mem_init

出典:Micron社 DDR3メモリモデル ddr3_model.sv ファイルより抜粋 (参照 : 2022/12/26)

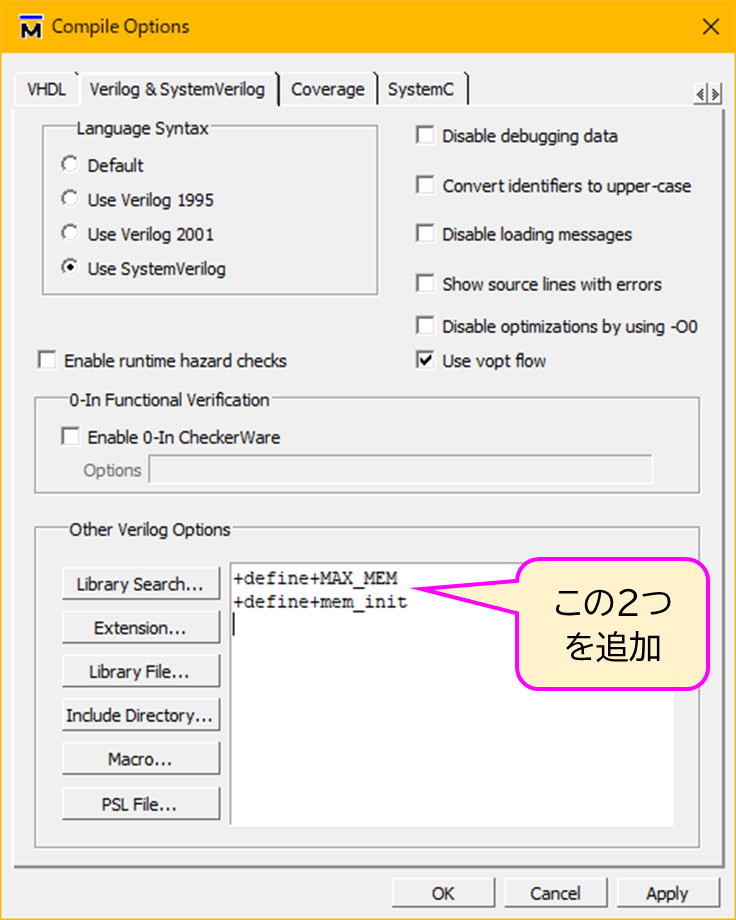

② ModelSim® のコンパイルオプションをGUIで設定

ModelSim® のvelirog のコンパイルオプションに次の2つを設定してコンパイルします。

+define+MAX_MEM

+define+mem_init

出典:ModelSim® SE-64 2021.03 Compile Options画面 (参照 : 2022/12/26)

③ ModelSim® のコンパイルオプションをコマンドに設定する

MIG のExample Designで出力される sim.do 、ここに書かれているメモリモデル「ddr3_model.sv」のコンパイルコマンドに次の2つを追加してsim.do を実行します。

+define+MAX_MEM

+define+mem_init

vlog -sv +define+x1Gb +define+sg125 +define+x8 +define+MAX_MEM +define+mem_init ddr3_model.svシミュレーションの実行

コンパイルが終わりましたらあとはいつも通りシミュレーションを実行します。

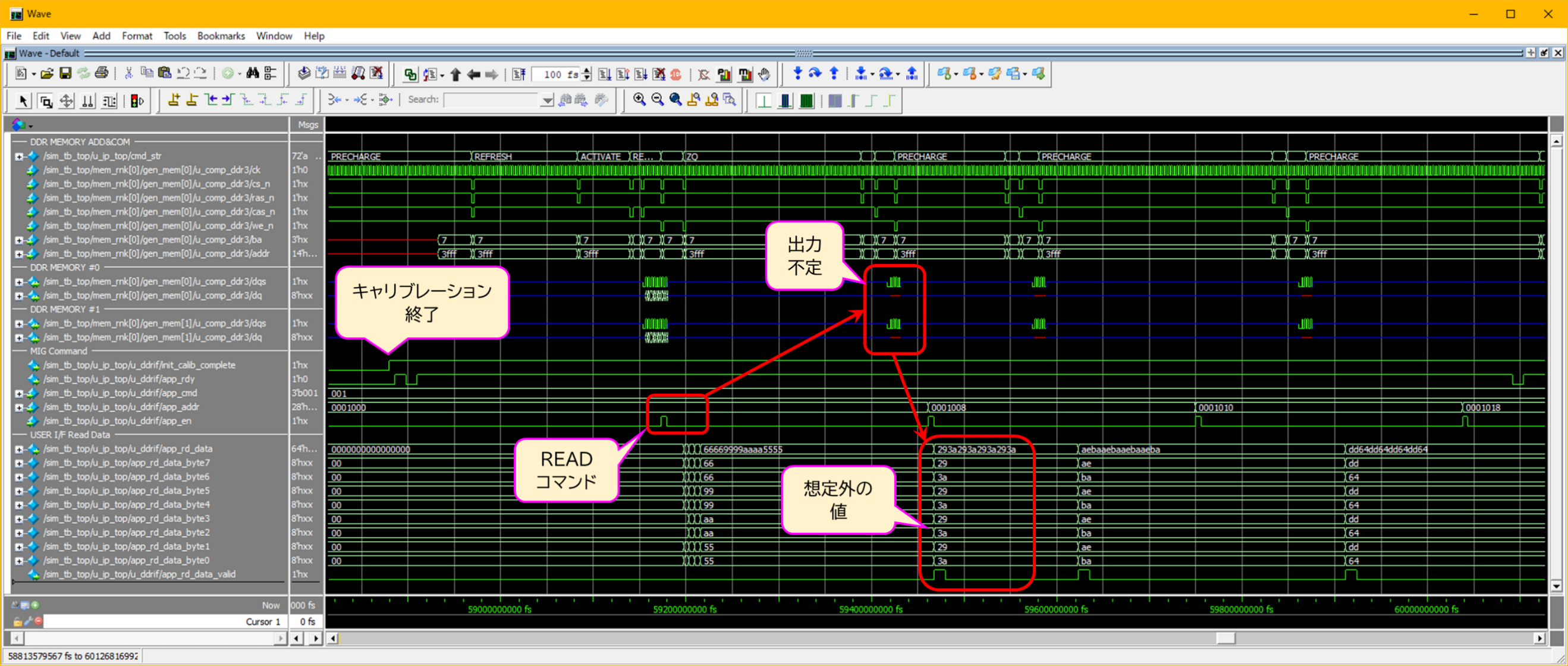

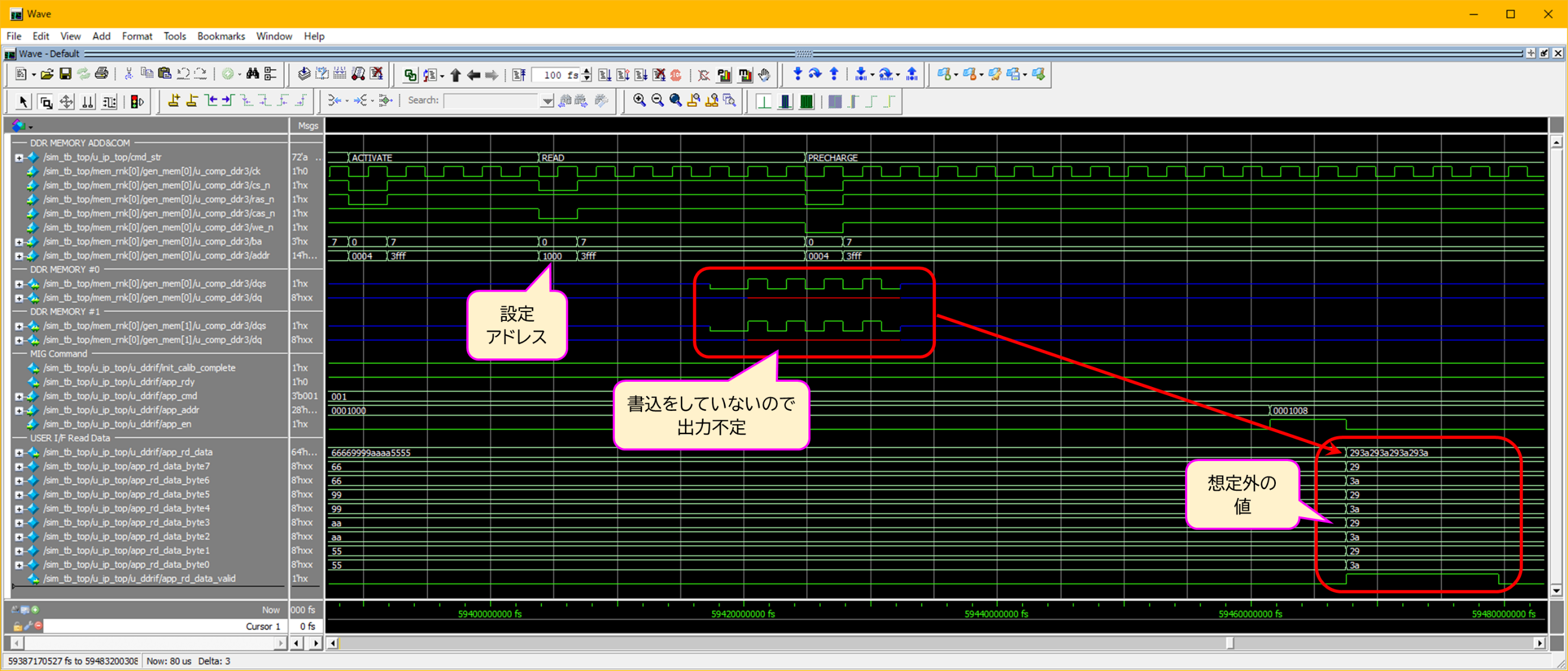

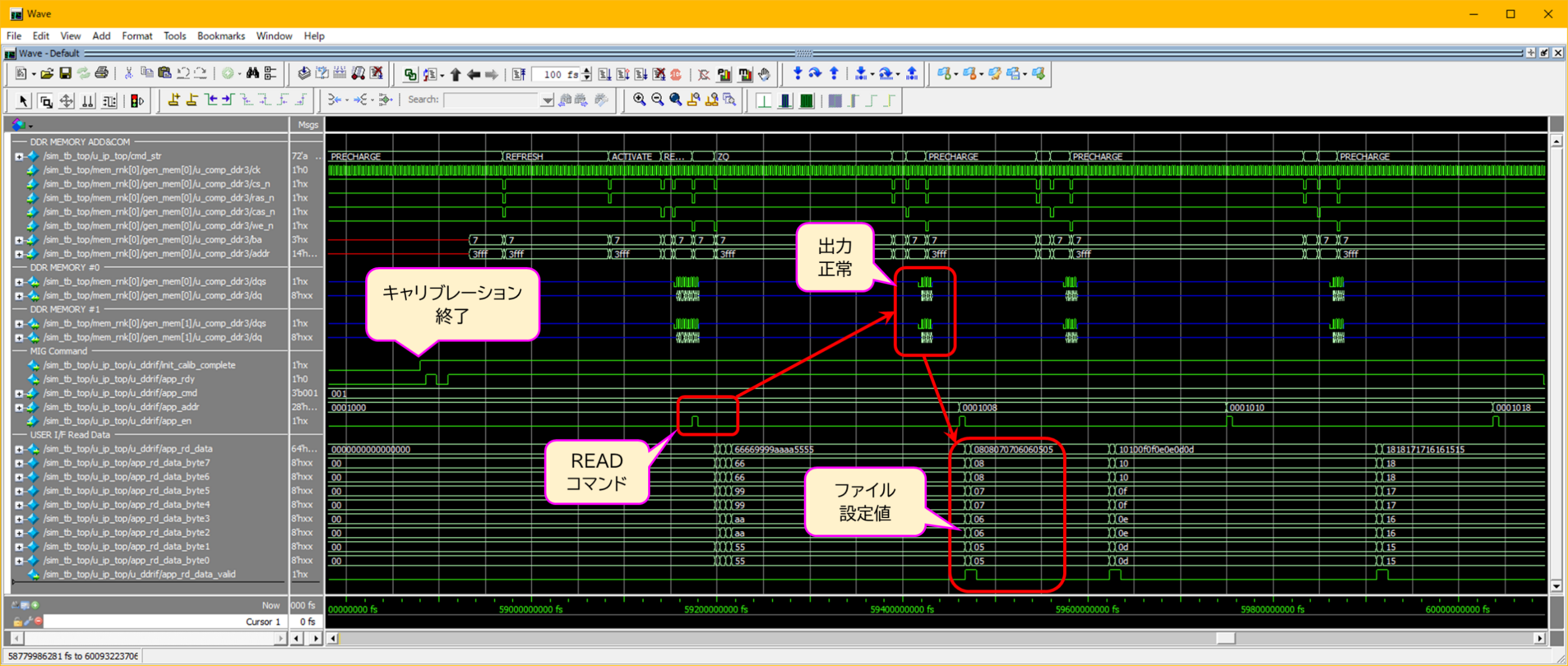

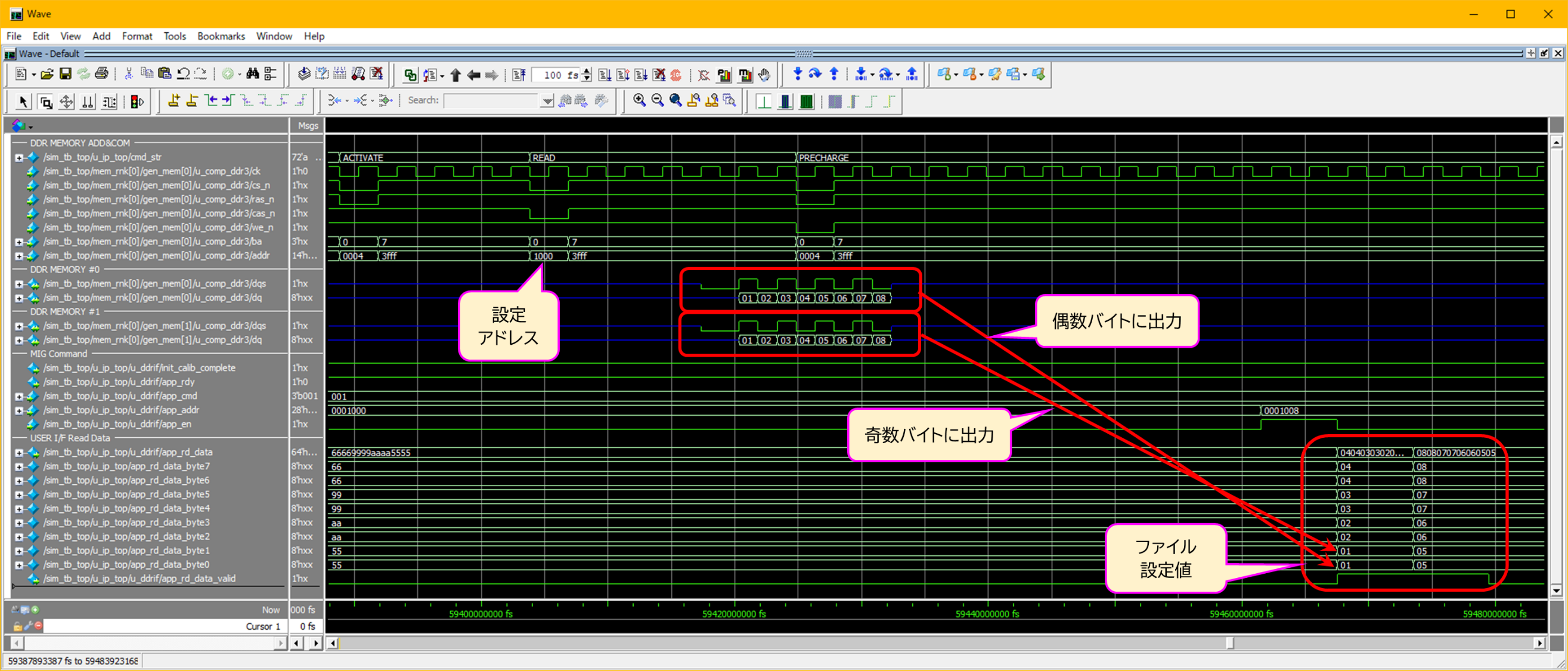

比較のため、初期値設定ファイルの使用・未使用で、キャリブレーションが終了した直後にアドレス0x000_1000 ~ を読み出してみます。

① 初期値設定ファイル未使用 : 全体

出典:ModelSim® SE-64 2021.03 WAVE画面 (参照 : 2022/12/26)

② 初期値設定ファイル未使用 : アドレス0x000_1000アップ

出典:ModelSim® SE-64 2021.03 WAVE画面 (参照 : 2022/12/26)

③ 初期値設定ファイル使用 : 全体

出典:ModelSim® SE-64 2021.03 WAVE画面 (参照 : 2022/12/26)

④ 初期値設定ファイル使用 : アドレス0x000_1000アップ

出典:ModelSim® SE-64 2021.03 WAVE画面 (参照 : 2022/12/26)

いかがでしたでしょうか。

必要な部分に値を設定することで、シミュレーションの一部の工程が省略でき、便利に使用することができるかと思います。

ぜひお試しください。

最後までご覧いただきましてありがとうございました!

これからもブログを通じて、皆様の設計にお役立てできればと思います。

次回のブログもどうぞよろしくお願いいたします。

このブログは「FPGA設計ブログ一覧」の

2. シミュレーションのひとつです。

弊社では各種デバイスの取り扱いやセミナーを行っています。ご興味のある方は下記URLをご覧ください。

ModelSim® セミナー

https://www.paltek.co.jp/techblog/seminar

Micron製品

https://www.paltek.co.jp/semiconductor/maker/micron/index.html

AMD ザイリンクス製品

https://www.paltek.co.jp/semiconductor/maker/xilinx/index.html