【FPGAテストベンチ/検証ノウハウ】シミュレーション豆知識 ~ 文字表示で視認性を高めてみる ~

皆さん、こんにちは。

シミュレーションでは、波形信号のLow/Highや数字を見て動作を確認されていると思います。

単純な動作であればこれらでもよいのですが、複雑になると見てすぐに今の状態を把握するのが難しくなります。

今の状態把握をしやすくするシミュレーションのちょっとしたテクニックとして、動作波形と一緒に文字を表示する方法についてお伝えしたいと思います。

それでは、はじめましょう。

このブログは「FPGA設計ブログ一覧」の

2. シミュレーションのひとつです。

目次

はじめに

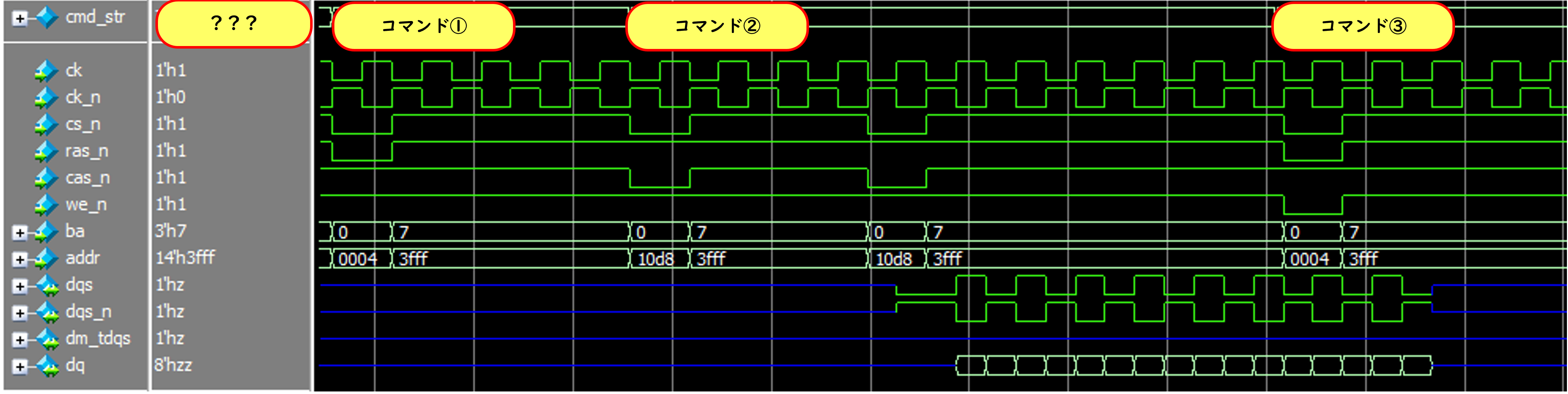

以下の図はDDR3 SDRAMの動作を表示させたものです。

DDRメモリは、チップセレクト(CS)・RAS・CAS・ライトイネーブル(WE)の信号を使ってメモリデバイスにコマンドを発行しますが、この3つのコマンドが何をしているかすぐにわかりますか。

出典:ModelSim® SE-64 2021.03 WAVW画面

もちろん覚えていればすぐに判別がつきますが、IPを使うことが多いと普通は覚えていないことが多いのではないかと思います。

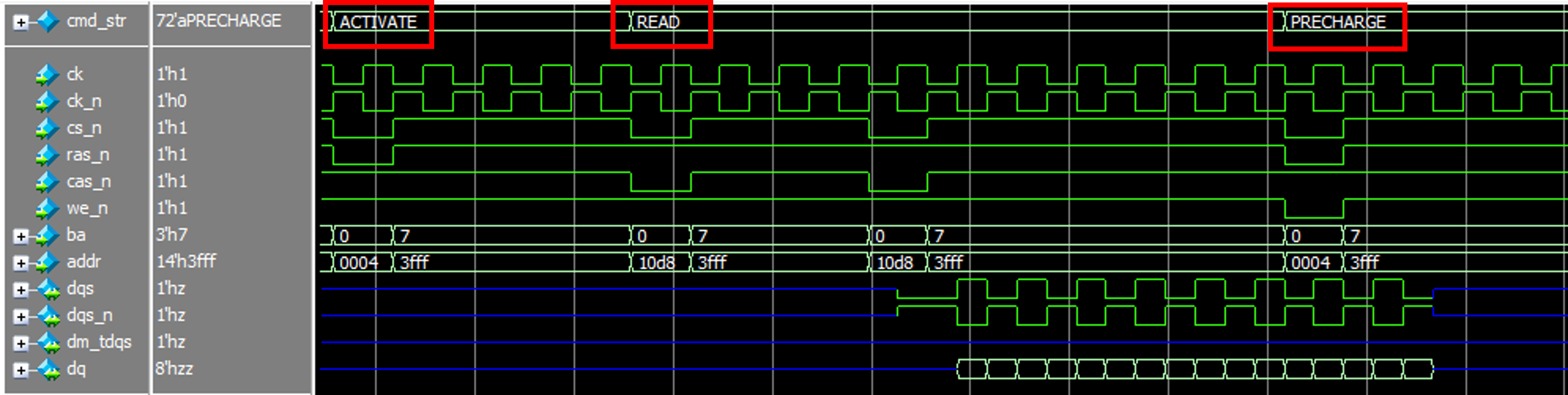

- それでは先ほどのDDR3 SDRAMの動作波形が何をしているかの目隠し部分を取ってみましょう。

(右の「+ボタン」を押してください) -

正解は「ACTIVATE」「READ」「PRECHARGE」でした。

どうでしょうか。わかりやすくなったのではないでしょうか。出典:ModelSim® SE-64 2021.03 WAVW画面

それでは先ほどのDDR3 SDRAMの動作波形が何をしているかの目隠し部分を取ってみましょう。

- 右の「+ボタン」を押してください。

-

正解は「ACTIVATE」「READ」「PRECHARGE」でした。

どうでしょうか。わかりやすくなったのではないでしょうか。出典:ModelSim® SE-64 2021.03 WAVW画面

初めに作ったステートマシーンが機能追加や修正を加えることによりどんどん複雑化し、今どのステートにいるのか把握が難しくなる場合があるかと思います。

このように、どこのステートにいるのかを波形と一緒に文字で表示すれば把握しやすくなります。

文字列をRTLに記述

それではRTLに文字列の表示を追加してみます。

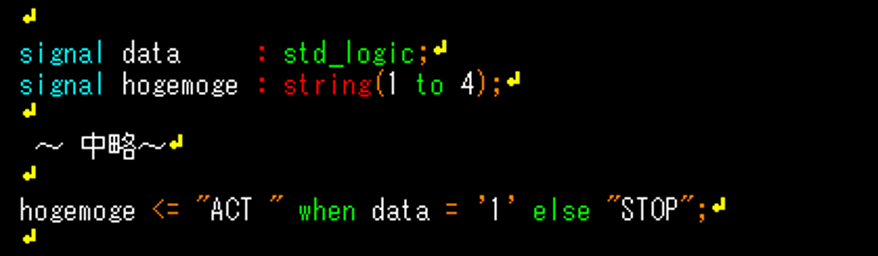

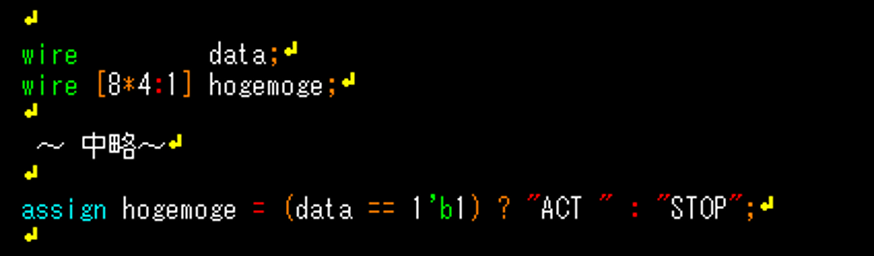

条件として、文字列表示する信号「hogemoge」に、dataがHighの時に"ACT"、Lowの時に"STOP"の文字を表示させます。

ASCII文字・1字を8bitとして、表示する文字の最大数を4文字の場合、次のように記述します。

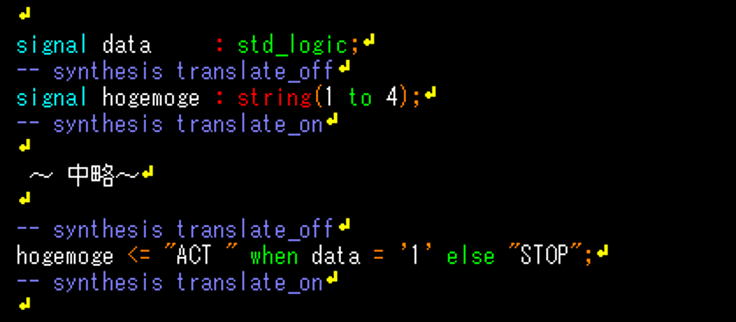

VHDLの場合

※entityやarchitecture等の宣言は省略しています。

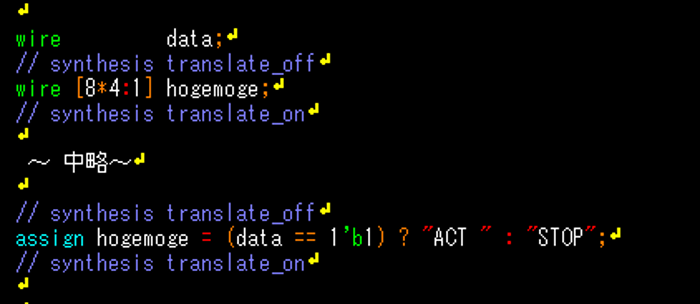

Verilog-HDLでwire型の場合

※reg型でも同じように使用できます。

表示確認

シミュレーションを行い、表示を確認してみましょう。

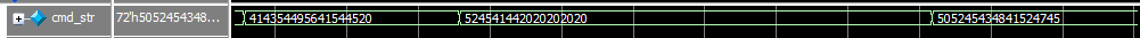

VHDLの場合、文字宣言をしているのであまりないのですが、Verilog-HDL の場合、デフォルトの基数(Radix)で表示されるため文字ではなく以下のように数字で表示されることがあります。

その場合には、文字列で表示をする信号を選択し、基数(Radix)を「ASCII」に変更してください。

出典:ModelSim® SE-64 2021.03 WAVW画面

注意

文字列に関する記述はテストベンチ内では特に問題はありませんが、ソース本体に記述する場合には注意が必要です。

文字列に関する記述は 論理合成ができません 。

そのため、先ほどの記述を以下ように変更する必要があります。

(論理合成ツールによってはサポートしてない場合や、別の記述の場合もあります。)

VHDLの場合

Verilog-HDLの場合

この「synthesis translate_off」から「synthesis translate_on」の記述で囲まれた部分は論理合成で無視されますので、ソースの中にシミュレーション用の記述を記載したままVivado®などのツールで使用することが可能になります。

また、どちらの言語もコメント宣言「 -- (VHDL)」や「// (Verilog-HDL)」で始まっていますが、これらを含めて記述する必要があります。

いかがでしたでしょうか。

いままで見ていた波形に文字が加わることによって視認性が高くなったのではないでしょうか。

最後までご覧いただきましてありがとうございました!

これからもブログを通じて、皆様の設計にお役立てできればと思います。

次回のブログもどうぞよろしくお願いいたします。

このブログは「FPGA設計ブログ一覧」の

2. シミュレーションのひとつです。

弊社では各種デバイスの取り扱いやセミナーを行っています。ご興味のある方は下記URLをご覧ください。

ModelSim® セミナー

https://www.paltek.co.jp/techblog/seminar

AMD製品

https://www.paltek.co.jp/semiconductor/maker/xilinx/index.html

弊社ではFPGA設計や回路図設計、レイアウト設計、ソフトウェア設計、筐体設計などを受託開発しています。サービス内容をWEBサイトに掲載していますので、ぜひご覧ください。

FPGAの活用に際して設計検討などありましたら、お気軽にお問い合わせください。