【FPGAテストベンチ/検証ノウハウ】シミュレーション豆知識 ~ 任意の信号をバス信号にしてみる ~

皆さん、こんにちは。

シミュレーションをしていて波形の表示をわかりやすくしたいと思ったことはありませんか?

ModelSim®やVivado®を使い始めの方にちょっとしたテクニックとして、今回は任意の信号をバス信号にする方法についてお伝えしたいと思います。

それでは、はじめましょう。

このブログは「FPGA設計ブログ一覧」の

2. シミュレーションのひとつです。

目次

はじめに

シミュレーション中に、以下のように思ったことはありませんか。

- バスの中の一部(ビット)の信号だけを取り出して確認したい

- 特定の信号をまとめてバスとして確認したい

など

確認したい信号がわかっていれば、あらかじめRTLの中に記述しておくことができます。

ただ、シミュレーションを実行した後に気づいた場合、特にシミュレーション時間が長くかかる場合には後の祭りで、視認しにくいままシミュレーションの確認を行うことになってしまいます。

このような場合、以下の設定を行うことで、バス信号の特定ビットの動作を把握しやすくなります。

ModelSim®での設定方法

バスになっている信号から任意のビットを取り出すには、バスを展開して必要な波形をコピーします。

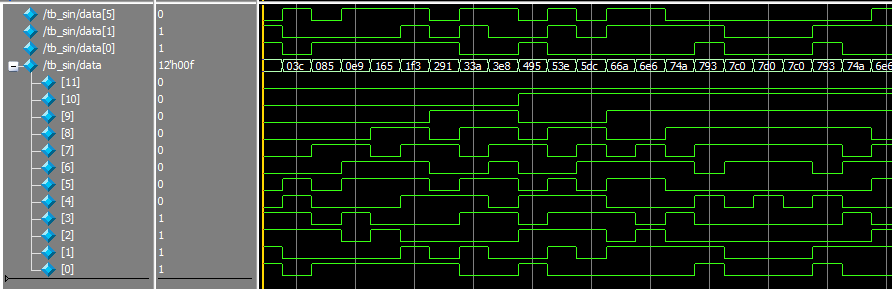

例として、ビットの0,1,5 をコピーします。(画面上部の3つが「data」からコピーした信号です)

出典:ModelSim® SE-64 2021.03 WAVW画面

コピーした信号を束ねる順番に並べます。基本的には上がMSB、下がLSBになります。

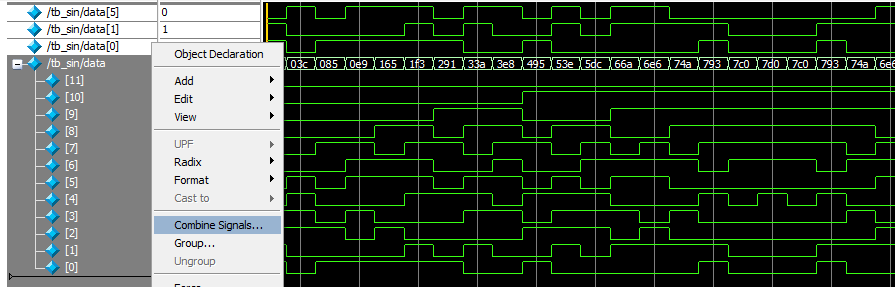

束ねる信号をすべて選択し右クリックし、「Combine Signals」を選択します。

出典:ModelSim® SE-64 2021.03 WAVW画面

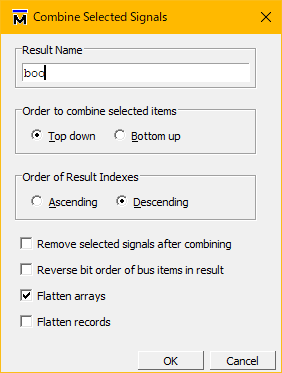

束ねた信号に名前「boo」を付け、必要があればオプションを設定します。

出典:ModelSim® SE-64 2021.03 Combine Selected Signals 設定画面

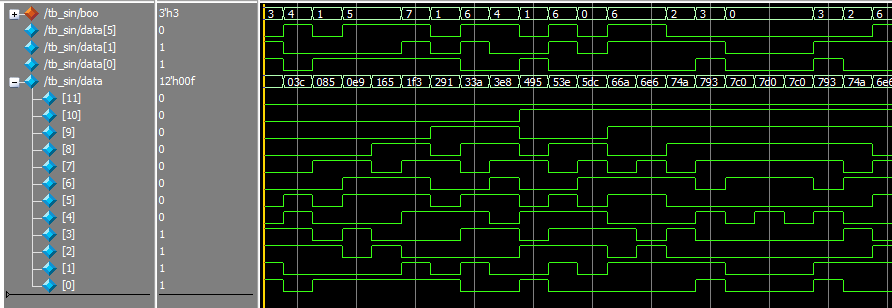

一番上の信号「boo」が、新たに作成したバス信号になります。

出典:ModelSim® SE-64 2021.03 WAVW画面

Vivado®での設定方法

バスになっている信号から任意のビットを取り出すには、バスを展開して必要な波形をコピーします。

例として、ビットの0,1,5 をコピーします。(画面上部の3つが「data」からコピーした信号です)

出典:Vivado® 2020.2 シミュレーション画面

コピーした信号を束ねる順番に並べます。基本的には上がMSB、下がLSBになります。

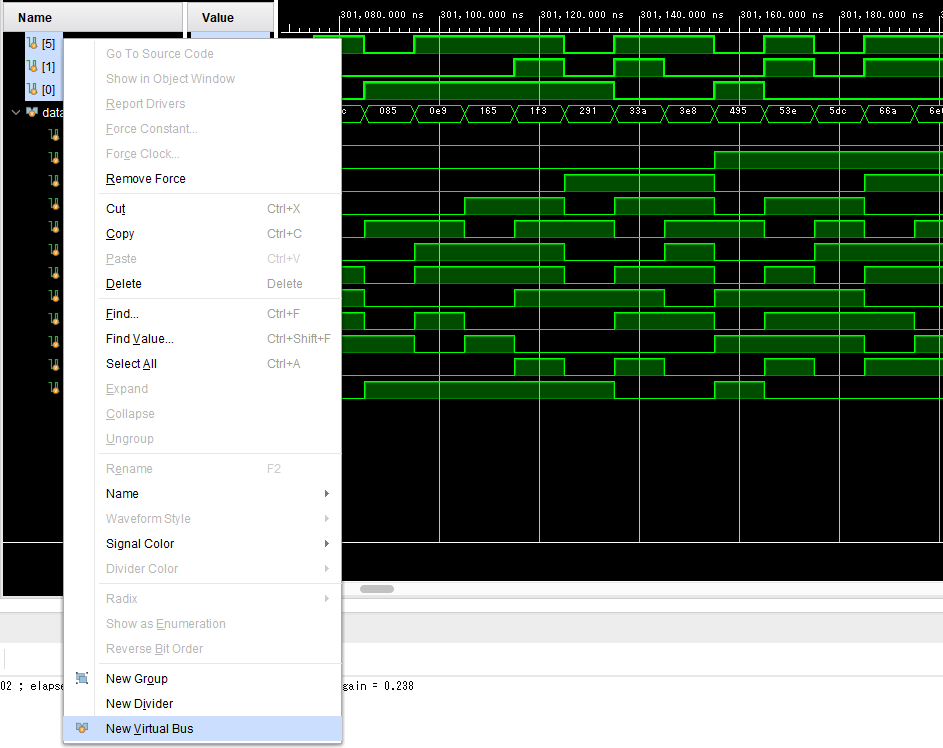

束ねる信号をすべて選択し右クリックし、「New Virtual Bus」を選択します。

出典:Vivado® 2020.2 シミュレーション画面

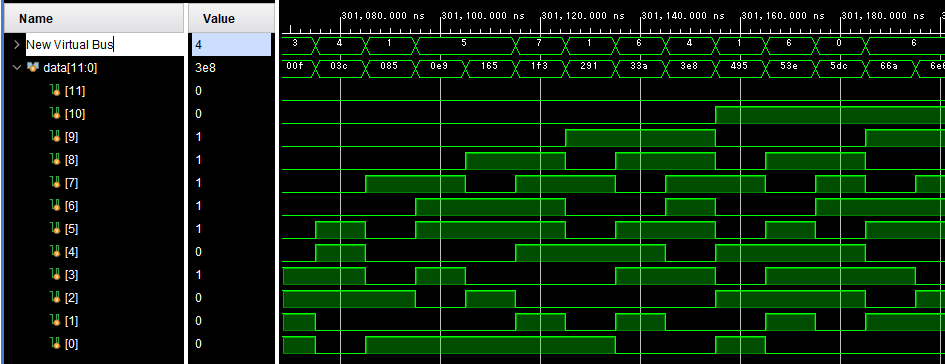

束ねた信号に名前「boo」を付けます。

出典:Vivado® 2020.2 シミュレーション画面

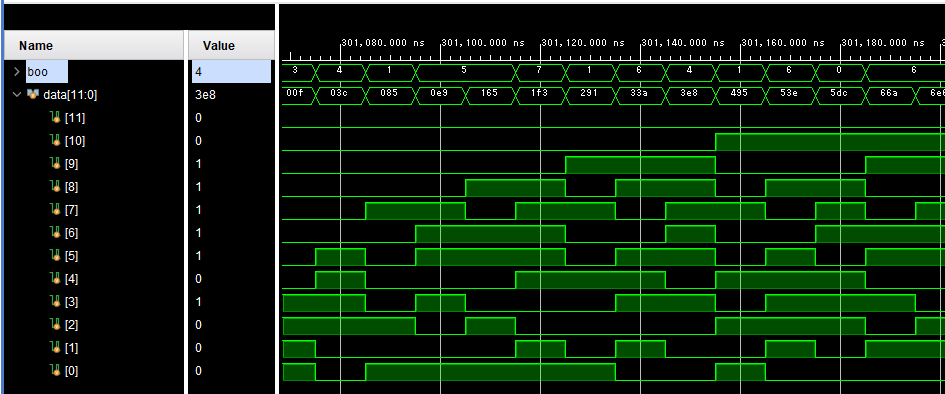

一番上の信号「boo」が、新たに作成したバス信号になります。

出典:Vivado® 2020.2 シミュレーション画面

この方法はシミュレーション以外にアナライザの表示波形でも行うことができます。

いかがでしょうか。

シミュレーション後でも任意のバス信号が作成できて、認識がしやすくなったかと思います。

最後までご覧いただきましてありがとうございました!

これからもブログを通じて、皆様の設計にお役立てできればと思います。

次回のブログもどうぞよろしくお願いいたします。

このブログは「FPGA設計ブログ一覧」の

2. シミュレーションのひとつです。

弊社では各種デバイスの取り扱いやセミナーを行っています。ご興味のある方は下記URLをご覧ください。

ModelSim® セミナー

https://www.paltek.co.jp/techblog/seminar

AMD製品

https://www.paltek.co.jp/semiconductor/maker/xilinx/index.html