【入門】ModelSimの使い方 <バッチスクリプト実行> ~ModelSim 2021.1 ModelSim Intel Edition, Microsemi Edition, ModelSim DE/PE/SE, QuestaSim対応版 ~

当ブログは、保守契約者様向け「ModelSimウェビナー ~ バッチ実行編 ~」より一部抜粋してお伝えしております。

ModelSimを使い始めたけど日本語マニュアルがなくて困ることありませんか?

本ブログではModelSimをバッチコマンドで、HDLソースコードのコンパイル、シミュレーション、デバッグに至る使い方について説明します。内容はバージョン毎に異なる部分もございますのでご注意下さい。本ブログはModelSimバージョン2021.1をターゲットに記述されていますがModelSim v6.0以降であれば本ブログを参考にしていただけます。本ブログの内容より詳細な情報はツールに付帯するユーザガイドなどをご参照下さい。

本ブログの内容はModelSim Intel Edition, MicroSemi Editionでもご利用いただく事が出来ます。

またModelSimDE/PE/SEやQuestaSimでもご利用可能です。

Modelsimに関する詳細はこちらをご覧ください。 https://www.paltek.co.jp/semiconductor/maker/mentor/modelsim/index.html

ModelSim/Questa エディション比較表はこちらをご覧ください。

https://www.paltek.co.jp/semiconductor/maker/mentor/modelsim_questa/index.html

ブログと同内容を動画でもご覧いただけます。

YouTube動画はChromeまたはFirefoxでご覧ください。

<内容>

- ModelSimシミュレーション実行フロー(1:10)

- ModelSimバッチ実行(1:55)

- まとめ(12:45)

目次

1.ModelSim シュミレーション実行フロー

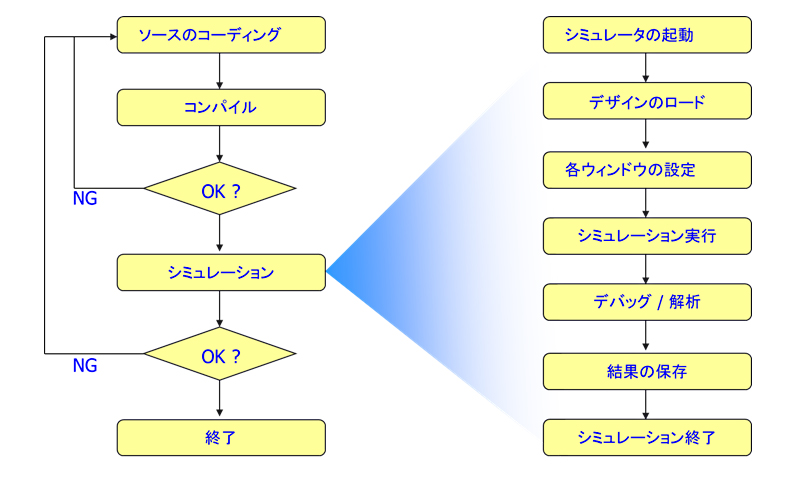

ModelSimのシミュレーション実行フローは、記述されたHDLをコンパイルしてシンタックスチェックを行い内部データベース(デフォルトはworkライブラリ)に取り込みます。その後トップモジュール(通常はテストベンチ)を指定してデザインをロードしシミュレータを起動します。起動後、波形表示や各種設定を行いシミュレーション実行します。さらにシミュレーション後、波形や各種デバッグコマンドを使いデバック作業を行う事ができます。

2.ModelSimバッチ実行

ModelSimはGUI実行のみならずバッチで実行することもできます。バッチ実行ファイルを記述することで同じ操作を間違えなく実行でき、HDL修正後に全てのテストを1つのコマンド(バッチファイル)で実行することもできます。またWindows、Linux共に同じバッチコマンドが扱えます。

2.1.ライブラリ作成とマッピング

ライブラリ作成はvlibコマンドで実行します。vlibコマンドの後にフォルダ名(ディレクトリフォルダ名)を入力します。

- vlib work

mkdir user_lib(またはWindowsエクスプローラでサブフォルダ作成)

vlib user_lib/my_lib

ライブラリは必ずvlibコマンドで作成します。Windowsエクスプローラで作成したり、linuxのmkdirコマンドで作成したりすることはできません。上記のようにサブフォルダ(user_lib)はWindowsエクスプローラ等で作成してください。

vlibコマンド実行後、マッピング処理を行います。vlibコマンドで作成したライブラリをvmapコマンドで論理ライブラリ名にマッピングします。論理ライブラリ名はVHDLのライブラリ名と同じにします。Verilogはライブラリ概念が有りませんので通常はworkライブラリのみで問題有りません。

- vmap work work

vmap my_lib user_lib/my_lib

vmapコマンドを初めて実行するとカレントフォルダにmodelsim.iniファイルが作成されvmapで実行されたマッピング情報が保存されます。次回以降のvmapではこのmodelsim.iniに情報が追記されます。

2.2.コンパイル

ライブラリ作成とマッピングが終了したらコンパイルを行います。コンパイルにはverilog/vhdlそれぞれコンパイルコマンドが有り、言語により使い分けて下さい。コンパイル時に発生したエラーはその都度修正を行い、再度コンパイルを行います。

2.2.1.verilog用コンパイルコマンド

Verilogソースファイルはvlogコマンドを使いコンパイルを行います。

- vlog module1.v

一般的なファイルリストも利用も可能です。”-f”, “-F”オプションを用いてファイルリストを指定します。大量のファイルが記述されたファイルリストを使ってコンパイルする場合には”-l”オプションでログファイルを生成することも可能です。コンパイル終了後にログファイルを確認しエラーが出ていないか確認します。

- vlog -f filelist -l compile.log

コンパイル時に”-work”オプションでワーキング・ライブラリを指定することも可能です。ワーキング・ライブラリが省略された場合はデフォルトのworkライブラリにコンパイルされます。

- vlog -work my_lib my_src.v

Verilogの規格(95/2001/systemverilog)もオプション指定が可能です。デフォルトはVerilog-2001となります。

- vlog -vlog95compat v95.v

vlog -vlog01compat v2k.v

vlog -sv systemver.v

ファイルタイプが.sv (例systemver.sv)の場合はSystemVerilogとして認識されますので-svオプションを省略することも可能です。

その他のオプションとして、Verilog標準のコマンドオプション -v, -y, +define, +incdir なども利用可能です。また-timescaleオプションでコンパイル時にtimescaleの設定を行う事も可能です。

- vlog -timescale 1ns/1ps mod1.v +incdir+../include/ -v gate_cell.v -y ../common/ -f filelist ......

2.2.2.VHDL用コンパイルコマンド

VHDLソースファイルはvcomコマンドを使いコンパイルを行います。

- vcom entity1.vhd

一般的なファイルリストも利用も可能です。”-f”, “-F”オプションを用いてファイルリストを指定します。大量のファイルが記述されたファイルリストを使ってコンパイルする場合には”-l”オプションでログファイルを生成することも可能です。コンパイル終了後にログファイルを確認しエラーが出ていないか確認します。

- vcom -f filelist -l compile.log

コンパイル時に”-work”オプションでワーキング・ライブラリを指定することも可能です。ワーキング・ライブラリが省略された場合はデフォルトのworkライブラリにコンパイルされます。

- vcom -work my_lib my_pack.vhd

VHDLの規格(87/93/2002/2008)もオプション指定が可能です。デフォルトはVHDL-2002となります。

- vcom -87 vhd87.vhd

vcom -97 vhd97.vhd

vcom -2002 vhd2002.vhd

vcom -2008 vhd2008.vhd

その他のオプションとして、”-autoorder” オプションを指定するとVHDLのコンパイルオーダーを自動で処理することが可能です。

- vcom -autoorder entity1.vhd pack1.vhd -f filelist.f ......

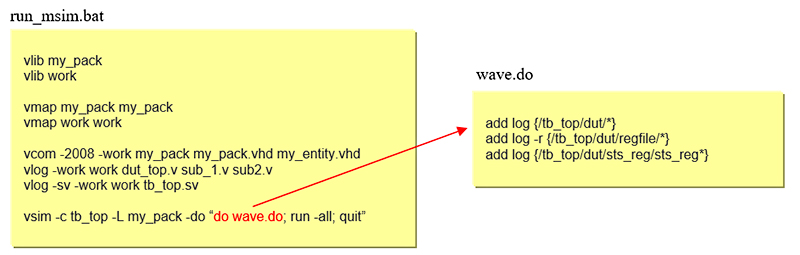

2.3.波形観測設定

コンパイルがエラー無く終了した場合、シミュレーション実行が可能となります。シミュレーション実行後に波形確認がしたい場合は波形観測の指定が事前に必要です。波形観測には”add log”コマンドを使用します。”add log”コマンドで波形観測を行いたいポートや信号を階層表記付きで”{ }”で囲い指定します。ポートや信号指定には”*”ワイルドカードも利用可能です。”add log”コマンドはシミュレータ起動後のコマンドになるので通常wave.doファイルなどに記述しシミュレータ起動コマンドの-doオプションで指定します。

- **wave.doファイル等に以下のようなadd logコマンド記述**

add log {/tb_top/dut/sub1/clk}

add log {/tb_top/dut/sub1/data_a_*}

add log {/tb_top/dut/*}

add log -r {/tb_top/dut/sub2/tx_blk/*}

** “-r” はリカーシブ指定となり指定階層以下全てのポート、信号が対象になります。むやみに多くの信号やポートを指定するとシミュレーションが遅くなる恐れがございますのでご注意下さい。

2.4.シミュレータの起動

波形観測の準備が終わったらシミュレータを起動し実行を行います。シミュレータの起動コマンドは”vsim -c”となります。”-c”がバッチモードの実行を意味します。”-c”を付けずに”vsim”とだけ入力するとGUIが起動します。 “vsim -c”の後にローディングモジュール(通常テストベンチのトップモジュールまたはエンティティ)をライブラリ名付きで指定します。”-do”オプションでシミュレータ起動後のコマンド(波形観測指定のadd logなど)を記述したファイルを指定します。

- シミュレーション実行を時間指定でする場合:

vsim -c work.tb_top -do “do wave.do; run 10ms; quit;”

HDLに記述された$finishまで実行する場合:

vsim -c work.tb_top -do “do wave.do; run -all; quit;”

“-do”の後に” … ”(ダブルコーテーション)で囲われた中にコマンドを記述します。直にコマンド記述することも可能です。

- vsim -c work.tb_top -do “add log {/tb_top/dut/*}; run 10ms; quit;”

ファイルに記述されたコマンドを実行する場合には”…”の中で”do ファイル名.do”と指定します。

- vsim.doに以下を記述

add log {/tb_top/dut/*}

run 10ms;

quit;

vsim -c -do “do sim.do”

複数のライブラリを用いて構築されたデザインはシミュレータ起動時に”-L”でローディング・ライブラリの指定が必要な場合があります。コマンドは以下のように記述します。

- vsim -c work.tb_top -L my_lib -L my_pack -L FPGA_Lib ….

2.5.バッチ実行スクリプト例

以下バッチ実行スクリプトの例となります。***.batファイルとシミュレータ起動後のコマンドをまとめた***.doの2ファイル構成で記述を行っています。

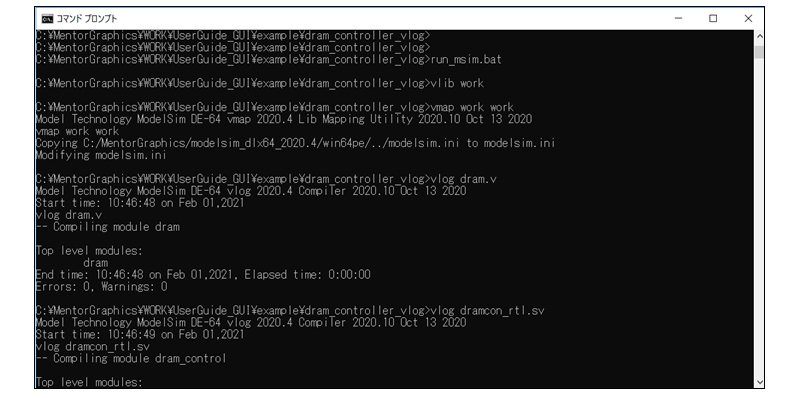

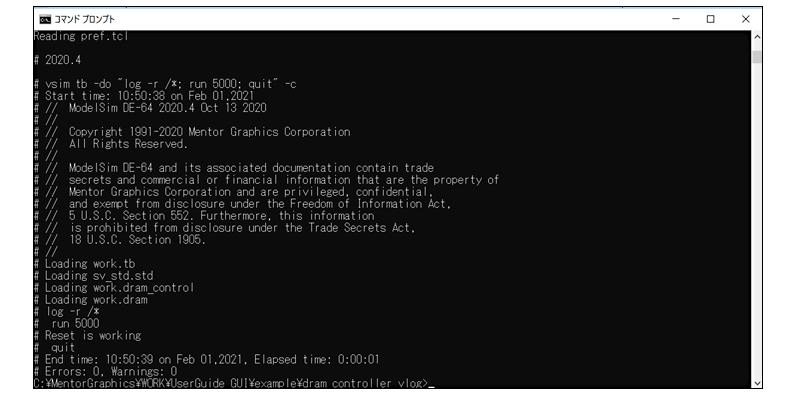

2.6.バッチスクリプト実行

バッチスクリプトが完成したらWindowsのコマンドプロンプトからバッチスクリプト”run_msim.bat”を実行します。また同じスクリプトをModelSim GUIを起動しTranscriptウインドからdo run_msin.batのように入力する事でGUIからも利用可能です。

: 実行が続きます。

2.7.波形ビュアでの確認

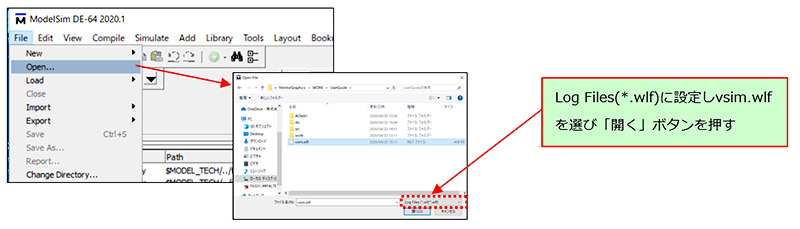

バッチ実行が終了すると波形観測指定が行われていればバッチスクリプト実行フォルダに波形ファイルvsim.wlfが生成されています。波形ファイルはModelSimをデスクトップのアイコンダブルクリック、またはWindowsスタートメニュー > ModelsimDE-64 2021.1 > MdeolSim 等で起動し、File > Open メニューでダイアログを表示しファイルタイプをLog Files(*.wlf)に設定しvsim.wlfファイルを開くことで内容を表示できます。

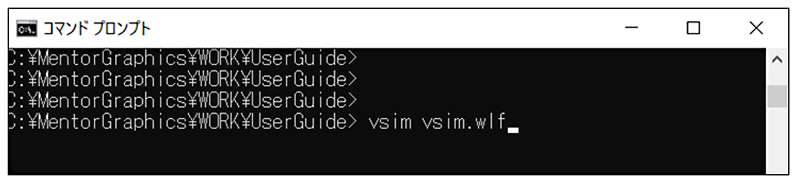

または、Windowsのコマンドプロンプトから”vsim vsim.wlf” コマンドでGUIを起動します。Run_msim.batにGUI起動コマンド(vsim vsim.wlf)を記述することで、シミュレーション終了直後にGUIを起動し波形表示を行う事も可能です。

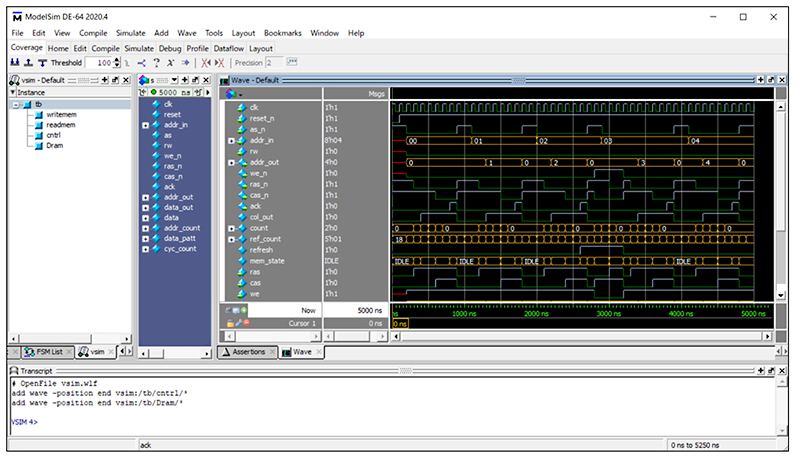

GUIが起動し波形確認が行えます。通常GUIで実行する場合には全ての階層が階層ブラウザに表示されますが、バッチ実行後は波形観測が指定された階層のみ表示されますのでご注意ください。波形表示は階層ブラウザでインスタンスを指定し、Objectウインドに表示された信号やポートを選択しマウス右クリックでAdd>Waveを実行します。Objectウインドが画面に無い場合にはView>Objectで表示します。同様に波形ウインドが表示されていない場合はView>Waveで表示します。

3.さいごに

今回はModelSimをバッチコマンドで、HDLソースコードのコンパイル、シミュレーション、デバッグに至る使い方について説明しました。

今回説明したバッチコマンド、ならびにコマンドオプションはごく一部です。その他のコマンドやコマンドオプションは以下の資料にまとめましたので必要な方はダウンロードください。

ModelSimコマンドオプション一覧表の

ダウンロードはこちら

その他、ModelSimを主にGUIを使いHDLソースコードのコンパイル、シミュレーション、波形確認に至る使い方について説明しているブログもございますので、こちらもご覧ください。

Xilinx社が提供するVivado® プロジェクトで作成された設計データやテストベンチは、Exportコマンドを用いてVivado® 環境外に出力することが可能です。この機能を用いれば、Vivado® 環境外でModelSim/QuestaSimを使用してシミュレーションを実行することができます。

このExport機能を使ったModelSim/QuestaSimシミュレーション実行方法を説明したブログもぜひご覧ください。

Xilinx社Vivado® とModelSimの連携 ~Vivado® Export機能を用いた ModelSim/QuestaSim シミュレーション実行方法~

弊社では設計と検証に関する技術や市場動向の情報をご紹介する「Design & Verification LANDSCAPE」という技術ニュースレターを年に3-4回刊行しています。

ご希望の方はニュースレターお申込フォームよりご登録ください。

https://www.paltek.co.jp/design/subscribe_davl_mn/index.html