仕様書がない/RTLや回路図しか存在しない場合の置き換えサービス

皆さんこんにちは。

本ブログでは、『仕様書がない、RTLしか存在しない場合の置き換えサービス』について紹介します。

既存製品の設計資産(CPLDやFPGA)を流用したいのにRTLしかない場合や、仕様書がプアで変更ができない場合、皆さんはどうされていますでしょうか?

例えば、実際に設計資産として残っていて使用している場合において、不具合が発生してクレームを受けた際に、設計担当者が既に退職していたりする場合にどう解決したらよいのでしょうか?

本ブログは、このように設計資産の扱いに悩んでいる方々に朗報なブログです。

弊社パートナー企業であるCMエンジニアリング株式会社(以降、CMエンジニアリング)のサービスの中で、このようなお悩みに対してサービス展開がありますので紹介します。

目次

なぜ仕様書が重要なのか

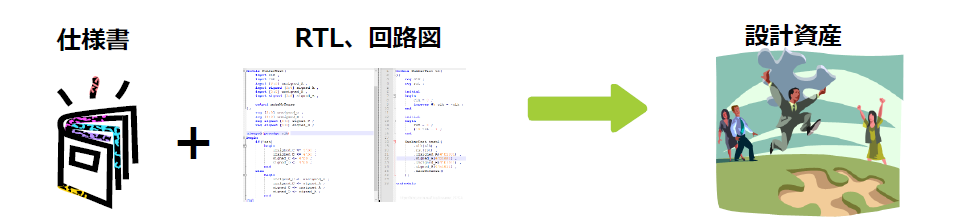

設計資産を活用する際に一番重要なのが仕様書です。

では、なぜ仕様書が一番重要なのでしょうか。

まず1つ目の理由は、回路の大規模化や短TAT(Turn Around Time)化により、複数の担当者やチームでの並列作業が必要となるためです。

大規模な設計となりますと、設計・検証の階層化により担当作業の細分化が必要となることに加え、チーム間の齟齬(そご)をなくしたいということになると、設計資産の重要性が増大=”仕様書”が重要と言えるでしょう。

2つ目の理由としては人材の流動化です。

仕様を理解している方が異動、退職などでいなくなるリスクや、会社の合併などにともない、設計文化の異なるメンバーでのチーム構成が必要になることに加え、外部リソースの活用(アウトソース化)が普及してきていることを考えると、ますます仕様書の重要性が高まっていることをお分かりいただけるのではないでしょうか。

ご存じの通り、設計資産を実際に活用する場合、RTLや回路図、デザインだけではなく、そこには必ず仕様書がセットになっていないと、設計資産として再利用することが難しくなってしまい、設計資産としての価値がなくなってしまいます。

図1 設計資産の考え方

(出典:CMエンジニアリング株式会社)

ここまでの説明を踏まえて、弊社パートナー企業であるCMエンジニアリングではどのようなサービスを展開しているのかについてお話しします。

CMエンジニアリングのサービスについて

| CMエンジニアリング株式会社の概要 | |

| 設立 | :2010年3月 |

| 拠点 | :本社(東京都品川区)、福岡開発センター(福岡県福岡市) |

| 事業内容 | :無線・FPGA/SoC開発サービス、OFDM/ITS関連サービス |

CMエンジニアリングでは、RTLや回路図などの既存のレガシーコードからIPの仕様書を作成、そのIPの品質のチェックしたうえで、最終的に再利用可能なIPへカスタイマイズを行う、という工程のサービスを提供しています。

| 1.レガシーコードからIPの仕様書作成 | |

| 2.IPの品質チェック | |

| 3.再利用可能なIPへカスタマイズ |

1.レガシーコードからIPの仕様書作成

RTLや回路図をもとにIPの仕様書を作成します。

その仕様書は入出力端子表や回路構成図、階層構成図、クロック系統図だけでなく、制御フローや動作フロー図、タイミングチャートを含めた仕様書に必要なものを作成します。

RTL/回路図

↓

- 入出力端子表

- 回路構造図、階層構成図、クロック系統図等

- 制御フロー、動作フロー図

- タイミングチャート

2.IPの品質チェック

IPを再利用するという意味では、資産自体の品質のチェックすることでRTLが正しく合成できるか、デットコードや非同期クロック間の載せ替え回路が適切かなど、IPが再利用に耐える品質レベルかのチェックも行います。

- RTLが正しく論理合成可能か

- デッドコードやFSMデットロックがないか

- 非同期クロック間の載せ替え回路は適切か

3.再利用可能なIPへカスタマイズ

これらが完了したのち、以下のようなカスタマイズを行います。

- 回路構成やRTL記述の不具合修正

- 仕様書と回路が一致するようにアップデート

- 検証項目抽出、検証環境構築

採用事例(ケース1・ケース2)

では以降では、実際の事例を紹介します。

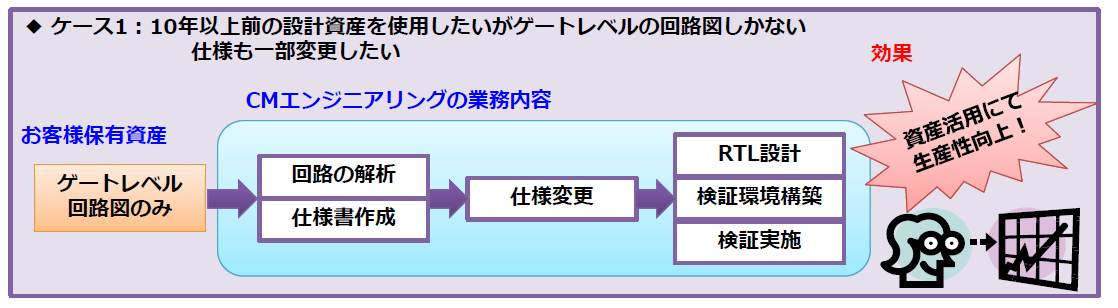

| 【ケース1】 | |

| ・10年以上前の設計資産を使用したいが、ゲートレベルの回路図しかない仕様も、一部変更したい |

本ケースで、お客様の保有資産はゲートレベルの回路図のみでした。

CMエンジニアリングの業務としては、まず回路の解析を行い、そこから仕様書を作成しました。その後、RTL設計や設計環境の構築、検証実施を行い、最終的には元々ゲートレベルの回路図しかなかった状況から、RTLの再利用/アップデートなど資産活用を行える状況となり、生産性向上が実現できました。

図2 サービス概要①

(出典:CMエンジニアリング株式会社)

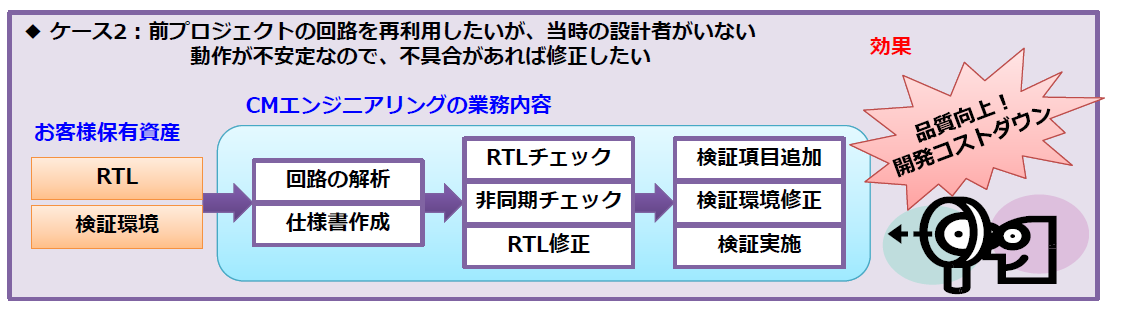

| 【ケース2】 | |

| ・前プロジェクトとの回路を再利用したいが、当時の設計者がいない | |

| ・動作が不安定なので、不具合があれば修正したい |

このケースは、RTLだけでなく、実際にシミュレーションができる検証環境もお客様にご用意いただきました。

このRTLと検証環境をもとに以下のように作業を進めていきました。

- 回路を解析し、仕様書を作成

- RTLのリントチェックや非同期のCDCのチェック、RTLの修正を実施

- お客様がお持ちの検証環境を利用して、仕様変更に対する検証項目の追加と検証環境の修正を行い、動作の一致性を確認

最終的にはお客様のコストダウンを含めて、品質向上を図ることができました。

図3 サービス概要②

(出典:CMエンジニアリング株式会社)

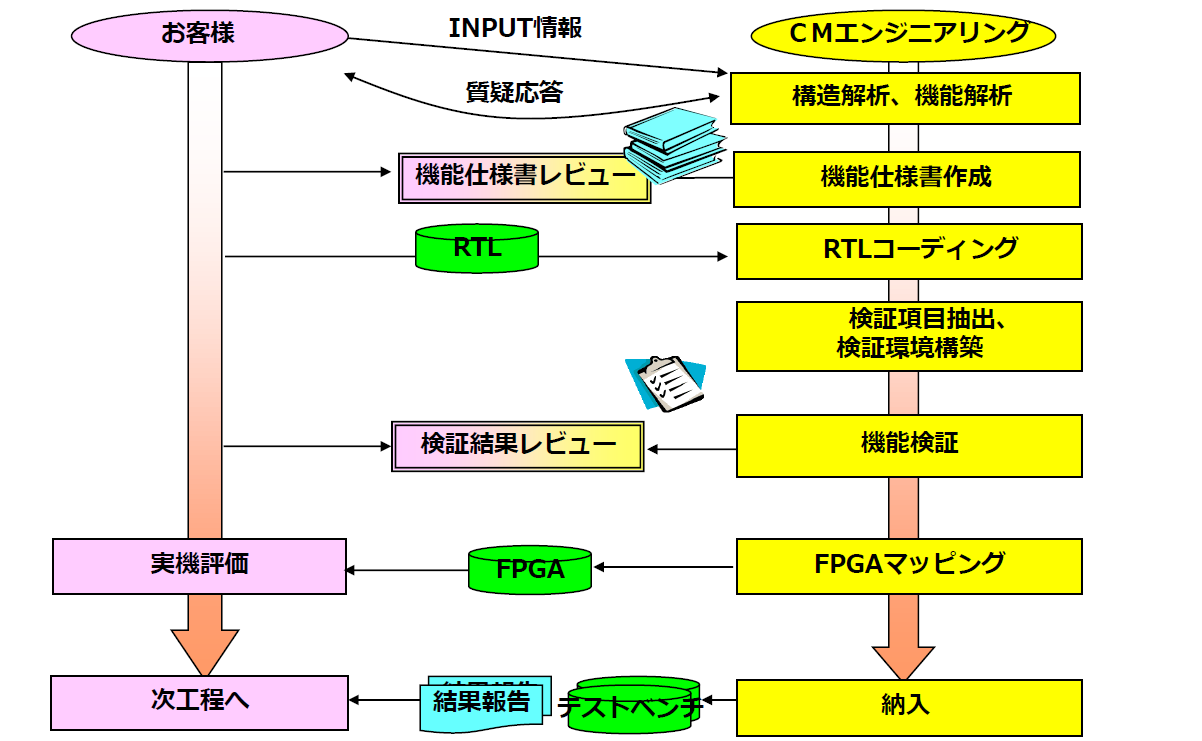

当サービスの流れを以下に整理します。

◆構造解析、機能解析までの時間を大きく左右するお客様との質疑応答

「RTLや回路図しかない」という場合は、それ以外にお客様側でどのような情報をお持ちなのかという点は解析時間を大幅に左右するという点でとても重要です。

例えば周辺インタフェースの参考になるもの、もしくはローカルで資料として残っている何かしらの資料などを提供いただくことで、RTLから解析するだけでなく、周辺のタイミングやインタフェースを理解しながら、中の解析をしていくことができますので、お客様がお持ちの情報を入念にヒアリングさせていただいています。

◆既存RTL/回路図の解析ができれば、あとはスムーズ

この解析が終われば、仕様書作成からお客様の必要に応じてRTLコーディングや機能検証、FPGAをマッピングした状態で納品するなど一連のFPGA開発の工程を踏みながら進められます。

図4 お客様とCMエンジニアリングの役割分担例

(出典:CMエンジニアリング株式会社)

開発実績

CMエンジニアリングでの実際の開発実績とその工数を以下に記載します。

1番簡単なものであれば、以下表1の項目1番目の小規模の内容に対してソースコードから仕様書化で、開発期間が2か月、開発人数が1人のイメージです。

項目2~5は、それぞれ工程が複雑化しているため、ケースによって開発人数が2~3人程度必要になります。

表1 開発実績

| ケース | 工程内容 | ブロック数 | 開発期間 | |

|---|---|---|---|---|

| 1 | RTLのみ存在 | 既存ソースコードを仕様書化 | 1(小規模) | 2か月 |

| 2 | RTLのみ存在 | 既存ソースコードを仕様書化、 機能検証、ソースコード修正 | 9(小規模) | 2か月 |

| 3 | 海外IP購入 | 回路解析、非同期解析、報告書作成 | 5(大規模) | 2~3か月 |

| 4 | 回路図のみ存在 | 回路解析、仕様書化、RTL作成、機能検証、FPGA化、実機評価サポート | 5(中規模) | 2か月 |

| 5 | 非同期設計のRTL存在 2RTLを1Chip化 |

回路解析、仕様書修正、非同期→同期化にRTL修正、機能検証、FPGA化、実機評価サポート | 2(中規模) | 2か月 |

(出典:CMエンジニアリング株式会社)

このように開発人数は異なるものの、実際に納品するまで2~3か月で納品できる実績を持っています。

最後に

既存の設計物であるRTL、回路図は会社資産ですが、そのままでは利用可能な資産ではありません。RTL、回路図を仕様書化することで再利用化を可能とする当サービスにご興味をお持ちの方は以下よりお問い合わせください。

最後までご覧いただきありがとうございました。