Vivado®2020.2でZynq® UltraScale+™ MPSoC Verification IP(VIP)を利用したシミュレーション(基本編)~VIPの概要とbase sample designの環境構築~

2019.2リリース以前のバージョンでは、Vivado®の[File]→[Open Example Project]をクリックし[Base ZYNQ®US+ MPSOC]を選択するとサンプルデザインを利用できました。

2019.2より新しいバージョンではVIPのサンプルデザインがないため、これから数回を分けて2020.2を使用するときに、VIPのサンプルデザインの作成方法や、GPIO、BRAM、CDMA、DDR4のシミュレーション方法を紹介したいと思います。2020.2より新しいバージョンでもこの方法で対応可能です。

なお、本TECHブログでは、EXAMPLEデザインを資料ダウンロードしていただけます。

あわせてご確認ください。それでは、始めましょう。

このブログは「FPGA設計ブログ一覧」の

2. シミュレーションのひとつです。

目次

Zynq® UltraScale+™ MPSoC Verification IPについて

Zynq® UltraScale+™ MPSoC Verification IPとは

Zynq® UltraScale+™ MPSoC Verification IPはスタンドアロンIPではありません。

Zynq® UltraScale+™ MPSoC IPに組み込まれており、PS Configurationウィザードのパラメーターを継承しています。

Zynq® UltraScale+™ MPSoC Verification IPは、Zynq® UltraScale+™ MPSoCベースのアプリケーションの機能シミュレーションをサポートします。 これは、プロセッサシステム(PS)-PLインターフェースおよびPSロジックのOCM/DDRメモリを模倣することにより、プログラマ ブルロジック(PL)の機能検証を可能にすることを目的としています。 このVIPは、SystemVerilogモジュールのパッケージとして提供されます。

VIPの動作は、一連のSystemVerilogタスクを使用して制御されます。

Zynq® UltraScale+™ MPSoC Verification IPの特徴

- ピン互換でVerilogベースのシミュレーションモデル。

- すべてのAXIインターフェースをサポート。AXI4.0に準拠。

- AXI_HPの場合は32、64、および128ビットのデータ幅、AXI_ACPの場合は128ビット。

- スパースメモリモデル(DDR用)およびRAMモデル(OCM用)。

- SystemVerilogタスクベースのAPI。

- Vivado®DesignSuiteで提供。

- ブロッキングおよび非ブロッキング割り込みのサポート。

- Zynq® UltraScale+™ MPSoC仕様によるID幅のサポート。

- すべてのZynq® UltraScale+™ MPSoCでサポートされるバースト長とバーストサイズのサポート。

- FIXED、INCR、およびWRAPトランザクションタイプのサポート。

- AXIVIPモデルによって提供されるプロトコルチェック。

- 読み取り/書き込み要求機能。

- OCM/DDRトランザクションのシステムアドレスデコード。

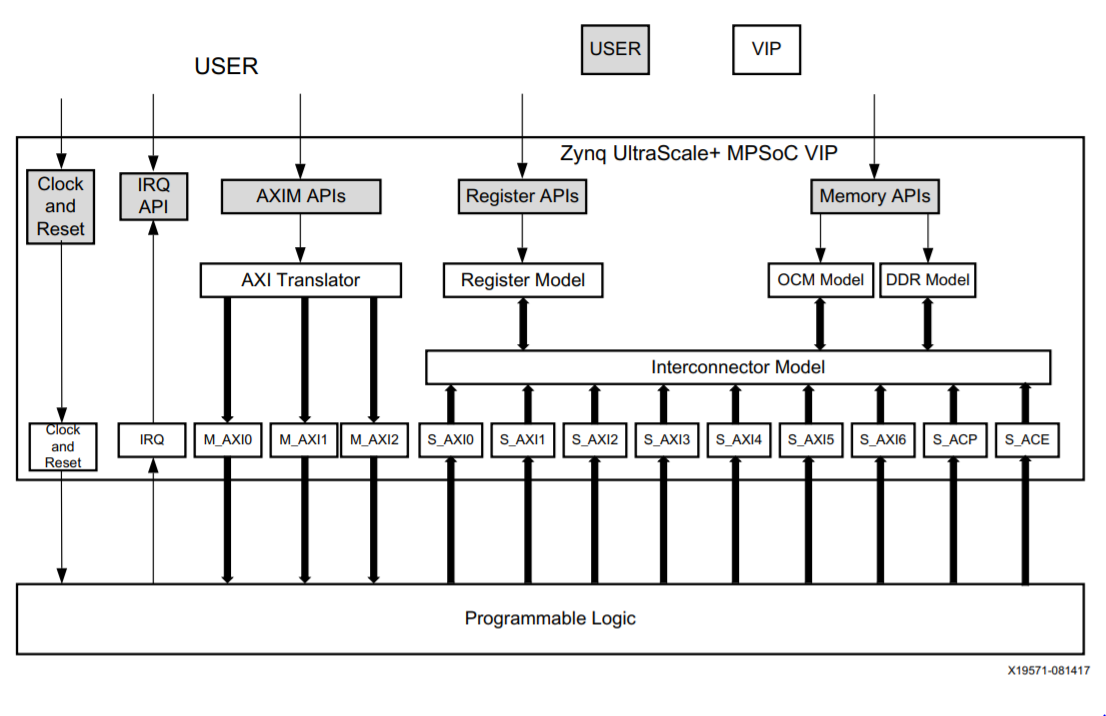

図1 VIPロジックのアーキテクチャ

出典:DS941:Zynq-7000 All Programmable SoC Verification IP v1.0

https://docs.amd.com/v/u/en-US/ds941-zynq-ultra-ps-e-vip(参照2022-07-07)

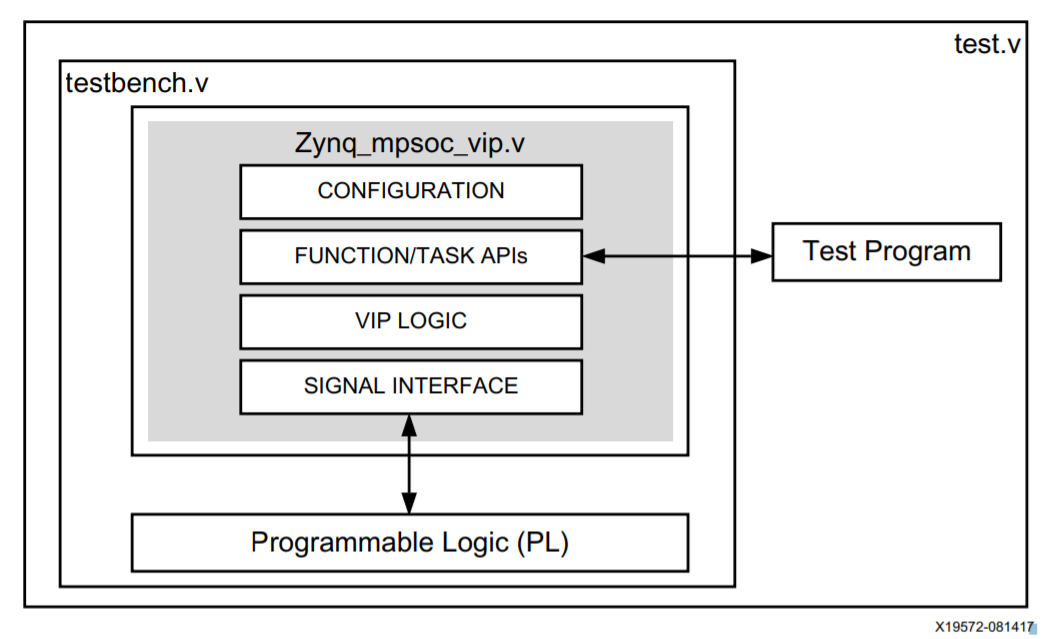

図2 Zynq® UltraScale+™ MPSoC VIPテストベンチの構成

出典:DS941:Zynq-7000 All Programmable SoC Verification IP v1.0

https://docs.amd.com/v/u/en-US/ds941-zynq-ultra-ps-e-vip(参照2022-07-07)

サンプルデザインの作成手順

| 1. | 以下のコードをダウンロードしてください。 ダウンロードはこちら コードをすべて選択し、ファイル名をdesign_1.tclとして保存します。 (全部で1,811行があり、1,811行目がcreate_root_design ""であることを確認してください) |

適当な所でvipbase1のフォルダを作成し、1で作ったdesign_1.tclをvipbase1フォルダに保存します。

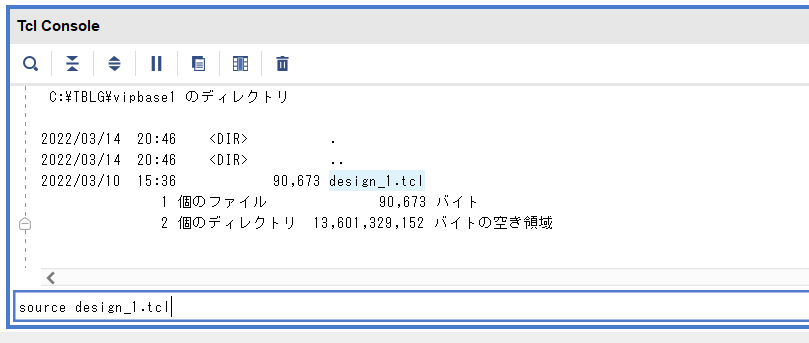

| 2. | Vivado®2020.2を起動し、Tcl consoleで2で作成したvipbase1にchangeし、source design_1.tclを入力し、実行します。(BDデザインを作成する) |

図3 Tcl Console画面

出典:Vivado® ML Edition

以下のデザインが作成されることを確認します。

※画像クリックで大きな画像が表示されます。

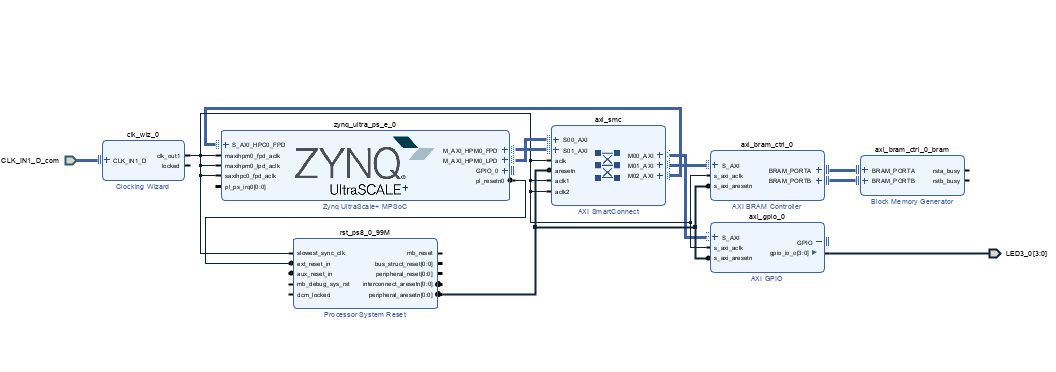

図4 Design_1.tclから作成されたBDデザイン

出典:Vivado® ML Edition

こちらで、Vivado®2020.2のZynq® UltraScale+™ MPSoC Verification IPシミュレーション用のBASEデザインが作成されました。

EXAMPLEデザイン

2020.2を使用するときのVIPのサンプルデザインの作成方法や、GPIO、BRAM、CDMA、DDR4のシミュレーション方法を紹介しました。

EXAMPLEデザインについては以下よりダウンロードいただけます。

おわりに

いかがでしょうか。次回はLED&AXI_BRAMを駆動(テスト)するテストベンチの作成方法を紹介したいと思います。最後までご覧いただきありがとうございました!

このブログは「FPGA設計ブログ一覧」の

2. シミュレーションのひとつです。

参考資料:

DS941:Zynq-7000 All Programmable SoC Verification IP v1.0

Xilinx Answer 69622

Xilinx Answer 70185

Xilinx Answer 70186

Xilinx Answer 75942