Vivado®2020.2でZynq® UltraScale+™ MPSoC Verification IP (VIP)を利用したシミュレーション(発展編①)~外部LED駆動とAXI BRAMのデータ比較のテストベンチサンプル:サンプルデザインあり~

前回は、Vivado®2020.2でZynq® UltraScale+™ MPSoC Verification IP (VIP)を利用したシミュレーション(基本編)~VIPの概要とbase sample designの環境構築~と題し、VIPシミュレーション用のデザインを作成しました。

今回は外部LED駆動とAXI BRAMのデータ比較のテストベンチを作成します。

なお本篇で使用したEXAMPLEデザインはダウンロードできるよう準備していますので、気になる方はダウンロードしていただければと思います。

それでは、始めましょう。

このブログは「FPGA設計ブログ一覧」の

2. シミュレーションのひとつです。

目次

はじめに

使用するAMD ザイリンクス社のZynq® UltraScale+™ MPSoC Verification IP APIは以下になります。

APIの全リストは、DS941を参照ください。

DS941:Zynq® UltraScale+ MPSoC Verification IP

| APIs | Inputs | Outputs |

|---|---|---|

| set_debug_level_info When set to value '1 ', debug level info for Zynq UltraScale+ MPSoC VIP is reported, else no info is reported. The default value is 1. |

LEVEL: A bit input for the info level. | None |

| fpga_soft_reset Issue/Generate soft reset for PL. |

[3:0] reset_ctrl : 4-bit input indicating the reset o/p to be asserted for PL. (Details same as FPGA_RST_CTRL register defined in PS) |

None |

| por_srstb_reset Soft reset for VIP. It is a mandatory reset. |

por_reset_ctrl : 1-bit input reset to VIP. | None |

| write_data Initiate an AXI write transaction on the master port. This task should be used when the transfer size is less or equal to 128 bytes and the write data is provided as an argument to the task call. Burst type used is INCR. This will be a blocking task and will return only after the complete AXI WRITE transaction is done. |

[31:0] addr: Write address (aligned address) [7:0] wr_size: Number of data bytes to be written [1023:0] wr_data: write data (max . 128 bytes). |

RESPONSE: The slave write response from the following: [OKAY, EXOKAY, SLVERR, DECERR] To use the write_data API, the address should be aligned. For an address that is not aligned, use the write_burst_strb API. |

| read_data Initiate an AXI read transaction on the master port. This task should be used when the transfer size is less or equal to 128 bytes and the read data is returned as an output to the task call. Burst type used is INCR. This will be a blocking task and will return only after the complete AXI READ transaction is done. |

[31:0] addr: Read address (aligned address) [7:0] rd_size: Number of data bytes to be read |

DATA: Valid data transferred by the Slave RESPONSE: The slave write response from the following: [OKAY, EXOKAY, SLVERR, DECERR] |

サンプルテストベンチの作成手順

| 1. | 以下のコードをダウンロードしてください。 ダウンロードはこちら コードをすべて選択し、ファイル名をsim_tb_top.svとして保存します。 |

| 2. | Vivado®2020.2を起動し、基本編で作成したPROJECTを開きます。 |

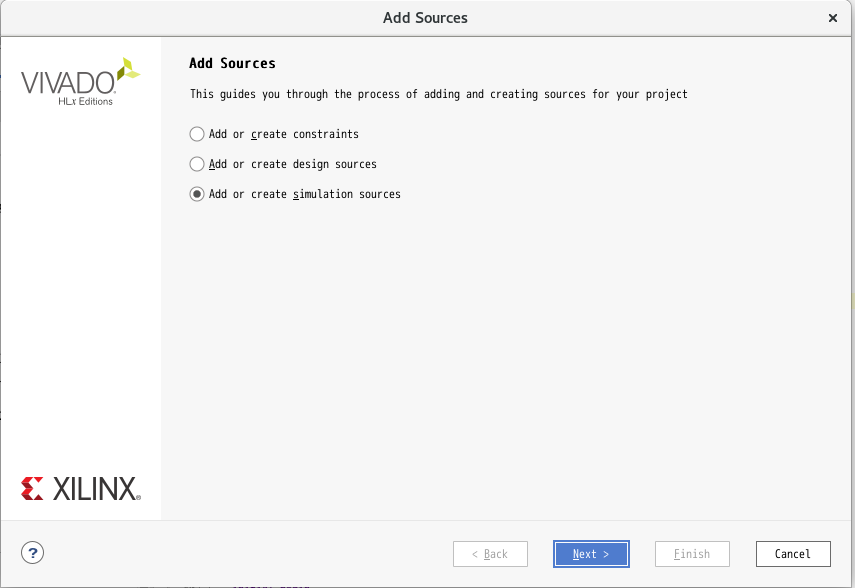

| 3. | File→Add Sources で下記のようにsim_tb_top.svをPROJECTに追加します。 |

|

出典:Vivado® ML Edition |

|

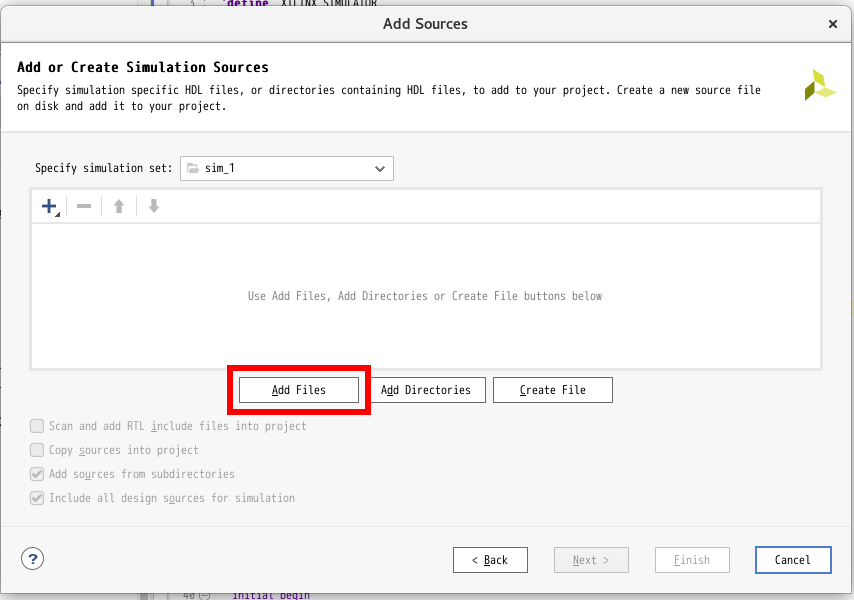

| 3-1. | Add Filesを選択し、sim_tb_top.svを追加します。 |

|

出典:Vivado® ML Edition |

|

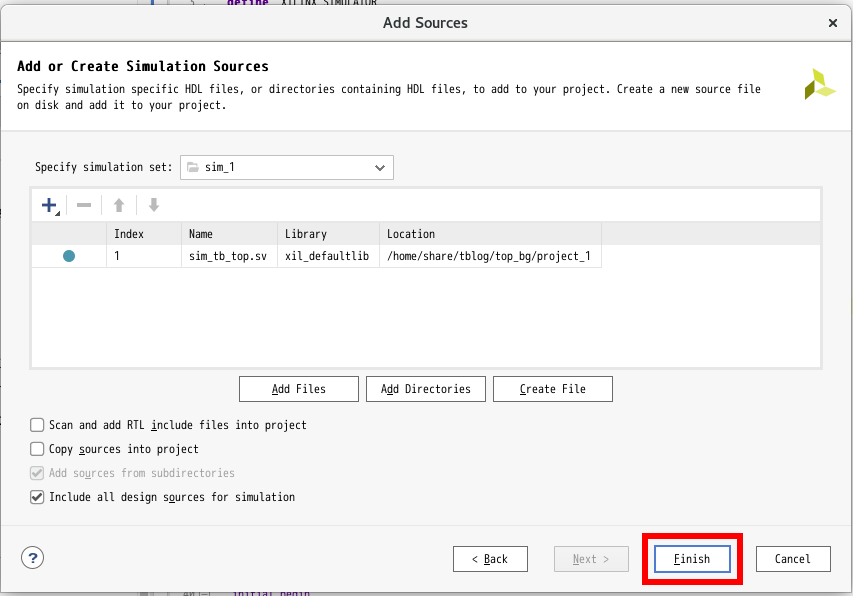

| 3-2. | Finishを選択し、終了します。 |

|

出典:Vivado® ML Edition |

|

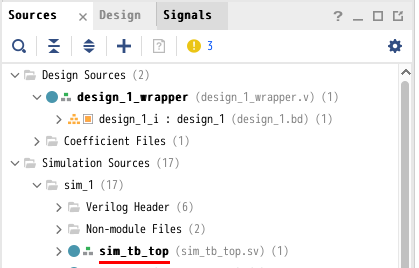

| 3-3. | Sourcesタブで、下図のようにsim_tb_topがtopデザインになっていることを確認します。 |

|

出典:Vivado® ML Edition |

|

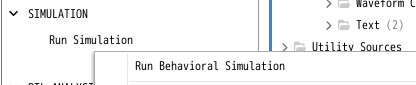

| 4. | シミュレーションの実行 下図のようにSIMULATION→run Simulation→Run Behavioral Simulationを選択、simulationを実行します。(環境依存で、時間がかかる場合があります) |

|

出典:Vivado® ML Edition |

|

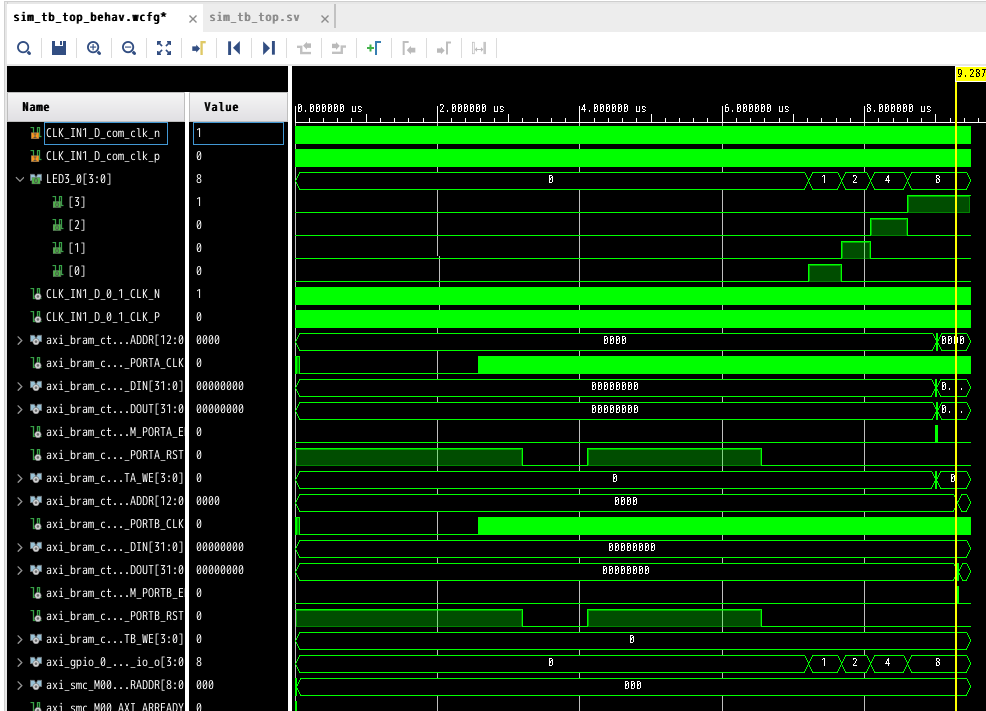

| 5. | 観測したい信号を追加し、runを再実行し、波形を観測します。(4つのLEDが順番に動作していることを波形上で確認できます) |

|

出典:Vivado® ML Edition |

|

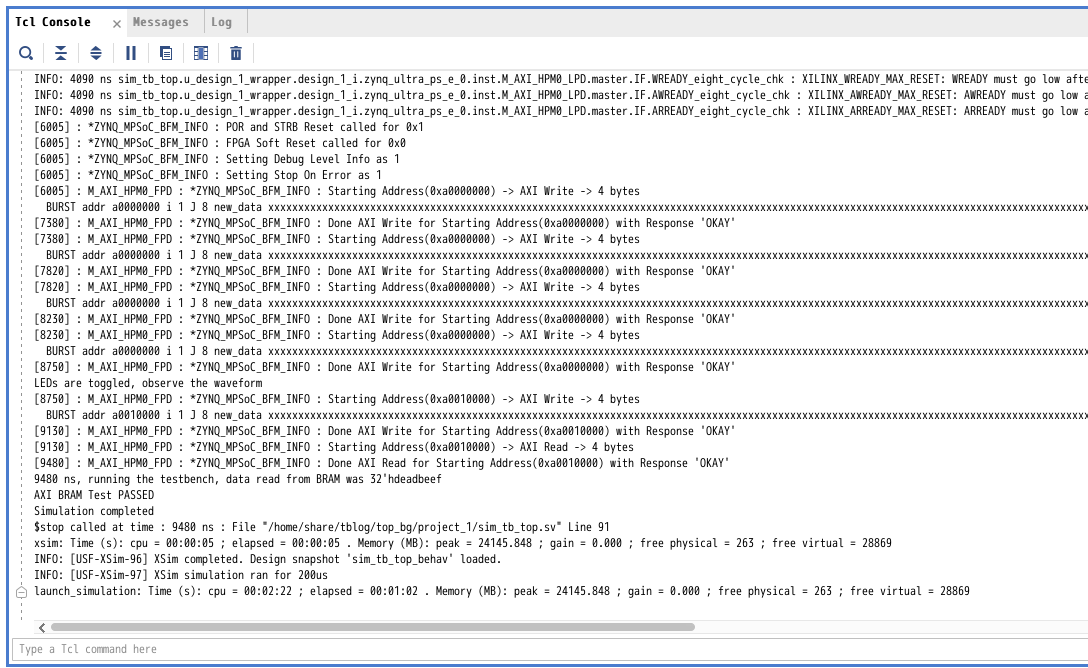

| 6. | シミュレーション結果はTcl console上でも確認ができます。 AXI BRAM Test PASSEDやSimulation completed の行で確認します。 |

|

出典:Vivado® ML Edition |

|

| こちらで、サンプルテストベンチの作成が完了しました。 | |

EXAMPLEデザイン

本ブログでは、外部LED駆動とAXI BRAMのデータ比較のテストベンチを作成する手順を紹介しました。

EXAMPLEデザインについては以下よりダウンロードいただけます。

おわりに

いかがでしょうか。次回はPL側のDMAを用いたVIPシミュレーションの方法を紹介したいと思います。

最後までご覧いただきありがとうございました。

このブログは「FPGA設計ブログ一覧」の

2. シミュレーションのひとつです。

参考資料:

DS941:Zynq-7000 All Programmable SoC Verification IP v1.0

Xilinx Answer 69622

Xilinx Answer 70185

Xilinx Answer 70186

Xilinx Answer 75942