シミュレーションツールを用いたFPGAの等価確認手法

皆さんこんにちは。

本ブログでは、シミュレーションツールを使用したFPGAの等価確認手法を紹介します。

様々な手法があるかと思いますが、本ブログでは比較的簡単に実施いただける方法を紹介します。

それでは始めます。

目次

FPGA置き換えで等価性検証が求められる背景

まず等価性検証が求められる背景として、多くが入手困難なデバイスを少しでも入手性の良いデバイスに変更したいというご要望から、既存のデバイスを置き換える作業が発生しているかと思います。

その際に入力するRTLは同じでもIPやマクロが異なる場合には、以前と同じ動作をするかどうか確認が必要です。

さらに、IPマクロが同一であっても、合成ツールが異なるバージョンのものを使用するとなると、出力された結果が過去のものと一致するかどうかの確認も必要になります。

実際に論理合成ツールの結果確認のためRTLとゲートの等価性検証を実行するケースもありますが、多くの場合等価性検証は実行されていません。そのため、慣れない作業をしなければならず、何を使用してどのように検証したら良いのかを悩まれている方も多いかと思います。

図1. FPGA置き換えで等価性検証が求められる背景

シミュレータによる等価性検証手法

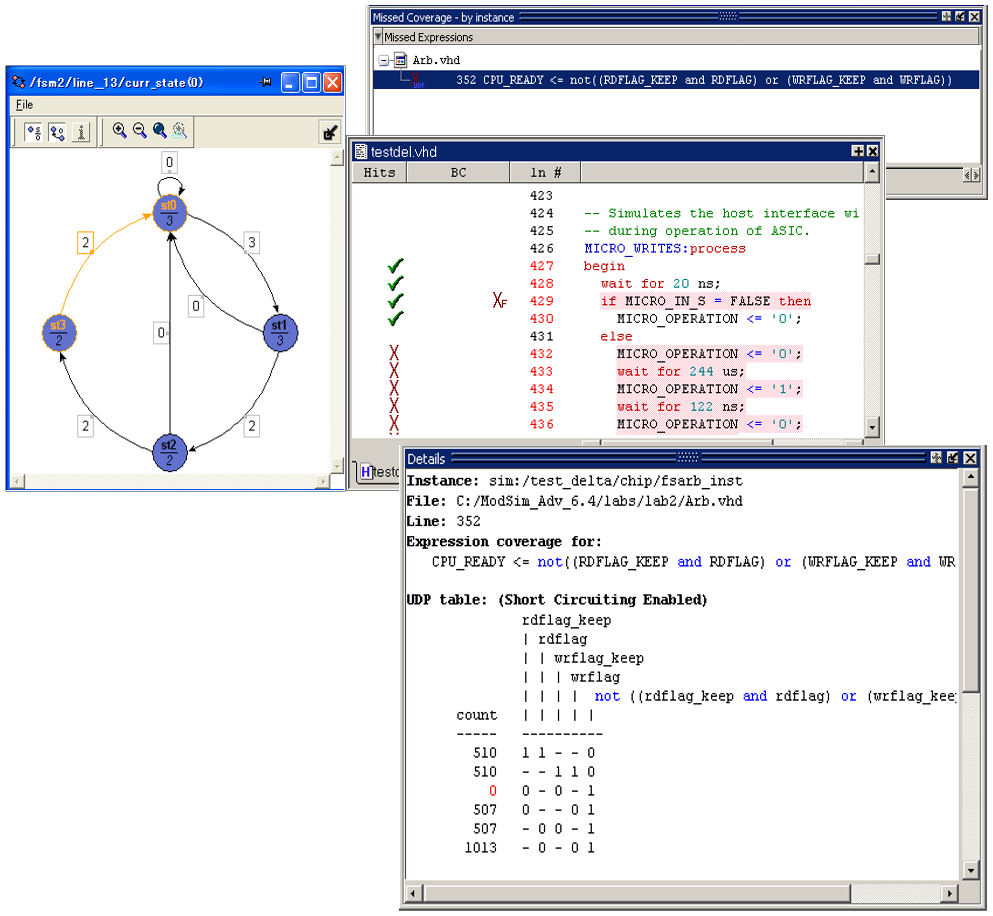

シミュレータを使用した検証方法としては、波形比較が最も簡単に使用できる機能となります。

ModelSim/Questaなど波形比較機能を持つシミュレータで実行することで、波形比較が簡単に実行できます。ModelSim/Questaでの波形比較は通常のシミュレーションフローの中で実行することができ、WLFとよばれる波形ファイルを比較し、とても簡単に実行することができます。

シミュレータを使用して等価性検証を行いますので、基本的にはテストパタンの質にかなり依存します。テストパタンの不足(実際に活性化していないコードがデザインの中に含まれる)について確認しつつ、波形比較を行っていかなければいけません。デザインを網羅的に活性化しているかの確認が必要となります。

先述した部分では、コードカバレッジが一つの手法になりますので、コードカバレッジを使用してデザインがしっかりと活性化されていることを確認したうえで、波形比較を行っていただくのが良いでしょう。

さらに、コードカバレッジを取得すると、シミュレータからカバレッジが取得できていないというのが、当然ながら判別することができます。しかし、「テストパタン不足なのか」、「デッドコードとよばれる構造的に実行できないコードなのか」についてはシミュレータからは判別ができません。そういった部分の解析に時間がかかる場合には、Auto Checkなどフォーマル検証ツールを使用してデッドコードを自動検出するようなフローを考えてみてもいいでしょう。

1. シミュレーション結果を使用した波形比較

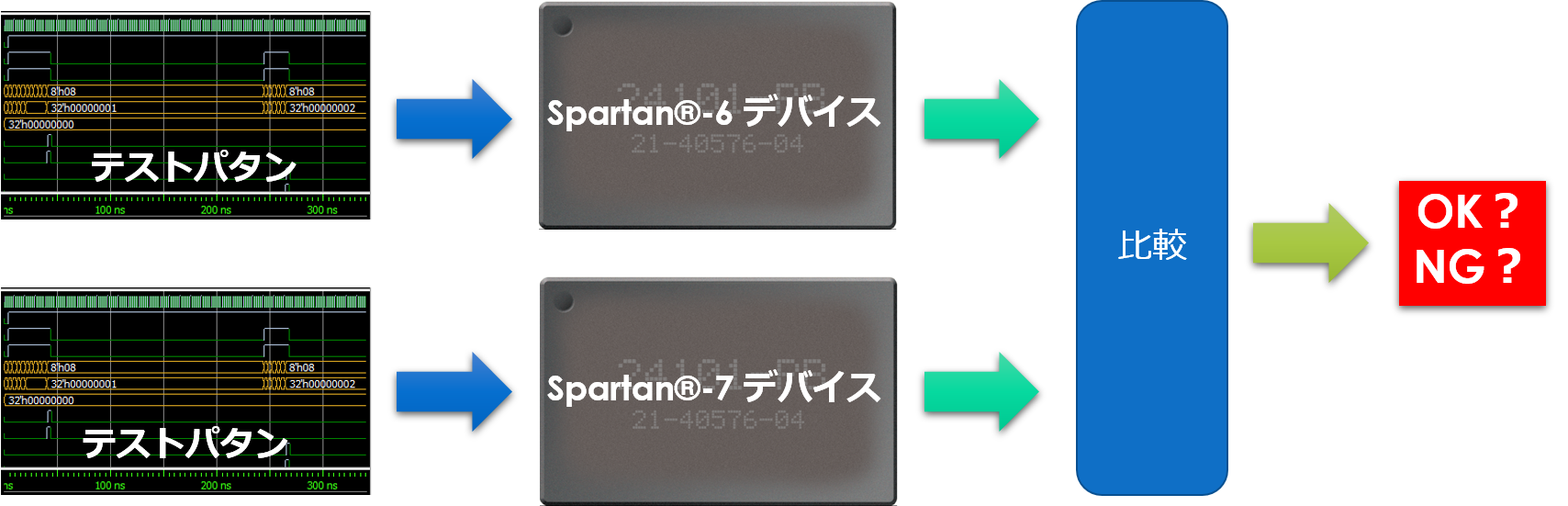

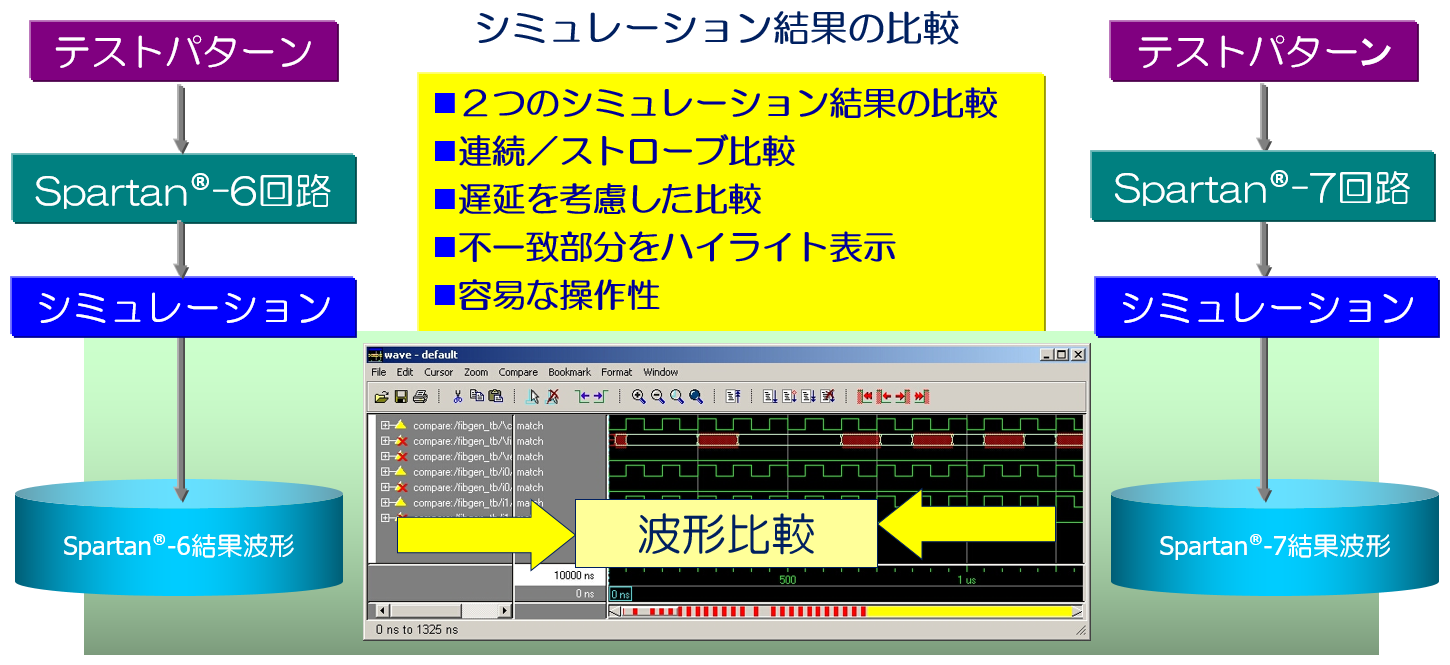

シミュレーション結果を比較する方法は、とても簡単で、まずは通常通りそれぞれシミュレーションを実行します。

例えばSpartan®-6用回路でプライマリI/Oの波形をダンプし、同じようにSpartan®-7で波形ダンプを行います。2つの出力結果(波形ファイル)ができますので、それを波形比較というコマンドを使用して比較をします。

比較方法には、連続的に比較することもできますし、ストローブを当てながら比較をすることもできます。RTLとゲートの場合には、遅延を考慮した比較も可能です。

不一致箇所がハイライト表示されるので、波形を見ればどこで不一致が発生したかすぐに確認することができ、操作自体は普段ご使用いただいているシミュレータと変わりませんので、誰でも簡単にご利用できます。

図2. シミュレーション結果を使用した波形比較

ただしゲートシミュレーションが絡む場合には時間を要するため注意が必要です。一般的にゲートシミュレーションはRTLシミュレーションに比べ遅いと言われており、ゲート vs ゲートの波形比較の場合シミュレーションの実行時間が非常に長くかかってしまいます。

当然テストベンチの内容(大容量のデータ)により更に実行時間が増える場合もあります。

(コードカレッジ結果からのパタン追加なども)

上述したような場合には、ModelSimDE/PEより高速なQuestaSimと呼ばれるシミュレータの導入を検討していただくことも必要になるかと思います。

QuestaSimと聞くと、非常に高額だという印象を受けられる方もいらっしゃるかもしれませんが、ショートターム(1か月など短期間)でのご提案も可能になっています。

さらに使い勝手に関してはModelSimと共通のコマンド、共通のGUI、共通のログ、共通の波形データをご利用いただくことができます。

即座に高速なシミュレーションエンジンでシミュレーション実行時間を短縮することができますので、ゲートレベルシミュレーション実行時間が支配的な場合はご一考いただくといいと思います。

2. コードカバレッジ

コードカバレッジを使用していただくと、実際漏れなくすべてのブロックにテストが実行されているかを確認できます。

コードカバレッジはModelSim/QuestaSimに標準で装備されていますので、今ある機能を使用していただければよいということになります。

次にコードカバレッジ収束の効率化の対策についてお伝えします。

図4. コードカバレッジ収束の効率化の対策

コードカバレッジが取れないポイントは、

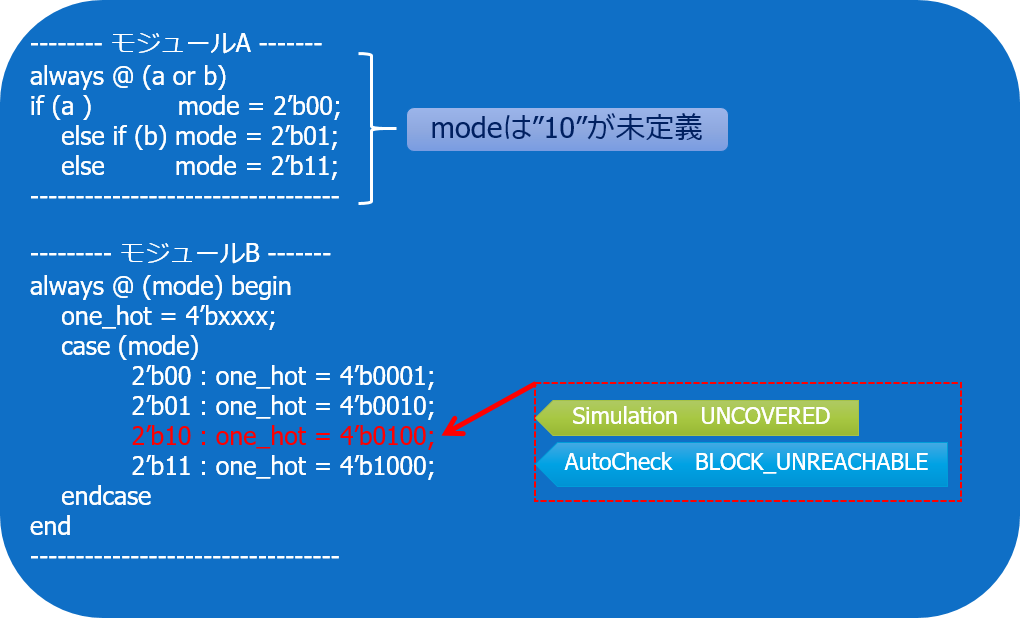

図4.にある通りシミュレータでコードカバレッジを実行すると“UNCOVERED”(実行回数0回)というステータスがふられます。

実際に図4の例ではモジュールA側で“mode”という信号で値を設定し、モジュールB側で“mode”信号を使用して条件分岐をかけます。

このようなケースで、シミュレーションを実行し“UNCOVERED”が出ますと回路のFan-In側を探索していき、mode信号がどのように作られているかを確認する必要があります。

AutoCheckのようなフォーマル検証ツールを使用して、実行すると“BLOCK_UNREACHABLE”というステータスがふられます。

“BLOCK_UNREACHABLE”から構造的に実行できないということを判別ができます。

構造的に動かなくても構わない場合はカバレッジ分母から除外いただき、RTL構造の問題ならソースコードを修正いただく必要があります。

このように、デッドコードの見極めを自動で判断できるので、古いデザインでデザインの詳細が分からない場合にも容易に対処することができます。

フォーマル検証ツールでの等価性検証手法

さらにフォーマル検証で等価性検証を行う方法もあります。(製品名:OneSpin)

FPGAのRTLと論理合成後のネットリストを比較することや配置配線後のネットリストの間で比較することができます。

ツール自体は、一部のFPGAベンダ自体でも使用しており、非常に信頼性が高いツールであるといえます。

しかしながら、全てのデバイスをサポートしているわけではありませんので、弊社までお問い合わせいただき個別に状況を聞きながら対応させていただければと思います。

波形比較に関して未だ使用したことがない方は、弊社のTECHブログをご覧いただくと実行方法の簡単な例が紹介されています。

さらに詳細に知りたい方は、弊社で開催しているウェビナーをご活用ください

まとめ

いかがでしたでしょうか。

デザインの等価性検証は手持ちのシミュレータでも実行可能ですので、新たな投資なく等価性検証が実行可能です。ぜひご活用いただければ幸いです。

- 「ModelSim/Questa エディション比較表」

-

https://www.paltek.co.jp/semiconductor/maker/mentor/modelsim_questa/index.html

- 「Siemens EDA/シーメンス EDA お問い合わせ」

-

https://www.paltek.co.jp/semiconductor/maker/mentor/inquiry/index.html

- 「Design and Verification LANDSCAPE」メールニュース登録フォーム

-

https://www.paltek.co.jp/design/subscribe_davl_mn/index.html