【回路設計ヒント】トランシーバのリファレンスクロック使用時の注意点

みなさん、こんにちは。

今回はトランシーバのリファレンスクロックを使用する際の注意点を説明します。

回路図を作成する際にクロックを適切に接続していないと、トランシーバを駆動させることができないなど問題が発生するため、注意が必要です。

本ブログはAMD ザイリンクス社の UltraScale™アーキテクチャをベースに執筆しています。

それでは、始めましょう。

このブログは「FPGA設計ブログ一覧」の

基板設計・評価関連のひとつです。

目次

トランシーバの構造とリファレンスクロックの関係

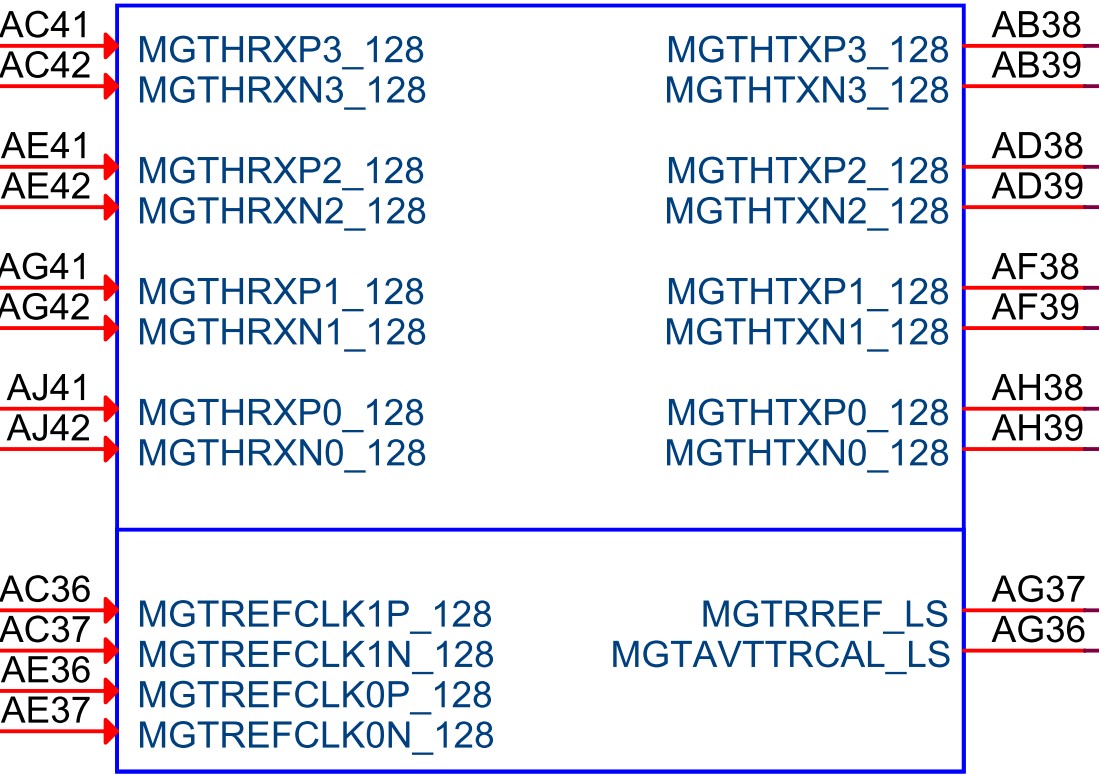

トランシーバは4Channelを1Quadとして、1Quadに対して2本のリファレンスクロックの入力を持っています。

以下の例(Kintex® UltraScale™ GTH)ではQuad128に4系統の受信(MGTHRX)と送信(MGTHRX)があり、それに対して2本のリファレンスクロック(MGTRECLK0/1)を持っています。AMD ザイリンクス社の7シリーズ以降のFPGAは、すべてこの構造に基づいています。

図1. 回路図シンボル

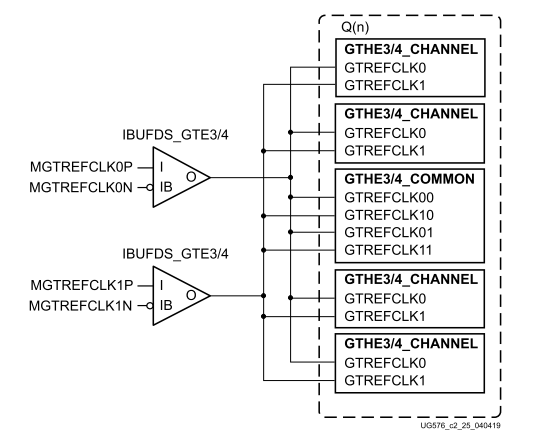

Quad内のクロック接続

Quad内には1個のCommon(QPLL 2個)と 4個のChannel(CLL 1個)があり、リファレンスクロックのポートから接続されます。

この際の注意点はRTL上でクロックを接続する際に下記の接続しか行うことができません。

- MGTREFCLK0はGTREFCLK0x(Common)とGTREFCLK0(Channel)のみ接続

- MGTREFCLK1はGTREFCLK1x(Common)とGTREFCLK1(Channel)のみ接続

0側のクロックで1側を駆動しようとすると配線でエラーとなってしまいます。

これを行うにはCommon/Channel内部にあるセレクタを使用する必要があります。

※画像クリックで大きな画像が表示されます。

図2. シングルクワッドにある複数の基準クロックを使用する複数のGTHトランシーバ

出典:UltraScale Architecture GTH Transceivers User Guide<P38>

https://japan.xilinx.com/content/dam/xilinx/support/documentation/user_guides/ug576-ultrascale-gth-transceivers.pdf

(参照2022-07-07)

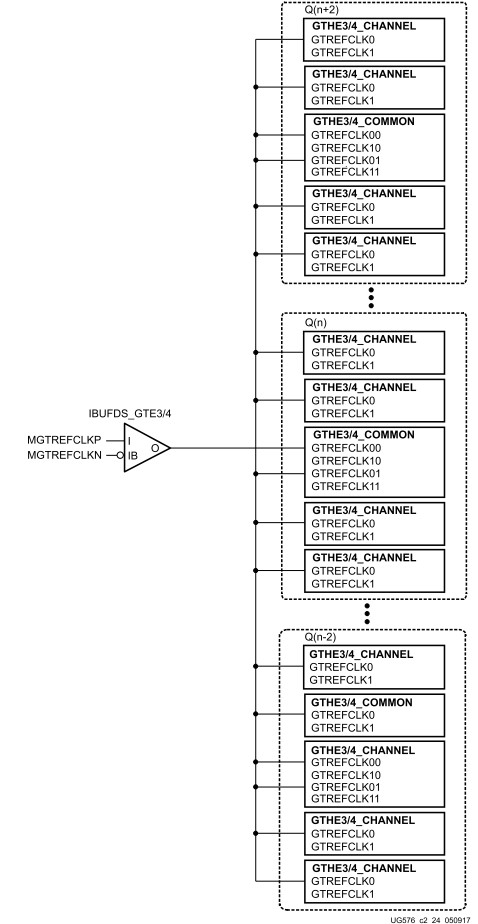

リファレンスクロックとQuadの接続

Quadに対してリファレンスクロック入力があると書きましたが、使用するすべてのQuadにリファレンスクロックを入力しなければいけないかというとそうではありません。

リファレンスクロックは分配されており、FPGA内部で他のQuadにも接続されています。ただし、条件は以下のようになります。

- UltraScale™ FPGAでは上下2個のQuadまで

- 7Series FPGAでは上下1個のQuadまで

※画像クリックで大きな画像が表示されます。

図3. 複数クワッドにある複数のトランシーバを使用する1つの外部基準クロック

出典:UltraScale Architecture GTH Transceivers User Guide<P36>

https://japan.xilinx.com/content/dam/xilinx/support/documentation/user_guides/ug576-ultrascale-gth-transceivers.pdf

(参照 2022-07-07)

またその他の注意点としては、SSI構造を持つFPGAではSSIの境界を超えた接続はできないため、隣り合っているように見えるQuadでもそれぞれにリファレンスクロックを接続する必要があります。

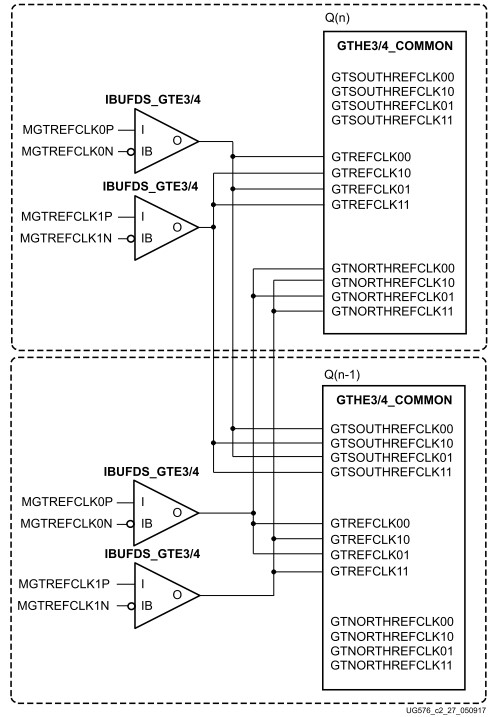

他のQuadからのリファレンスクロックも使用したい場合

自分自身のQuadのリファレンスクロックに加えて、他のQuadのリファレンスクロックも使用したい場合があります。

その場合は、GTSOUTHREFCLKとGTNORTHREFCLKを使用することで可能となります。

ただし、ここでも接続の制限として0側クロックは0側、1側クロックは1側への接続制限がありますので注意してください。

SouthとNorthの関係ですが、例えばQuad128のクロックをQuad129に接続したい場合はQuad129のNorthに、Quad129のクロックをQuad128に接続した場合はQuad128のSouthに接続することになります。

接続は以下のように覚えるとよいでしょう。

- 自分のQuadより大きいQuadからの接続はSouth

- 自分のQuadより小さいQuadからの接続はNorth

また、その他の注意点としてこのポートはトランシーバウィザードのStructural Optionでポートを有効にしないと出てきません。

※画像クリックで大きな画像が表示されます。

図4. 異なるクワッドにある複数の基準クロックでCPLLを使用する複数のGTHトランシーバ

出典:UltraScale Architecture GTH Transceivers User Guide<p40>

https://japan.xilinx.com/content/dam/xilinx/support/documentation/user_guides/ug576-ultrascale-gth-transceivers.pdf

(参照2022-07-07)

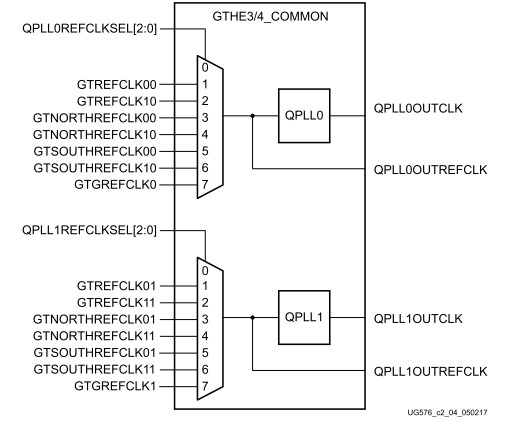

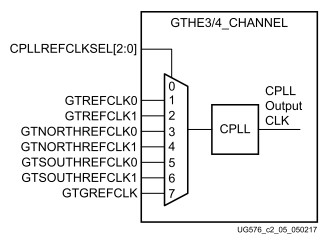

Quad内部でのクロックマルチプレクサ

0側のクロックは0x側、1側のクロックは1x側にしか接続できないと書きましたが、Common/Channel内にあるマルチプレクサを設定することで使用可能になります。REFCLKSEL端子に使用したいクロックを選択することで、PLLに対して自由にクロックを供給可能となります。

※画像クリックで大きな画像が表示されます。

図5. QPLLの基準クロック選択マルチプレクサ

出典:UltraScale Architecture GTH Transceivers User Guide<P33>

https://japan.xilinx.com/content/dam/xilinx/support/documentation/user_guides/ug576-ultrascale-gth-transceivers.pdf

(参照2022-07-07)

※画像クリックで大きな画像が表示されます。

出典:UltraScale Architecture GTH Transceivers User Guide<P34>

https://japan.xilinx.com/content/dam/xilinx/support/documentation/user_guides/ug576-ultrascale-gth-transceivers.pdf

(参照2022-07-07)

おわりに

いかがでしたでしょうか。

トランシーバのリファレンスクロック使用時の注意点をご理解いただけますと幸いです。回路図を作成する際にクロックを適切の接続していないとトランシーバを駆動させることができないなど問題が発生するためご注意ください。

最後までご覧いただきありがとうございました。

このブログは「FPGA設計ブログ一覧」の

基板設計・評価関連のひとつです。

UltraScale Architecture GTH Transceivers User Guide

https://japan.xilinx.com/content/dam/xilinx/support/documentation/user_guides/ug576-ultrascale-gth-transceivers.pdf