【回路設計ヒント】どうする?FPGAの端子アサイン ~クロック専用端子編~

皆さん、こんにちは。

FPGAの端子アサインはどうやって決めていますか?

- FPGA設計者が主体で決めている

- 回路(基板)設計者が主体で決めている

- FPGAも回路も一人で両方行っている

などさまざまなケースがあると思います。

一人で両方を行っている場合には臨機応変に修正対応が行えそうですが、分業にしている場合には

- FPGA設計者が決めると「パターンの引き回しが考慮されない」

- 回路設計者が決めると「FPGAの機能や仕組みが考慮されない」

といった問題が発生することがあります。

特に深刻なのが、基板は完成したものの端子アサインが原因でVivado™やISE®がエラーとなり、実機が動作しなかったり、基板の作り直しが必要になったりするケースです。

そこで今回は、FPGAを使い始めた方やFPGA内部についてあまり詳しくない方に向けて、FPGAの端子アサインに関する重要なポイント、特にクロックに関する注意点を紹介していきたいと思います。

それでは、はじめましょう。

目次

ここで掲載している図表は例として挙げています。

すべてのデバイスシリーズに当てはまるわけではありません。

必ずご使用になるデバイスシリーズのデータシートで内容をご確認ください。

専用端子に接続

クロックの入力は専用端子に接続する必要があります。

この専用端子は、FPGA内部の各種クロックリソースに専用配線で直接接続できる設計になっています。

主なクロックリソースには以下のようなものがあります。

- グローバルバッファ

- PLL(Phase-Locked Loop)

- MMCM(Mixed-Mode Clock Manager)

- DCM(Digital Clock Manager)

【 デバイスシリーズ別のクロック入力専用端子 】

| UltraScale+™ シリーズ | GC, HDGC |

|---|---|

| 7シリーズ | MRCC, SRCC |

| Spartan™ 6シリーズ | GCLK |

※

デバイスシリーズにより名称が異なりますので、各シリーズのクロッキングリソースユーザーガイドをご確認ください。

- シングルエンドのクロックは、クロック入力専用端子のPch側に接続

- クロック入力として使用しない場合は、通常のユーザーI/Oとして使用可能

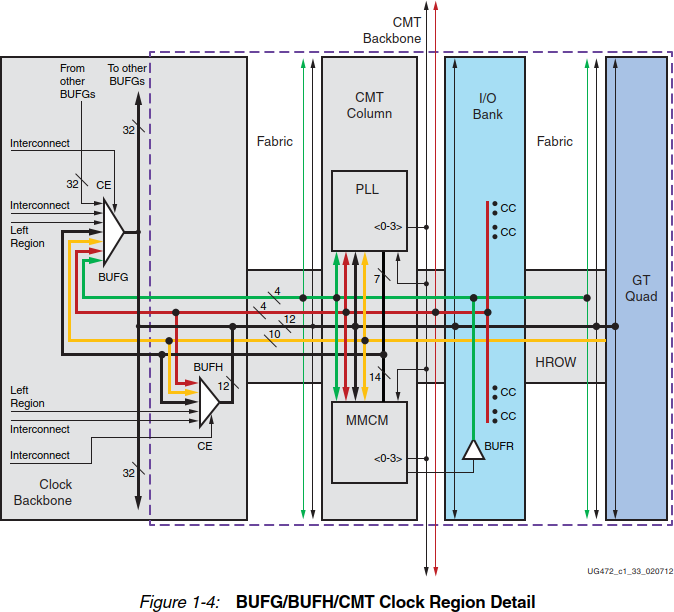

例えば7シリーズのクロック入力からの内部接続は以下のような構成になっています。

※

I/O BANKの「CC」と書かれているのがクロックの入力端子になります。

出典:

UG472 7 Series FPGAs Clocking Resources User Guide <P.19> (参照 2024/11/25)

注意点

オプションの設定により、通常の端子からもこれらのクロックリソースへの接続は可能です。

ただし、この場合は通常の配線経路が使用されるため、インプリメントを行うたびに

- 配線ルートが変化

- 配線長が変化

- タイミングが変化

といった問題が発生します。そのため、この方法は推奨できません。

集中させない

クロックを専用端子に接続するだけでは、適切な設計とは言えません。

その理由は、各デバイスシリーズにおいて、以下の制限が存在するためです。

制限事項

- クロック専用端子から接続できるグローバルバッファの数に制限

- PLL(MMCM/DCM)への接続可能な数と範囲に制限

- PLL(MMCM/DCM)で生成した複数クロックごとにグローバルバッファが必要

これらの制限により、特定のI/O BANKにクロック入力を集中させてしまうと

- クロックリソースの不足

- 希望する構成の実現が困難

といった問題が発生する可能性があります。

そのため、内部リソースを十分に考慮した端子アサインの計画が重要です。

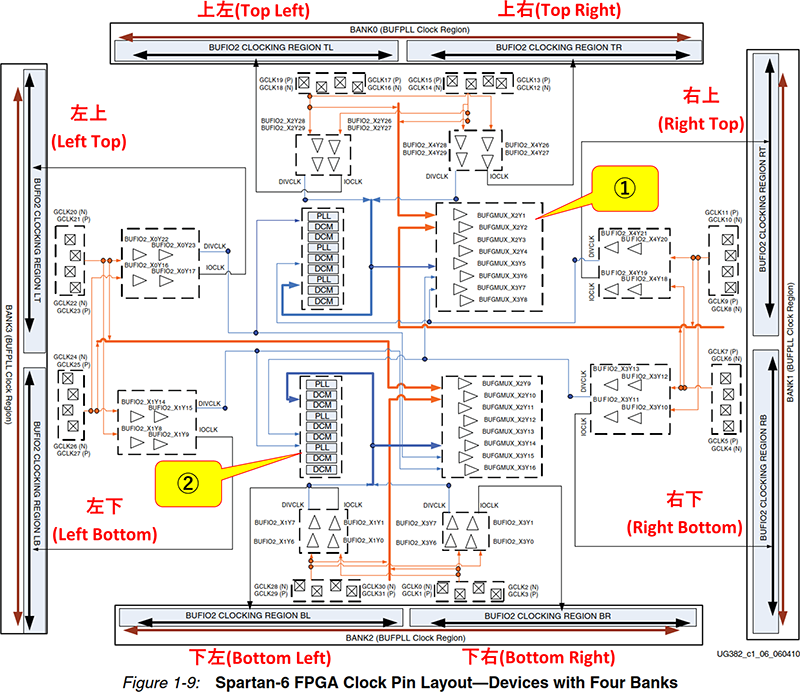

具体例:Spartan™ 6シリーズの場合

- BANK0上(T)とBANK1右(R)のGCLKから直接接続可能なグローバルバッファ

→①が指すBUFGMUX_X2Y1~X2Y8のみ(橙色の線) - BANK2左右(BL/BR)、BANK1下(RB)、BANK3下(LB)から直接接続可能なPLL/DCM

→②が指すPLL/DCMのみ(青色の線)

出典:

UG382 Spartan-6 FPGA Clocking Resources User Guide <P.26> (参照 2024/11/25)

確認

クロックに関する端子アサインや各種クロックリソースの配置・配線ルールは、データシートでも確認できますが、最も確実な方法は以下の手順です。

- 実際の使用形態を想定した仮のデザインを作成(クロックが削除されないように注意)

- Vivado™やISE®でインプリメントを実行

- warningの確認

- 必ず「Generate Bitstream」まで実行

論理合成・配置配線が完了していても、最終段階の「Generate Bitstream」でルール違反が判明しエラーが発生する場合があります。

まとめ

クロックの入力は専用端子に接続しましょう。

また、FPGA内部の接続にも影響が出てくる場合があるので、クロック入力端子から各種クロックリソースへの接続も必ず確認する必要があります。

いかがでしたか?

このように、端子アサインに関連してさまざまな条件が存在しますので、FPGAでの実現性確認と基板設計での最適化とを繰り返しながら端子を決めていくことが望ましいと考えます。

最後までご覧いただきましてありがとうございました!

これからもブログを通じて、皆様の設計にお役立てできればと思います。

次回のブログもどうぞよろしくお願いいたします。

弊社ではFPGA設計や回路図設計、レイアウト設計、ソフトウェア設計、筐体設計などを受託開発しています。

サービス内容をWEBサイトに掲載していますので、ぜひご覧ください。

FPGAの活用に際して設計検討などありましたら、お気軽にお問い合わせください。