【回路設計ヒント】多ピンFPGA・適応型SoCの回路図CADシンボル作成

みなさんこんにちは

いつの頃からFPGAや適応型SoCもピン数が多いデバイスが増えてきました。

回路設計で新しい部品を使う場合、回路を描く前にシンボルを作らないといけませんが、 ピン数が多い場合(多ピン)のシンボル作成はどのようにしていますか?

通常ですと、シンボルエディタで一つ一つ情報を打ち込んでいるかと思います。この方法はピン数が少なければよいのですが、多くなると間違いも発生しますし時間もかかってしまいます。ちなみにXilinx社の「XCVU19PFSVB3824」というFPGAは3824ピンもあります。

そこで、今回はピン数が多い場合(多ピン)のFPGAおよび適応型SoCのシンボル作成に便利な情報をお届けしたいと思います。

このブログは「FPGA設計ブログ一覧」の

基板設計・評価関連のひとつです。

目次

ピン情報ファイルの取得

ひとつデバイスを挙げて説明していきたいと思います。

中規模クラスのピン数である以下のデバイスを例に説明します。

| メーカー | Xilinx |

|---|---|

| シリーズ | Kintex®-7 |

| パーツナンバー | XC7K325T |

| パッケージ | FBG900 |

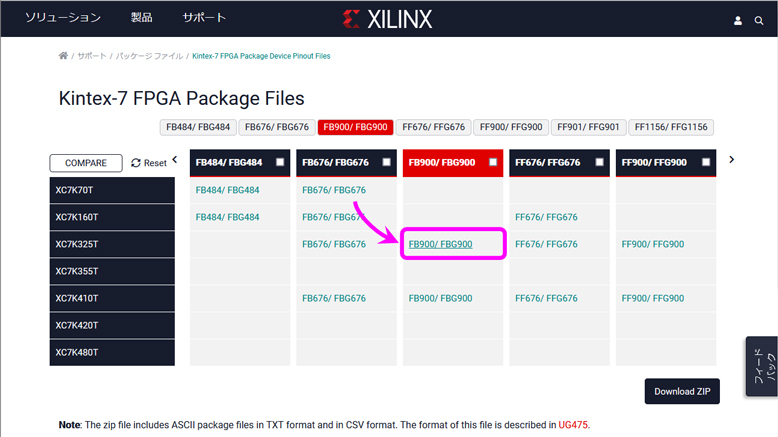

まず、Xilinx社ホームページからターゲットとなるデバイスのパッケージファイルをダウンロードします。

パッケージファイルポータルからターゲットのデバイスKintex®-7を選びます

https://japan.xilinx.com/support/package-pinout-files.html

ターゲットの(左欄)パーツナンバーXC7K325Tと(上欄)パッケージFBG900の交点にあるファイルxc7k325tfbg900pkg.txtをダウンロードします。

https://japan.xilinx.com/support/package-pinout-files/kintex-7-pkgs.html

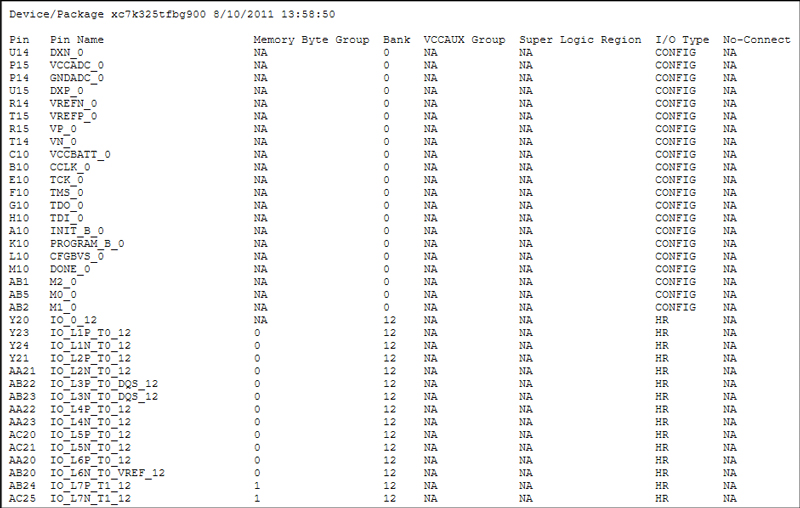

中身はテキストで、このように記載されています。

ファイルの加工

これをExcel等で取り込んで使用するCADツールのフォーマットに加工していきます。

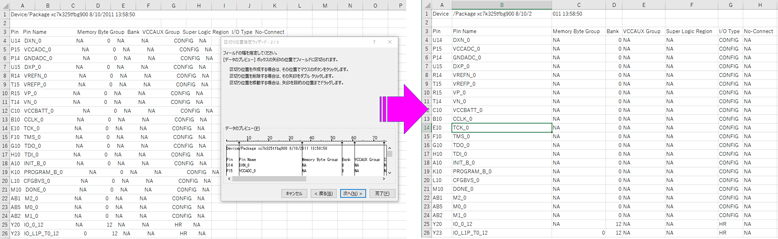

まずダウンロードしたファイルxc7k325tfbg900pkg.txtをExcelに取り込み、加工しやすいようにします。

※画像クリックで大きな画像が表示されます。

※画像クリックで大きな画像が表示されます。

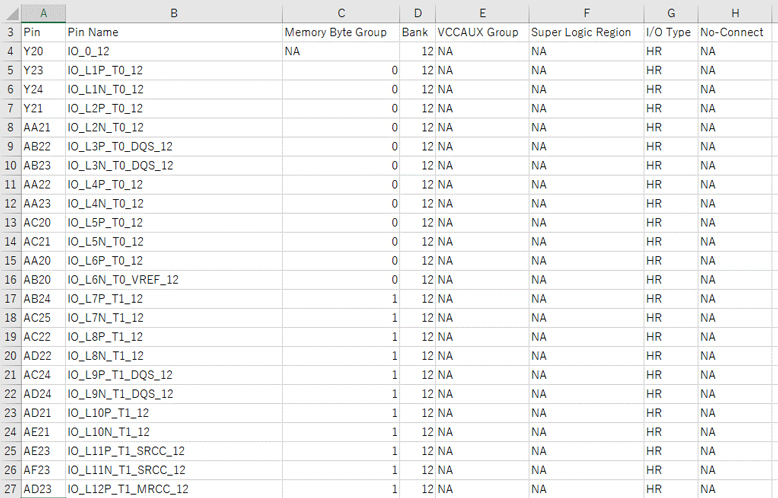

次にピンをシンボルに表示させる順番に並べ替えをしていきます。 筆者の場合、汎用的なシンボルを作るのがほとんどなので基本はBANK→IO_番号P→IO_番号Nの順番にしています。図はBANK12をこの順番で並び替えたものです。

ここから先はCADツールによって加工の仕方が異なります。

なお、ここで入力している情報は例です。実際は所属している部署などのルールに従って入力してください。

Cadence社 OrCAD® Captureの場合

次のように情報を記入していきます。

ファイルを開いたまま次の工程に行きます。

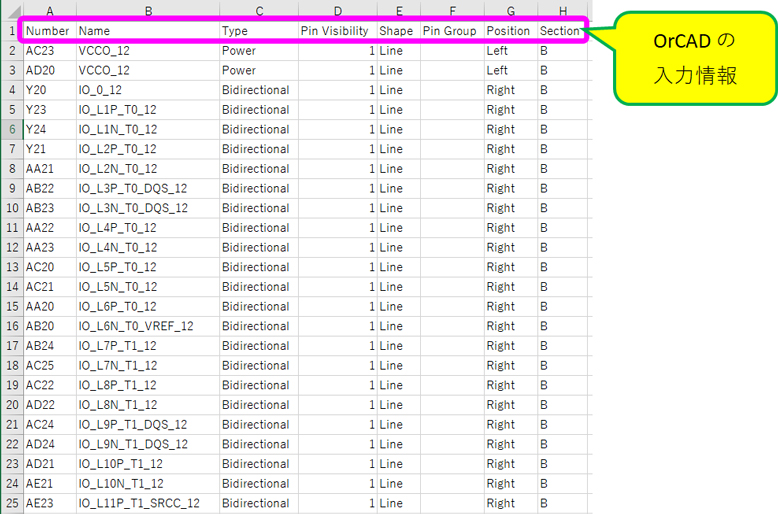

Siemens社 PADS® の場合

次のように情報を記入していきます。

CSVファイルとしてセーブします。

CADツールでの取り込み・シンボル作成

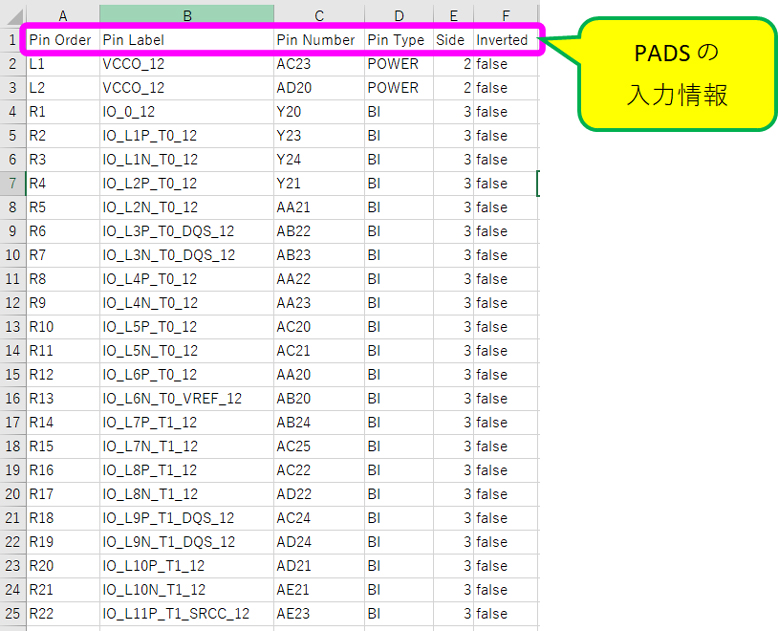

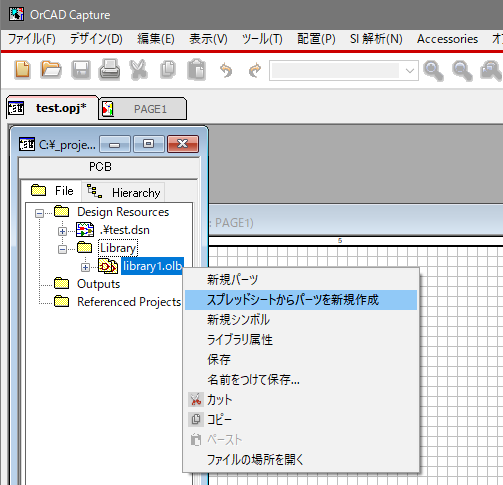

Cadence社 OrCAD® Captureの場合

スプレッドシートから「パーツを新規作成」を実行します。

※ツールの表示を日本語化しています

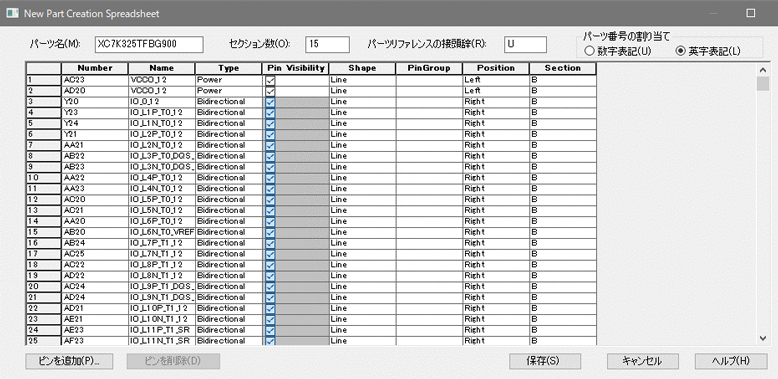

次の画面が表示されるので、上部の設定事項を入力した後、先ほど作ったファイルからセルを選択・コピーをしてこの画面のシートにペーストします。

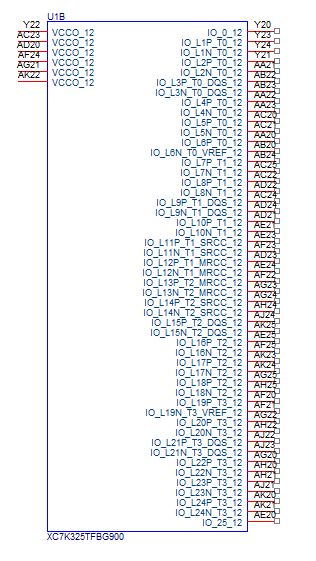

保存を行うとこのような形でシンボルができあがります。

Siemens社 PADS® の場合

「ピンからシンボルを作成」を実行し、先ほど作成したCSVファイルを読み込みます。

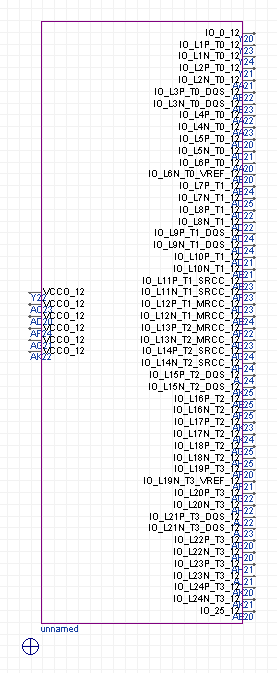

実行後このような形でシンボルができあがります。

いかがでしたでしょうか?

汎用的ではなくプロジェクト毎にシンボルを作成するのであればFPGAや適応型SoCのツールが出力するピンレポートファイルを利用するのもよいでしょう。

もちろんFPGAや適応型SoCだけではなく、CPUやDSPなど他のデバイスでピン数が多い場合(多ピン)でも有効です。メーカーが提供するピン情報が利用できれば間違いもなく時間の短縮につながります。

これからもTECHブログを通じて、皆様の設計にお役立てできればと思います。次回のブログもどうぞよろしくお願いいたします。

このブログは「FPGA設計ブログ一覧」の

基板設計・評価関連のひとつです。

尚、CADツールについてはお使いのCADメーカーにお問い合わせください。

最後までお付き合いいただきありがとうございました。

このブログのシリーズ