【回路設計ヒント】どうする?FPGAの端子アサイン ~ユーザーI/O編~

皆さん、こんにちは。

FPGAの端子アサインはどのように決定していますか?

- FPGA設計者が主体で決めている

- 回路(基板)設計者が主体で決めている

- FPGAも回路も一人で両方担当している

などさまざまなケースがあると思います。

一人で両方を行っている場合には臨機応変に修正対応が可能ですが、分業している場合には

- FPGA設計者が決めると「パターンの引き回しが考慮されない」

- 回路設計者が決めると「FPGAの機能や仕組みが考慮されない」

といった課題が発生することがあります。

中でも最も困るのは、基板が完成したにもかかわらず、端子アサインが原因でVivado™やISE®での合成が通らず、実機が動作しなかったり、基板の作り直しが必要になったりするケースです。

そこで、FPGAを使い始めた方やFPGA内部をあまりご存じない方に向けて、FPGAの端子アサインに関するヒントを紹介したいと思います。

それでは、はじめましょう。

目次

ここで掲載している図表は例として挙げています。

すべてのデバイスシリーズに当てはまるわけではありません。

必ずご使用になるデバイスシリーズのデータシートで内容をご確認ください。

パッケージ上の距離 ≠ 内部配線長

パッケージ上で端子が近接していても、他の端子とタイミングが異なる経験はありませんか?

このような現象にはさまざまな要因がありますが、その代表的な例を見てみましょう。

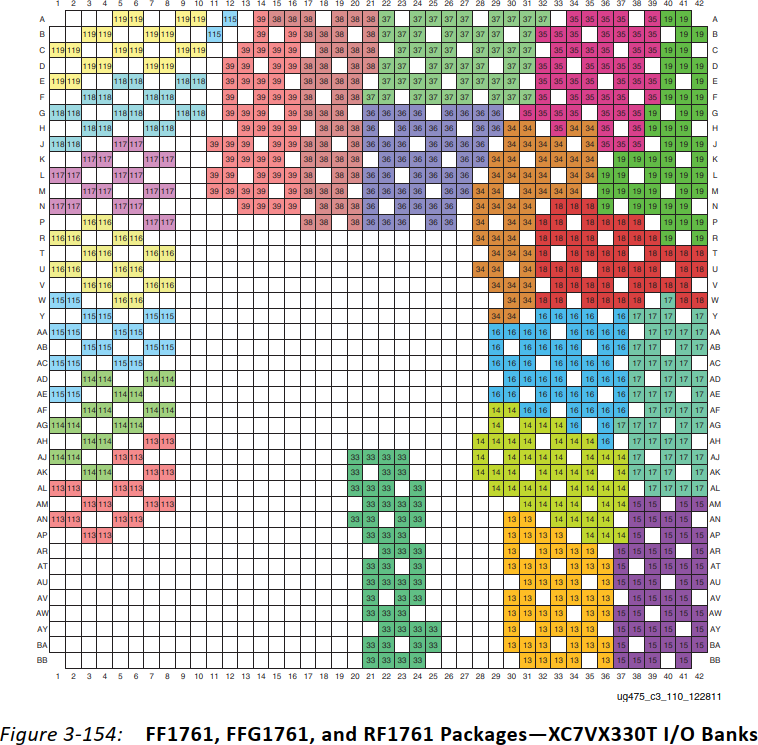

例えば、AMD社のVirtex™ 7 シリーズのXC7VX330T FFG1157を例に説明します。

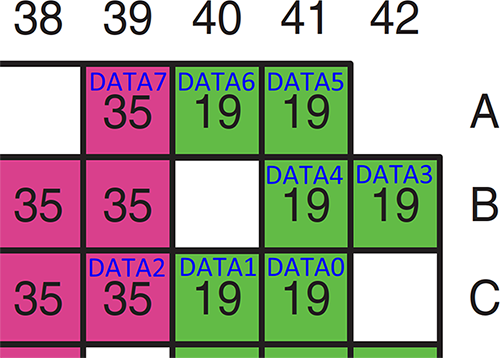

8bitのデータバス信号(DATA0~7)があり、その6端子をI/O BANK19(C41,C40,B42,B41,A41,A40)に配置し、PCBのパターン配線を最適化するため、残りの2端子をI/O BANK35(C39,A39)に配置したケースを考えてみます。

出典:

UG475 7 Series FPGAs Packaging and Pinout Product Specification <P.185> (参照 2024/11/25)

ちなみに、ユーザーI/Oの全体はこのようになっています。

出典:

UG475 7 Series FPGAs Packaging and Pinout Product Specification <P.185> (参照 2024/11/25)

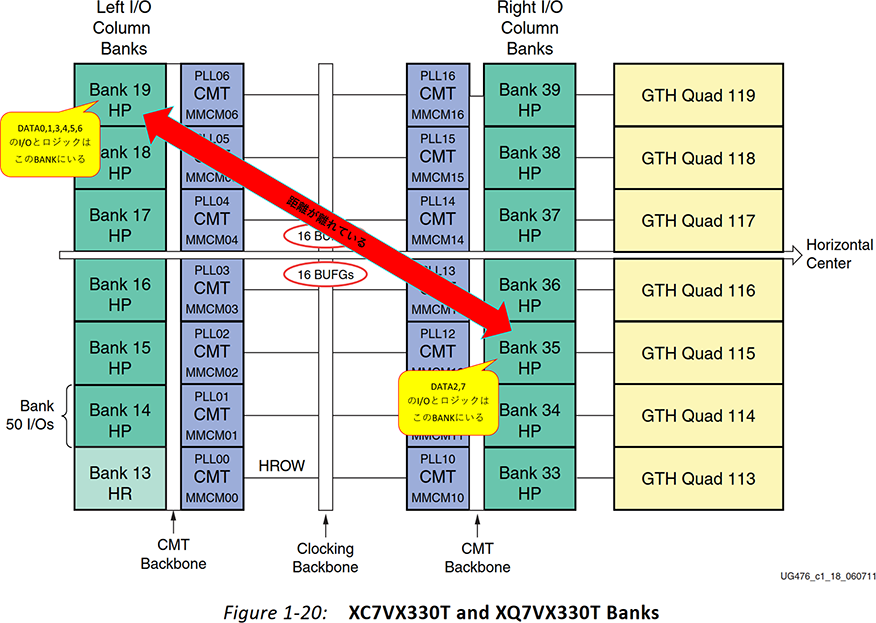

次の図はFPGA内部の各機能(ロジックやI/O)の位置を簡易的に表したものです。

図から分かるように、BANK19とBANK35はチップ上でかなり離れた位置に配置されています。

このため、制御ロジックがBANK19に集中している場合、BANK35に配置された信号との接続には長い配線経路が必要となります。

その結果、配線長の違いにより信号間でタイミングの差異が生じる可能性があります。

出典:

UG475 7 Series FPGAs Packaging and Pinout Product Specification <P.50> (参照 2024/11/25)

機能端子

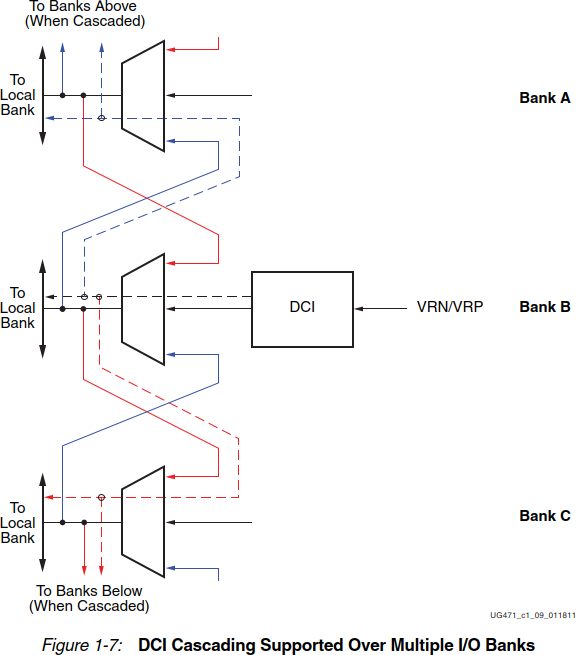

I/Oスタンダードやオプション設定によって、ユーザーI/Oから専用機能端子へと役割が変更される端子があります。代表的な例として、Vref入力や内部終端(DCI:Digitally Controlled Impedance)用のリファレンス抵抗の接続などが挙げられます。これらの端子は配置位置が固定されているため、優先的に割り当てを行う必要があります。

なお、内部終端用のリファレンス抵抗については、特定の条件下で近接するI/O BANKでもリファレンス抵抗を共有(カスケード接続)できるため、必要な接続数を削減できる場合があります。ただし、この仕様はデバイスシリーズによって異なりますので、詳細は各デバイスのセレクトI/Oリソースユーザーガイドで確認してください。

例えば、AMD社の7シリーズは次のようになっています。

出典:

UG471 7 Series FPGAs SelectIO Resources User Guide <P.23> (参照 2024/11/25)

指定端子

IPやハードマクロによっては端子を指定している場合や専用端子が用意されているもの、専用端子が実装されているものがあります。最近のデバイスでは、AD変換入力、Vref入力、内部終端用のリファレンス抵抗接続端子などがこれに該当します。

また、パラレルPCI(PCIeではなく)のIPコアでは、IRDY/TRDY信号用の端子が指定される場合があります。

これらの端子は、FPGA内部の接続構造やパフォーマンスの要件により、配置位置を変更することができません。そのため、端子割り当ての際は、これらを優先的に確定する必要があります。

設計検証

開発初期段階でも、使用予定の全端子を仮割り当てした状態で、未使用端子が削除されない設計データを作成し、Vivado™やISE®でインプリメンテーションを実行することを推奨します。その際、警告メッセージの確認も重要ですが、必ず「Generate Bitstream」まで完了させてください。

なお、論理合成や配置配線が成功しても、最終段階の「Generate Bitstream」生成時にルール違反が判明し、エラーが発生する場合があります。

まとめ

- バスの信号は基本的に1つのI/O BANKにまとめて配置するのがよいでしょう。

- 信号数が多く複数のI/O BANKに割り当てる場合には、I/O BANKが内部で縦に隣接しているバンク(例えば、BANK14とBANK15)にある程度のまとまりをもって(例えば、データバスが32ビットだった場合、ビット0~15をBANK14、ビット16~31をBANK15)配置するとよいでしょう。

- 機能的に端子が指定されている場合や、ユーザーI/Oから機能が変わる端子は優先して配置しましょう。

おわりに

いかがでしたか?

このように、端子配置に関連してさまざまな条件がありますので、FPGAでの実現性確認と、基板設計での最適化とを繰り返して端子を決めていくことが良いと思います。

最後までご覧いただきましてありがとうございました!

これからもブログを通じて、皆様の設計にお役立てできればと思います。

次回のブログもどうぞよろしくお願いいたします。

弊社ではFPGA設計や回路図設計、レイアウト設計、ソフトウェア設計、筐体設計などを受託開発しています。

サービス内容をWEBサイトに掲載していますので、ぜひご覧ください。

FPGAの活用に際して設計検討などありましたら、お気軽にお問い合わせください。