【回路設計ヒント】Spartan®-6 FPGA ファミリから Spartan®-7 FPGA ファミリへの置き換え ~A/Dコンバータ・DDRメモリインタフェース編~

みなさんこんにちは。AMD ザイリンクス社のSpartan®-6 FPGAファミリから Spartan®-7 FPGAファミリへの置き換えの需要が高まってきています。

そこで5回にわたって、回路設計の観点で置き換え時のポイントをあげていきたいと思います。

今回は4回目で、A/DコンバータとDDRメモリインタフェースに着目します。

※引用した参考資料のページ数はバージョンにより異なる場合がございますので、予めご承知おきください

A/Dコンバータ

今まで上位デバイスでサポートされていたA/DコンバータがXC7S25以上のパッケージにも搭載されています。

本格的にA/Dコンバータをご使用になりたい場合にはこちらをご覧ください。

[UG480] 7 Series FPGAs and Zynq-7000 SoC XADC Dual 12-Bit 1 MSPS Analog-to-Digital Converter User Guide

このブログは「FPGA設計ブログ一覧」の

Spartan®-6 FPGAファミリの置換 の

ひとつです。

目次

それでは、始めましょう。

電源接続

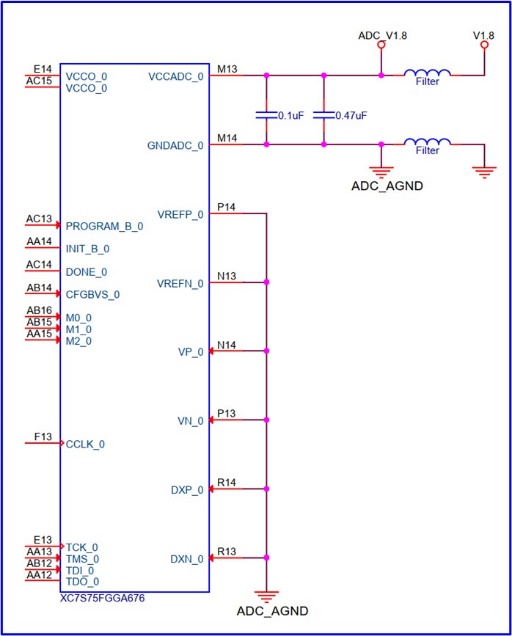

A/Dコンバータが未使用の場合でも電源VCCADC_0にVCCAUXと同じ1.8Vを接続する必要があります。

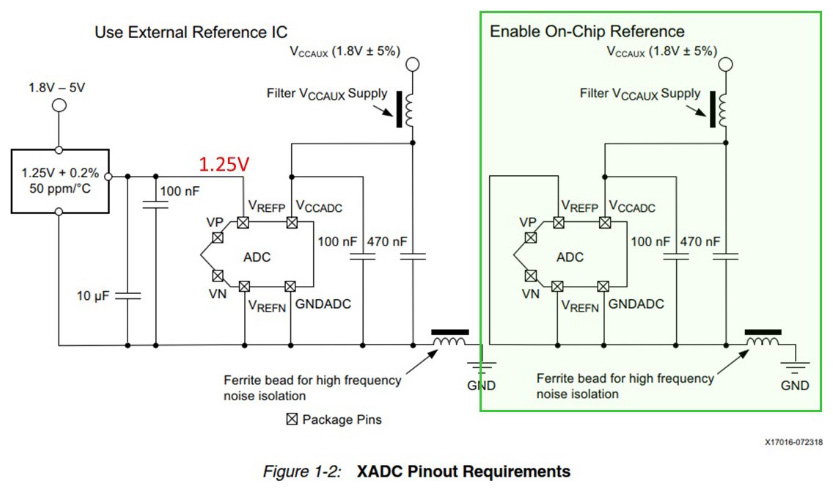

基本的な使用では、下右図の内部の基準電圧を使用する構成で使用します。

A/Dコンバータを高精度で使用することを希望される場合には、以下の図の構成のように外部リファレンスVREFPに高精度の1.25Vを接続してください。

※画像クリックで大きな画像が表示されます。

図1 XADCピン配置の要件について

出典:UG480 (1.10.1) 7 Series FPGAs and Zynq-7000 SoC XADC Dual 12-Bit 1 MSPS Analog-to-Digital Converter User Guide<P.8>

https://docs.amd.com/r/en-US/ug480_7Series_XADC/XADC-Overview

(参照 2022-07-11)

※画像クリックで大きな画像が表示されます。

図2 内部の基準電圧を使用する場合の電源接続回路例

DDRメモリインタフェース

ここで掲載している内容は、AMD ザイリンクス社のメモリインタフェースIPを使用することを前提としています。

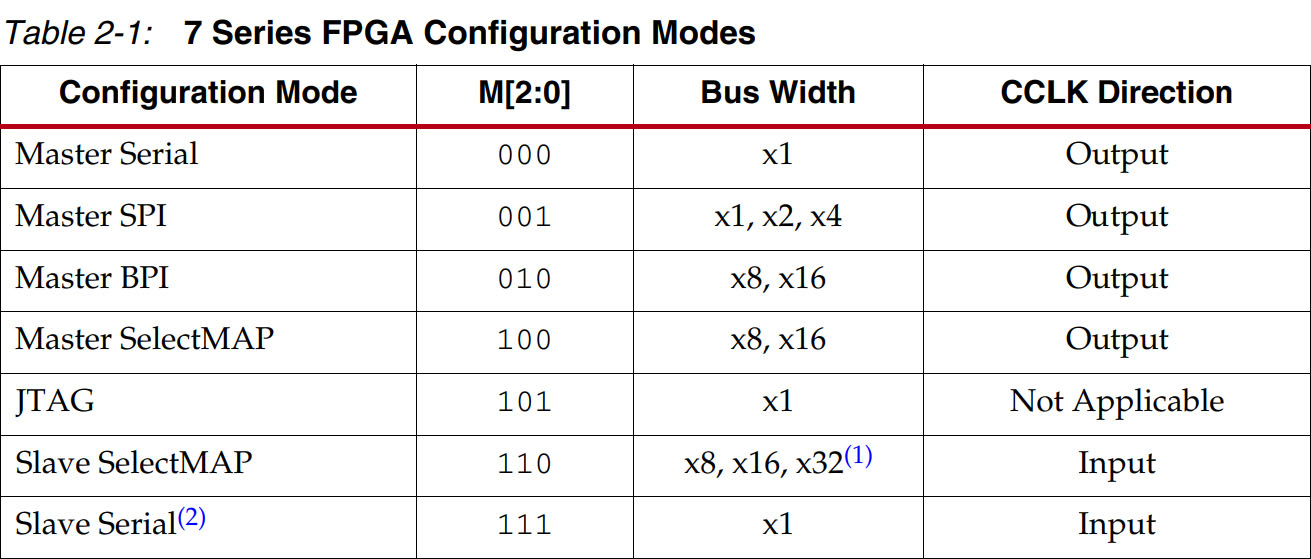

Spartan®-6 FPGAファミリではDDRメモリの専用ハードマクロが搭載されていましたが、Spartan®-7 FPGAファミリではソフトIPとなるため、その分のリソースが必要となります。

また、ユーザー側のインタフェースも変更になるため修正が必要となります。

詳しくは [UG586] Zynq-7000 SoC and 7 Series Devices Memory Interface Solutions User Guide

でご確認ください。

サポートするメモリ規格

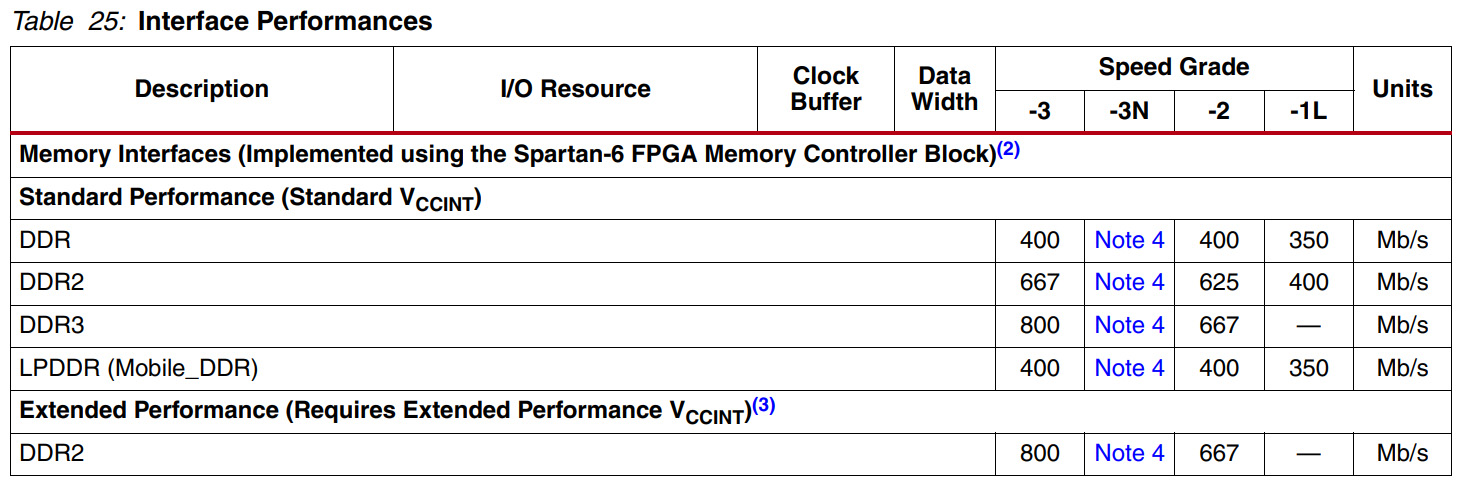

Spartan®-6 FPGAファミリで使用できたDDR(1)とLPDDR(1)はサポートされていないため、別の規格のメモリに変更する必要があります。

※画像クリックで大きな画像が表示されます。

出典:DS162 (v3.1.1) Spartan-6 FPGA Data Sheet : DC and Switching Characteristics<P.18>

https://japan.xilinx.com/content/dam/xilinx/support/documentation/data_sheets/ds162.pdf

(参照 2022-07-11)

出典:DS189 (v1.9) Spartan-7 FPGAs Data Sheet : DC and AC Switching Characteristics<P.15>

https://japan.xilinx.com/content/dam/xilinx/support/documentation/data_sheets/ds189-spartan-7-data-sheet.pdf

(参照 2022-07-11)

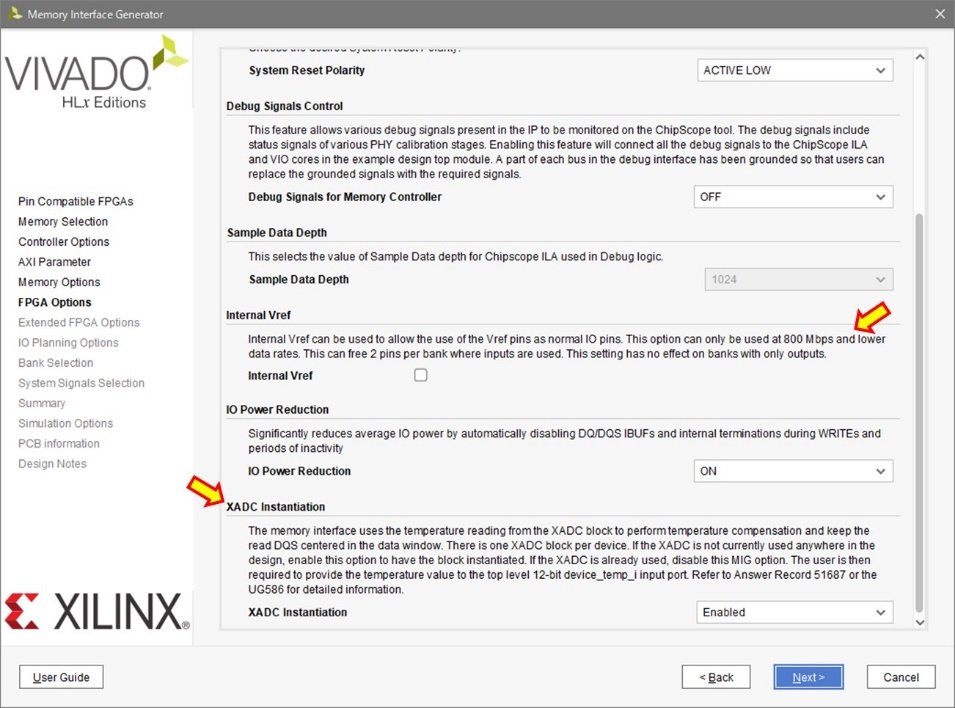

Vrefと位相調整

転送レートが800Mbps以下の場合は内部VREFが使用でき、空いた端子をUSER I/Oとして使用することができます。(デフォルトは無効になっています)

A/Dコンバータで温度を監視してDQS信号の位相調整を行うことができます。(デフォルトは有効になっています)

どちらもIPの中で設定するので、FPGA内部をデザインされる方と調整をしてください。

出典:Vivado HLx Edition (v2020.2.1) / Memory Interface Generator (MIG 7 Series Ver. 4.2 Rev. 1)

端子アサインの変更

配置やパターンの都合上、メモリインタフェースの端子を入れ替えた場合は、AMD ザイリンクス社のIPがアサイン可能なものになっているか必ずVIVADO®のMemory Interface Generatorでご確認ください。

メモリインタフェース用クロック

メモリインタフェースで使用するクロックは、基本的に使用するメモリインタフェースが含まれるBANKに接続します。

ほかのBANKでもアサイン可能ですが、制限がありますので詳細はユーザーガイド [UG586] Zynq®-7000 SoC and 7 Series Devices Memory Interface Solutions User Guide

に書かれているデザインガイドでご確認ください。

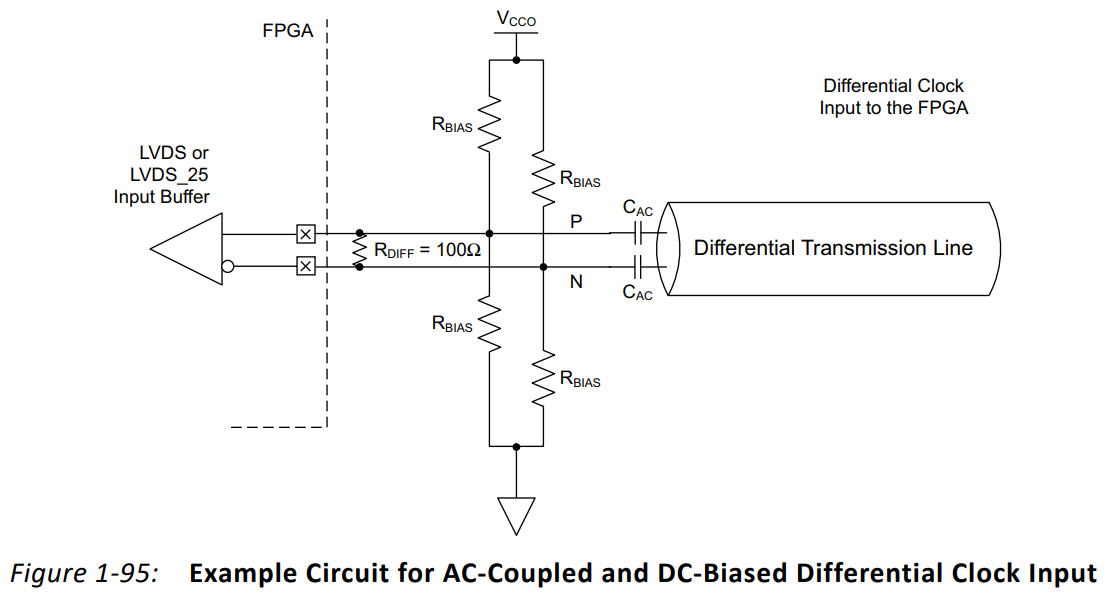

また、接続するBANKとクロック信号の規格が合わない場合には次のような方法で接続してください。

※画像クリックで大きな画像が表示されます。

出典:UG586 (v4.2) Zynq-7000 SoC and 7 Series Devices Memory Interface Solutions User Guide<P.212>

https://japan.xilinx.com/content/dam/xilinx/support/documentation/ip_documentation/mig_7series/v4_2/ug586_7Series_MIS.pdf

(参照 2022-07-11)

パターン設計ガイド

パターン設計については各種ガイドが出ていますのでご参照ください。

- [UG586] Zynq-7000 SoC and 7 Series Devices Memory Interface Solutions User Guide

- [WP484] DDR2/DDR3 Low-Cost PCB Design Guidelines for Artix-7/Spartan-7 FPGAs White Paper

- [XTP306] MIG IP 7 Series Design チェックリスト

いかがでしたでしょうか?

お役に立てましたら幸いです。

まとめ

- A/Dコンバータへの電源接続は必須

- 使用できるメモリの種類が変更になっている

- DDRメモリ専用ハードマクロからソフトIPに変わるため内部のインタフェースも変更する

- Vref端子はFPGA外部から供給するか、FPGA内部のものを使うか、決める必要がある

最後までお付き合いいただきありがとうございました。

このブログは「FPGA設計ブログ一覧」の

Spartan®-6 FPGAファミリの置換 の

ひとつです。