【回路設計ヒント】IBISモデルの出力

みなさんこんにちは

SIシミュレーションを行う際に各部品のIBISモデルを集めるわけですが、部品が多くなると大変ですよね。ましてやFPGAのような端子数も多くオプションもたくさんあるデバイスだと各端子への設定指示も大変になりますよね。

今回のブログでは、Xilinx社ホームページからIBISモデルをダウンロードして使用する方法ではなく、設計ツールVivado® Design Suiteから各端子の設定情報付きでIBISモデルを出力する方法を紹介したいと思います。

このブログは「FPGA設計ブログ一覧」の

基板設計・評価関連のひとつです。

目次

準備

まず、デザインのソースとConstraintsファイル(.xdc)を用意します。

デザインは仮のものでもよいですが、トップデザインに必要な端子をすべて記述するようにしてください。

Constraintsファイルには必要な端子のアサインとIO Standardの設定をしてください。

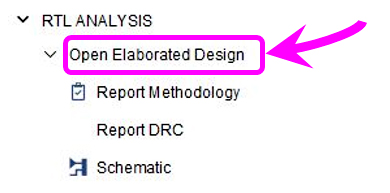

これらのファイルをVivado® Design Suiteに設定し、RTL ANALYSIS (Open Elaborated Design)を実行します。

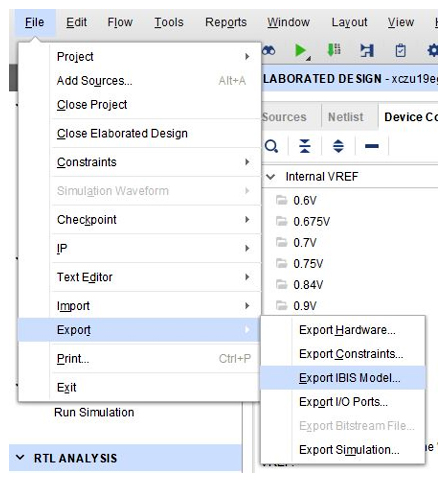

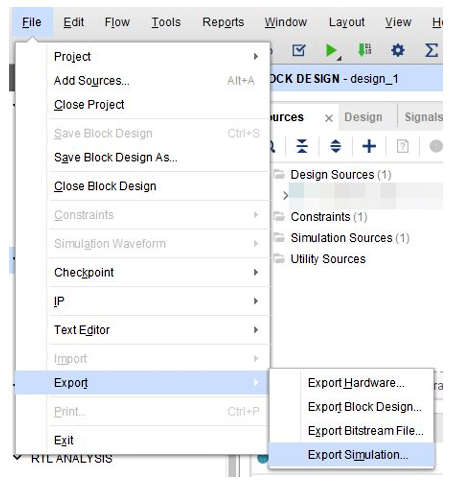

次にRTL ANALYSIS実行後にFile→Export→Export IBIS Modelを実行します。

なお、既にインプリメンテーションまで終わっている方もRTL ANALYSIS を実行してください。そうでないとExportにExport IBIS Modelは表示されません。

出力

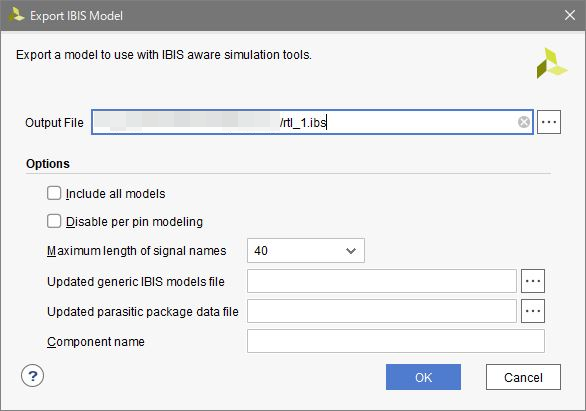

Export IBIS Modelを実行すると次のウィンドウが表示されますので、出力先と名前を設定して実行してください。

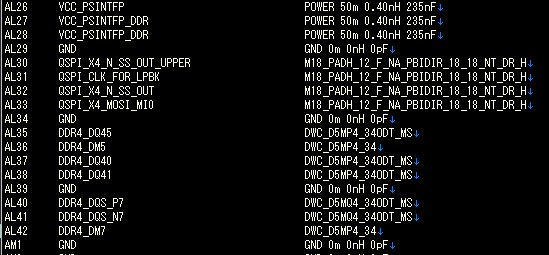

実行後ファイルを覗くとこのような感じになっています。

いかがでしたでしょうか?

これからもTECHブログを通じて、皆様の設計にお役立てできればと思います。次回のブログもどうぞよろしくお願いいたします。

なお、今回使用したVivado® Design Suiteのバージョンはv2020.2.1 です

最後までお付き合いいただきありがとうございました。

このブログは「FPGA設計ブログ一覧」の

基板設計・評価関連のひとつです。