【Versal™ ACAP】機能紹介 NoC編

みなさんこんにちは。

Xilinx社からVersal™が発表されてから2年ほど経ちますが、当社でも徐々にVersal™ ACAPにふれたという声を聞くことが増えています。

Versal™ ACAPにふれるモチベーションとしては、AIE(AI Engine)とプロセッシングシステム(PS)の活用や、5G、100G Etherなどハードウェア面での活用などをあげられます。

今回のTECHブログでは、それらを繋ぐインターフェースであるNoC (Network on Chip)について紹介します。

次回以降、実際の設計ツール上での使用方法について説明したいと思います。

ご不明点などございましたら、本ページ下部からお気軽に問い合わせいただければと思います。

それでは、始めましょう。

このブログは「FPGA設計ブログ一覧」の

Versal Acap関連のひとつです。

目次

NoCの概要

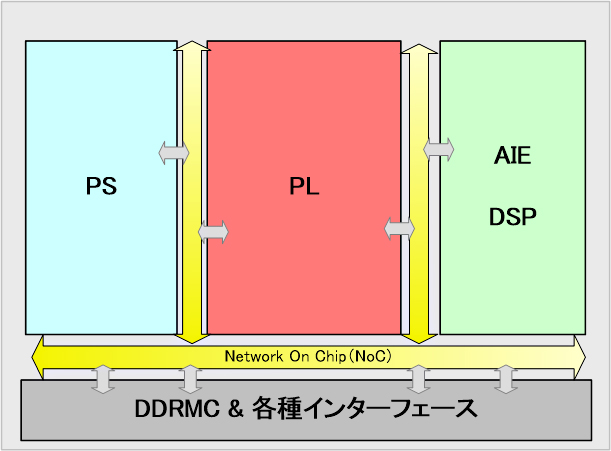

NoCとはVersal™ ACAPに搭載されている機能のひとつで、AIEやPS、プログラマブルロジック (PL) などを繋ぐインターコネクト (AXI4など) を指します。

これまでは、機能ブロック (IP) として Xilinx社のFPGAではSmart Connectなどが使われていましたが、それに機能は類似しています。

また、Versal™ ACAPは今後も新たなシリーズがリリースされていく予定で、NoCはVersal™ACAP共通の機能として備わっています。

NoCの接続先例としては以下があげられます。

- DDRメモリへのアクセス

- PL同士の接続

- AIEへのアクセス

- PSとPLの接続

- PSとDDRの接続

AIEとPS、PLの既存機能を繋ぐだけではなく、高帯域の一面も持ち、数Tbps (Tera bit per second)の帯域を持ちます[1]。

こちらについては、次項にて説明します。

NoCを使うメリット

現時点では、低速ならこれまで通りSmart Connect でいいと考えている方や、AIEを使わないから用がないという方もいらっしゃるかもしれませんが、 その前にNoCを使うことで得られるメリットを見てみましょう。

リソース活用

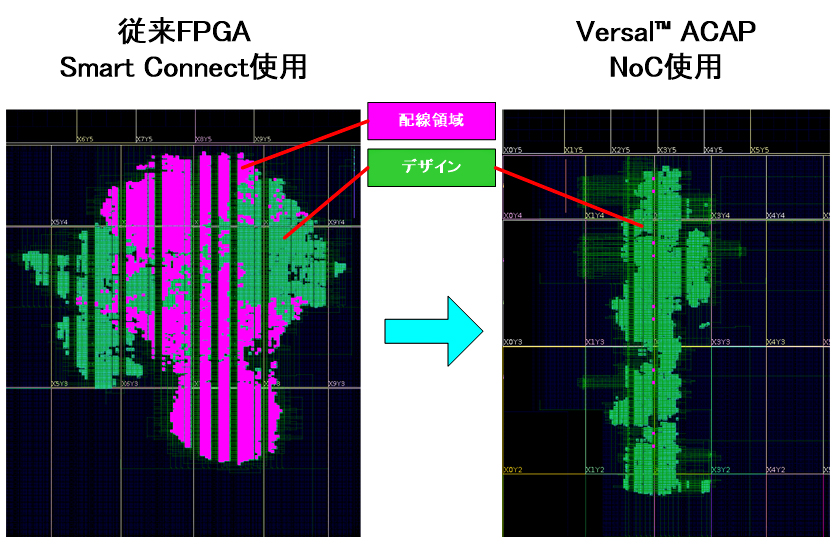

NoCがこれまでのインターコネクトと異なる点として、ハードマクロであることがあげられます。

これはNoCの経路はあらかじめVersal™ ACAP内に組み込まれているため、インターコネクト接続時にはPLをほぼ消費しなくなります。

これにより近年の微細化大規模化で課題としてあがる配線問題の対策になります。また、NoCを使用することによって、設計ツール上での通信時間や消費電力の予測が容易となります。

※画像はイメージになります。

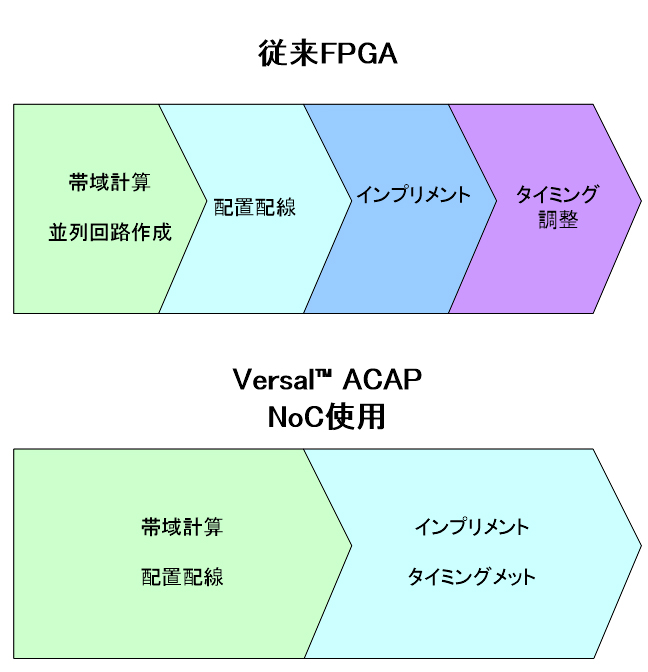

速度、タイミング保障

これまでのFPGAでは、DDRメモリの帯域を活用したいけれどインターコネクトIPの速度がネックとなり、バッファなどを使用して並列演算などの工夫が必要な場面がたびたび見られます。

しかし、NoCは先にも記した通り、数Tbpsの帯域を持っているため、その分設計が容易となり、設計工数の減少へとつながります。

また、ハードマクロであるためタイミングが保障されており、こちらもあわせて時間の短縮につながります。

NoCの導入難易度

NoCの導入メリットだけではなく、NoC導入の難易度を気にされる方も多いのではないでしょうか。

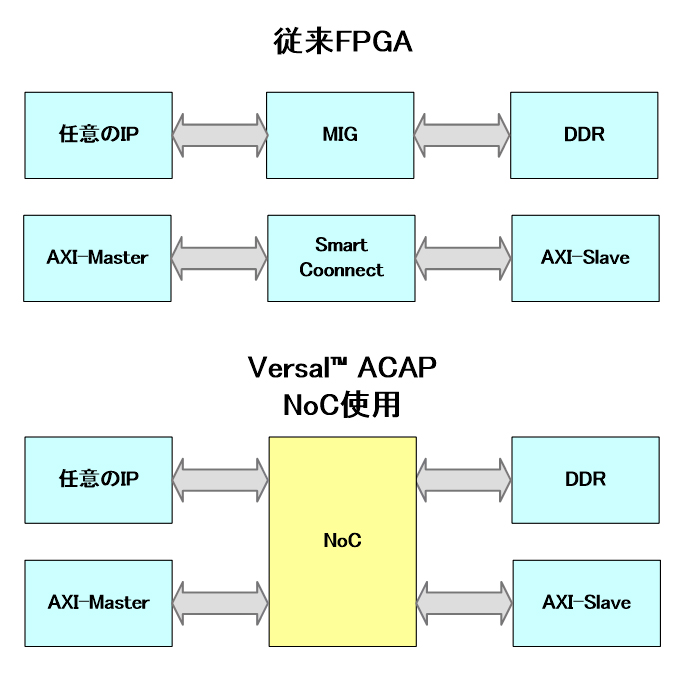

NoCの導入難易度は低く、Vivado® Design Suite上ではIPとして使用します。

複雑な設定などはありませんが、DDRメモリなどに接続する際には、MIGと同様に設定する必要はあります。

基本的には、NoCの位置づけとしては、MIG と Smart Connectというイメージになります。

既にある程度想像がついている方もいらっしゃるかもしれませんが、実際の設計画面については、次回以降でお話します。

おわりに

今回は、Versal™ ACAPの機能のひとつであるNoCについて紹介しました。

次回以降では、Vivado® Design Suiteを通じて実際に使用する様子を紹介できればと思います。

Versal™ ACAPの機能はNoCだけでなく、AIEなど気になる機能は他にもあるかと思いますので、これからもTECHブログを通じて、わかりやすくお伝えできればと思います。

次回のブログもどうぞよろしくお願いいたします。

調査依頼や、設計検討などありましたら、弊社デザインサービス事業までお気軽にお問い合わせください。

このブログは「FPGA設計ブログ一覧」の

Versal Acap関連のひとつです。

最後までお付き合いいただきありがとうございました。

[1] Versal™ ACAP AI Core Series Product Selection Guide

https://japan.xilinx.com/products/silicon-devices/acap/versal.html