【Versal™ACAP】MIPI Example Design【Vivado® ML 2021.1】

みなさんこんにちは。

今回は、MIPIのカメラモジュール、LI-IMX274MIPI-FMCを使ってVersal™ AI コア シリーズ VCK190 評価キット上でMIPI Example Designを動かしてみました。

LI-IMX274MIPI-FMCデータシートはこちら

https://www.leopardimaging.com/uploads/LI-IMX274MIPI-FMC_datasheet.pdf

動作が確認できるまでの過程や注意点をまとめましたので紹介します。

それでは、始めましょう。

このブログは「FPGA設計ブログ一覧」の

Versal Acap関連のひとつです。

目次

今回は、以下の環境で実行します。

- ・HostPC CentOS 7.6

- ・Vivado® ML Edition 2021.1

- ・Vitis™ 2021.1

Vivado® ML Edition

それではデザインを作成していきます。

基本的に、詳細はpg232-mipi-csi2-rx.pdf[1]に記載されているので、大まかな流れと注意点に絞って記載していきます。

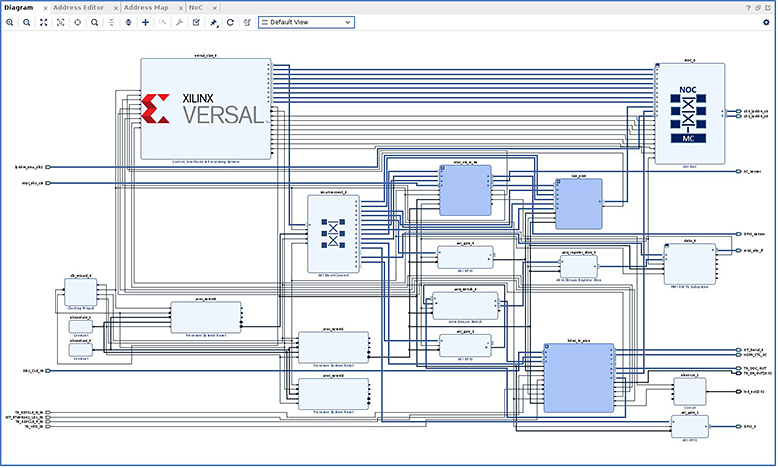

Select Deviceにて「Versal VCK190 ES1 Evaluation Platform」を選択したプロジェクト生成後、IP Catalogから「MIPI CSI-2 Rx Subsystem」を生成し、右クリック ⇒ Open IP Example Designを実行します。

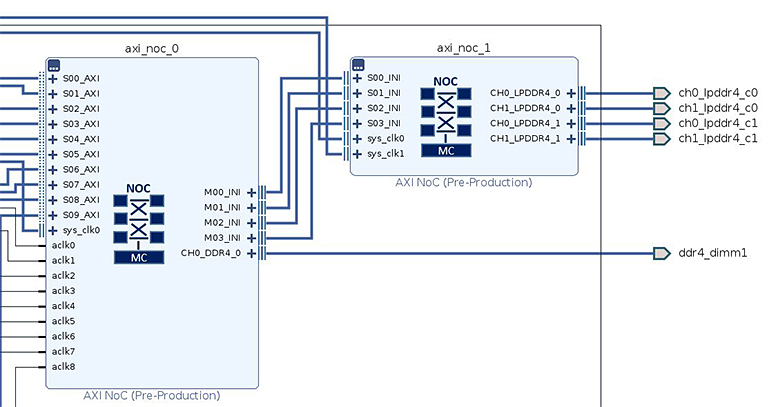

以下図のようなデザインが生成されます。

出典:Vivado® ML Edition

注意点①

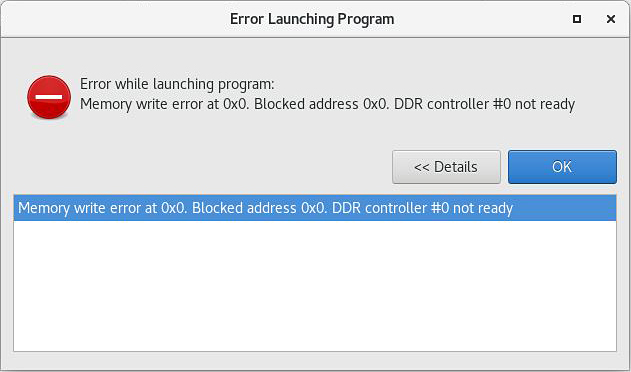

デザインそのままのLPDDR4単体とアドレス設定では、この後の手順でElfファイルの実行時に以下のようなエラーが出ます。

「Memory write error at 0x0. Blocked address 0x0. DDR controller #0 not ready」

以下の図はCIPSとNoC ⇔ LPDDR4を繋いだだけのデザインでHello Worldを実行したときの様子です。

出典:Vivado® ML Edition

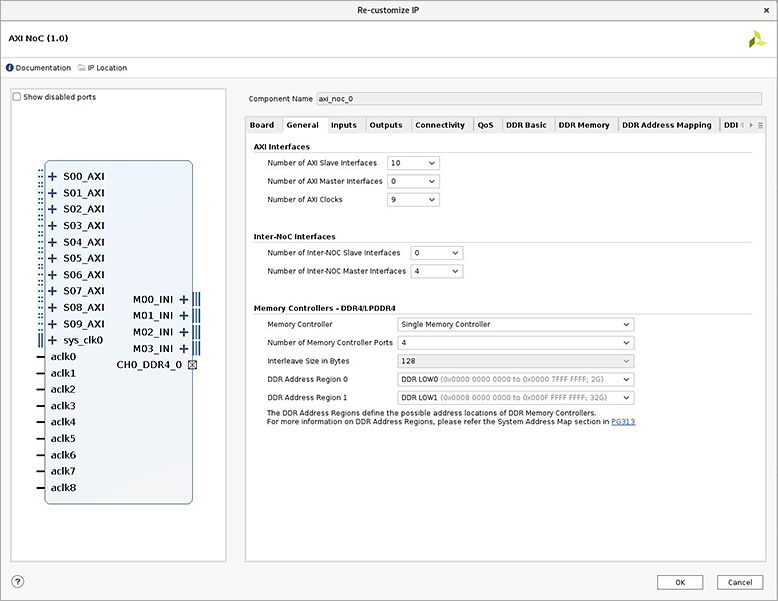

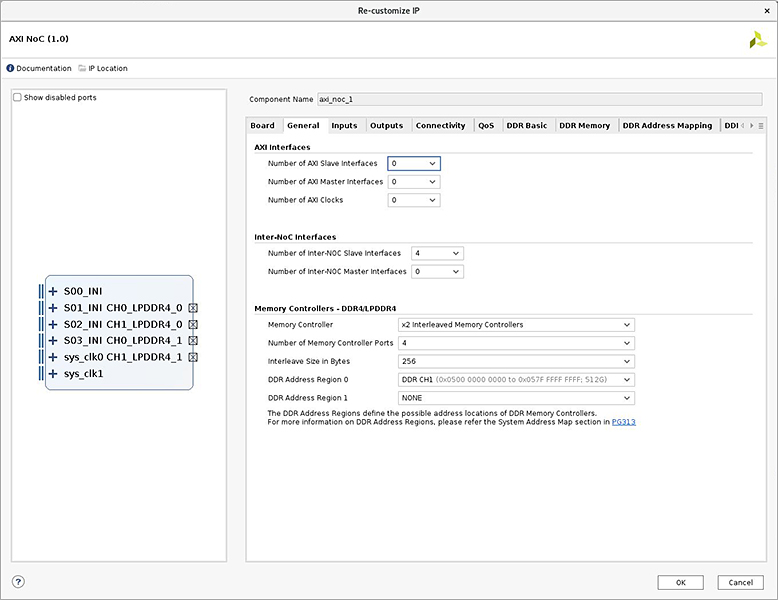

今回は注意点①の対応策として、NoCにDIMMとLPDDR4の両方を加えます。

Vivado® ML EditionのデザインでNoCの設定をする際に、

「General」⇒Memory Controllers - DDR4/LPDDR4 を以下のように割り振ります。

・DIMM

- DDR Address Region 0:DDR LOW0

- DDR Address Region 1:DDR LOW1

・LPDDR4

- DDR Address Region 0:DDR CH1

- DDR Address Region 1:None

※画像クリックで大きな画像が表示されます。

出典:Vivado® ML Edition

※画像クリックで大きな画像が表示されます。

出典:Vivado® ML Edition

※画像クリックで大きな画像が表示されます。

出典:Vivado® ML Edition

注意点②

VCK190でDIMMを使用したデザインをVitis Baremetalで操作する際は、インプリメントする前に以下のコマンドをTclで打ち込む必要があります。

set_param noc.enableNOCClockGating 0詳細は以下リンク[2]を参照してください。

インプリメント完了後、HW ExportでXSAを生成します。

※インプリメント時にエラーが出てしまう場合は、CIPSおよびNoCを作り直してインプリメントしてみてください。

Vitis™

Platform Project作成します。

Platform Project作成後、

platform.spr > Board support package > mipi_csi_rx_ss_csirx_0

のImport Exampleから「xmipi_vcl190_example」を選択します。

Build完了後、実行に移ります。

実行

今回はOSがCentOS 7.6なので、ここからは端末上から操作します。

注意点③

Versal向けのコマンドはpg232に記載されていないので、代わりとしてHDMI Exampleデザインのpg235[3]を参照しています。

注意点④

VCK190のSystem Controllerのバージョンが古い場合、Vadjの設定が必要となるので、以下リンク[4]からバージョン2.1以降のSystem ControllerをVCK190"裏面"のmicro SDカードに書き込む必要があります。

https://xilinx-wiki.atlassian.net/wiki/spaces/A/pages/973078551/BEAM+Tool+for+VCK190+Evaluation+Kit

Exampleデザインの階層にCurrent Directoryで移動します。

$cd ./<IP instance name>_exその後、システムデバッガーを使うため、xsdbを起動します。

$ vivado -mode tcl

Vivado% xsdbJTAGターゲットをリストします。

xsdb% targets

1 Versal vjtag40

2 RPU (PS POR is active)

3 Cortex-R5 #0 (PS POR is active)

4 Cortex-R5 #1 (PS POR is active)

5 APU (FPD domain isolation)

6 Cortex-A72 #0 (FPD domain isolation)

7 Cortex-A72 #1 (FPD domain isolation)

8 PPU

9 MicroBlaze PPU (Sleeping after reset)

10 PSM

11 PMC

12 PL

13 DPCPDIをダウンロードします。

xsdb% device program ./<IP instance name>_ex.runs/impl_1/design_1_wrapper.pdi

xsdb% after 1000ターゲットプロセッサをセットします。

xsdb% targets -set -filter {name =~ "Cortex-A72 #0"}

xsdb% rst -proc

xsdb% after 1000.elfをダウンロードします。

xsdb% dow ./<vitis_workspace>/<application_name>_1/Debug/<application_name>_1.elf実行します。

xsdb% conXSDBを出るときは、以下を実行します。

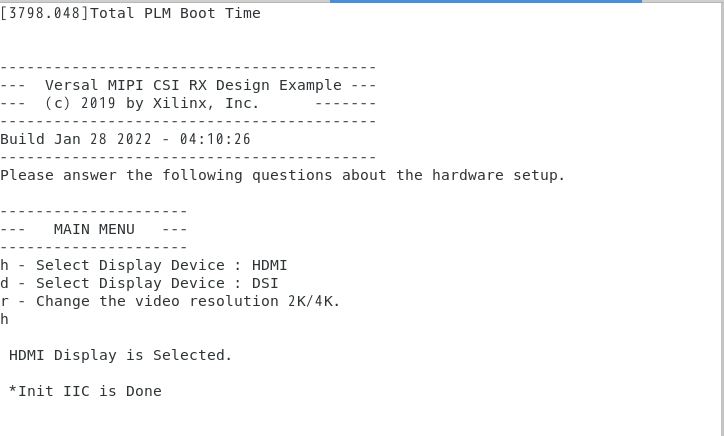

xsdb% exitcon実行後、シリアルコンソールに以下のような状態が表示され、出力先選択後にMIPIのカメラの映像が映りました。

出典:シリアルコンソール画面

(※モニターが緑っぽいですが、カメラ側の設定のようです。)

おわりに

今回は、Versal™ AI コア シリーズ VCK190 評価キットでMIPI Example Designの実機確認と実行までの注意点について解説しました。

別インターフェースのExampleデザインについても、ブログを通じてお伝えできればと思いますので、次回のブログもどうぞよろしくお願いいたします。

調査依頼や、設計検討などありましたら、弊社デザインサービス事業までお気軽にお問い合わせください。

最後までお付き合いいただきありがとうございました。

このブログは「FPGA設計ブログ一覧」の

Versal Acap関連のひとつです。

- 参考文献

-

[1]MIPI CSI-2 Receiver Subsystem Product Guide

https://japan.xilinx.com/content/dam/xilinx/support/documentation/ip_documentation/mipi_csi2_rx_subsystem/v5_1/pg232-mipi-csi2-rx.pdf

[2]Cannot run a bare-metal PS application with Cortex A72 using Vitis IDE on VCK190

https://support.xilinx.com/s/question/0D52E00006ihQLlSAM/cannot-run-a-baremetal-ps-application-with-cortex-a72-using-vitis-ide-on-vck190?language=ja

[3]HDMI 1.4/2.0 Transmitter Subsystem Product Guide

https://japan.xilinx.com/content/dam/xilinx/support/documentation/ip_documentation/v_hdmi_tx_ss/v3_2/pg235-v-hdmi-tx-ss.pdf

[4]Xilinx Wiki:BEAM Tool for VCK190 Evaluation Kit

https://xilinx-wiki.atlassian.net/wiki/spaces/A/pages/973078551/BEAM+Tool+for+VCK190+Evaluation+Kit