【Versal™ACAP】機能紹介 NoC編(2)

みなさんこんにちは。

前回 はVersal™ACAPの機能であるNoC(Network on Chip)の概要について説明しました。

今回はVivado® ML Edition上でNoCのシミュレーションを行う準備の様子をお伝えします。

まだ前回をご覧になられていない方は、是非 前回の記事を参考にNoCの特徴や導入のメリットを知っていただければと思います。

ご不明点などございましたら、本ページ下部からお気軽に問い合わせいただければと思います。

それでは、始めましょう。

このブログは「FPGA設計ブログ一覧」の

Versal Acap関連のひとつです。

目次

Simulation用デザインの作成

今回は、以下の環境で実行します。

- CentOS 7.6

- Vivado® ML Edition 2020.2

Vivado起動後、Block Designを作成します。

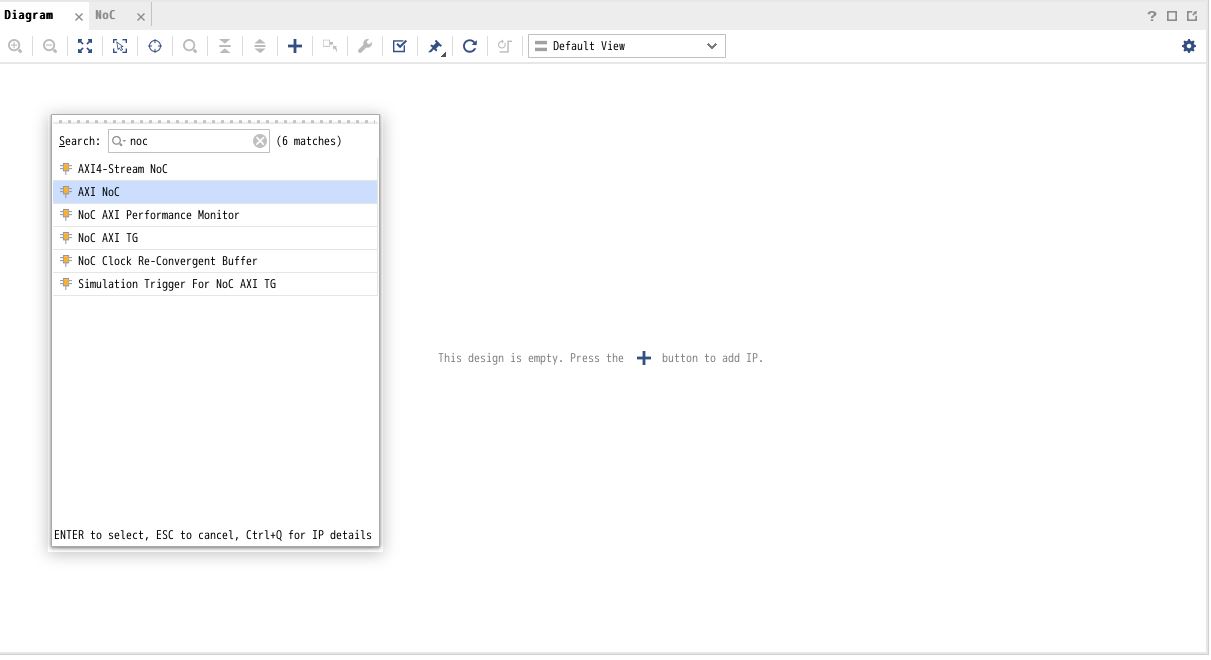

IPよりNoCを選択します。

出典:Vivado® ML Edition

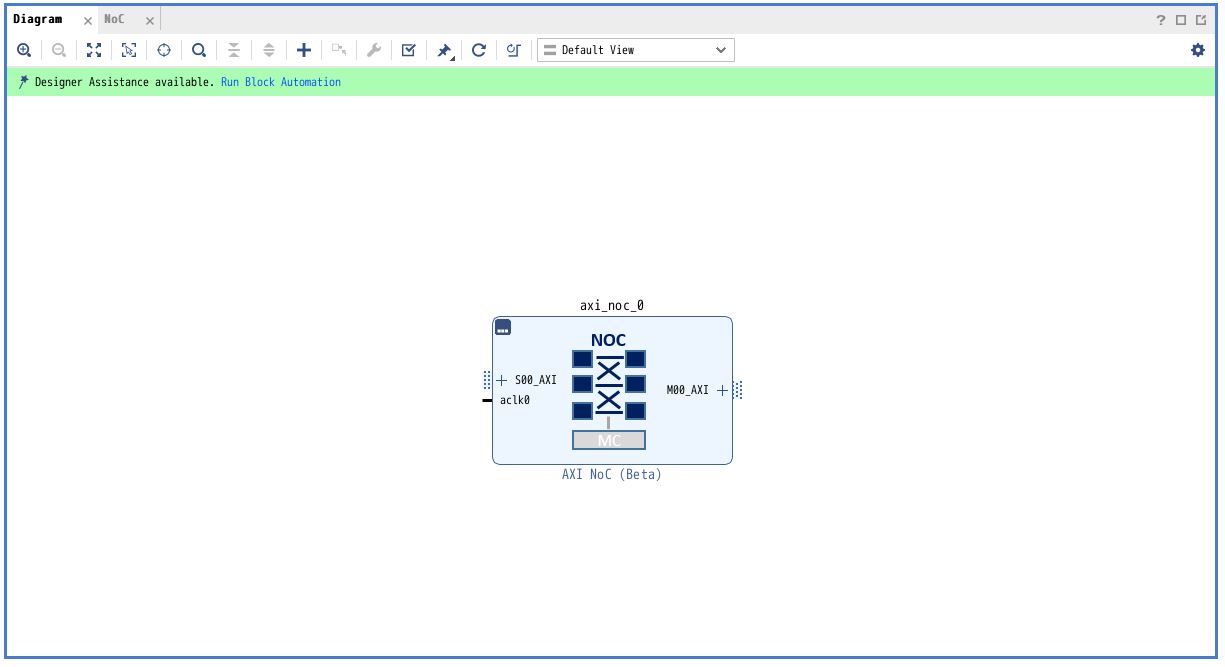

NoC配置後、「Run Block Automation」を選択します。

出典:Vivado® ML Edition

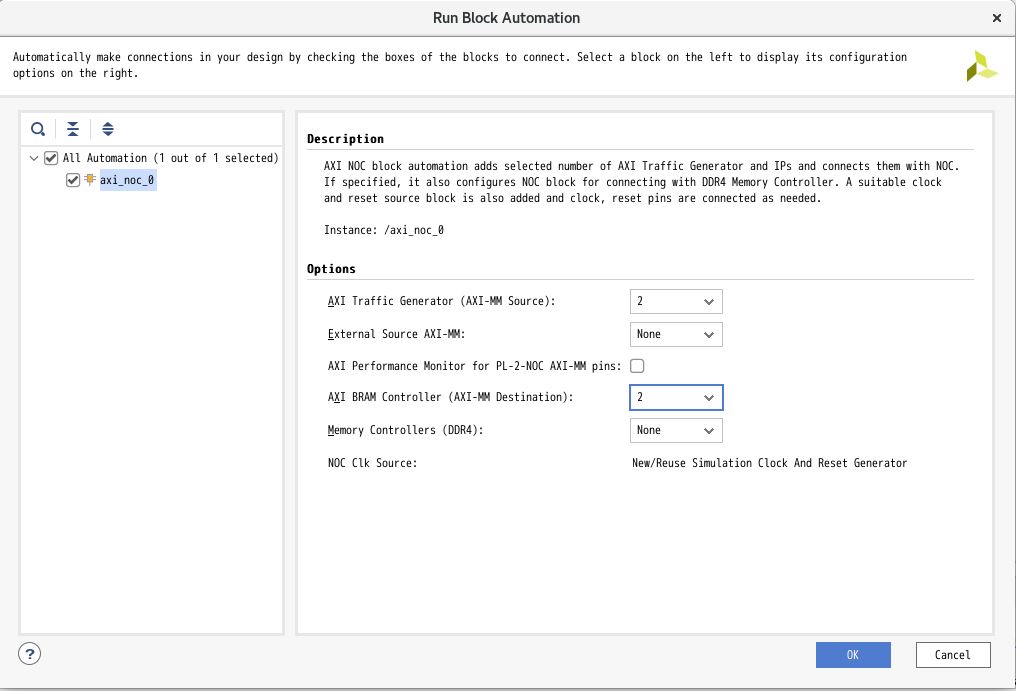

以下のような設定画面が開きます。

今回は下図の設定で進めます。

出典:Vivado® ML Edition

~設定項目について~

| AXI Traffic Generator (AXI-MM Source) |

テスト用のTraffic Generatorを追加できます。今回はSimulation用に2つ追加します。 |

|---|---|

| External Source AXI-MM | NoCに接続する別のソースがある場合は、こちらで追加を行います。もちろん、設定完了後の追加も可能です。 |

| AXI Performance Monitor for PL-2-NOC AXI-MM pins | AXIのTraffic Generatorに対して、パフォーマンスモニターを配置する場合はチェックを入れます。パフォーマンスモニターを加えると、Simulationの画面で帯域などを確認することができます。 |

| AXI BRAM Controller (AXI-MM Destination) |

使用するBRAMの数を選択します。今回は、2つのTraffic Generatorに対してBRAMをそれぞれ配置するため、2を選択します。 |

| Memory Controllers (DDR4) | DDR4を使用する際は、インターフェースの数を選択します。今回は、Simulationを目的とするため、Noneを選択します。 |

| NOC Clk Source | NoCのクロックソースが表示されます。 |

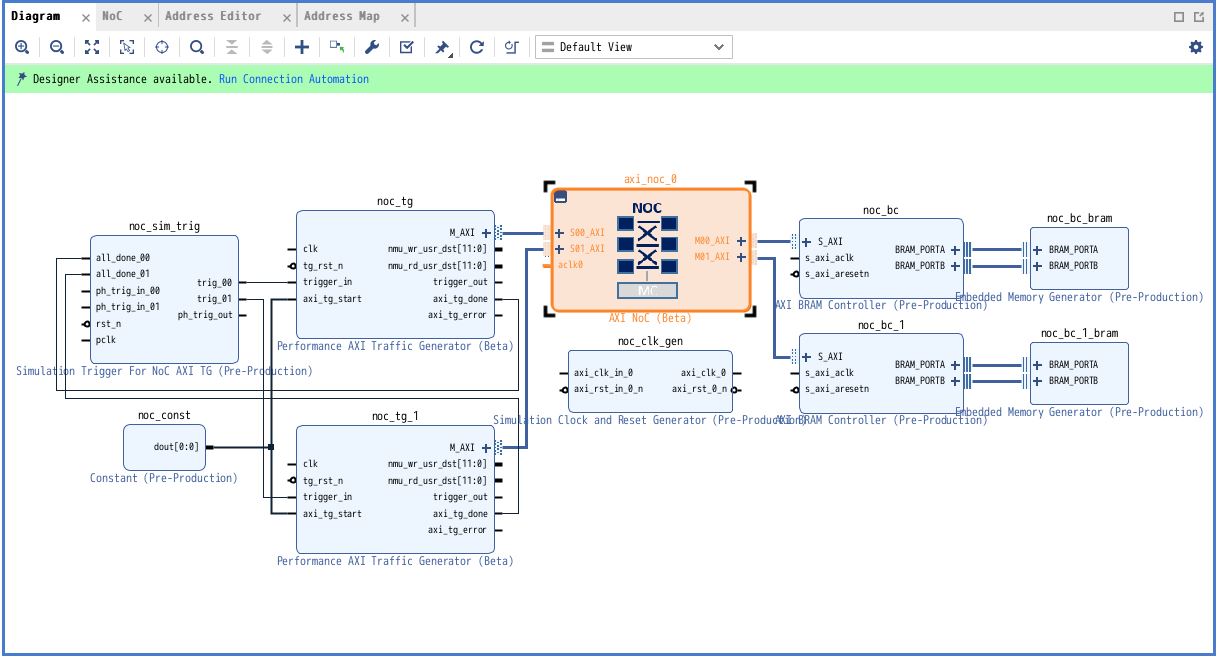

設定反映後、「Regenerate Layout」を行うと以下のような画面となります。

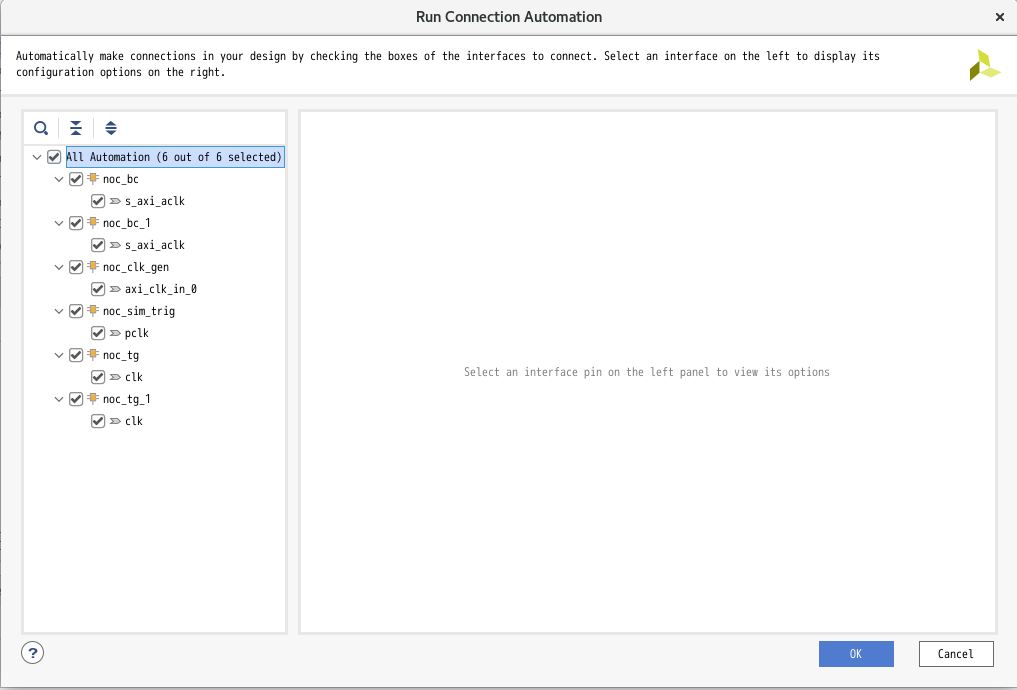

さらに緑色のバーより「Run Connection Automation」を選択します。

出典:Vivado® ML Edition

「Run Connection Automation」の設定画面です。各IPのクロックソースを選択します。

今回は、「ALL Automation」を選択し、自動配線を行います。

出典:Vivado® ML Edition

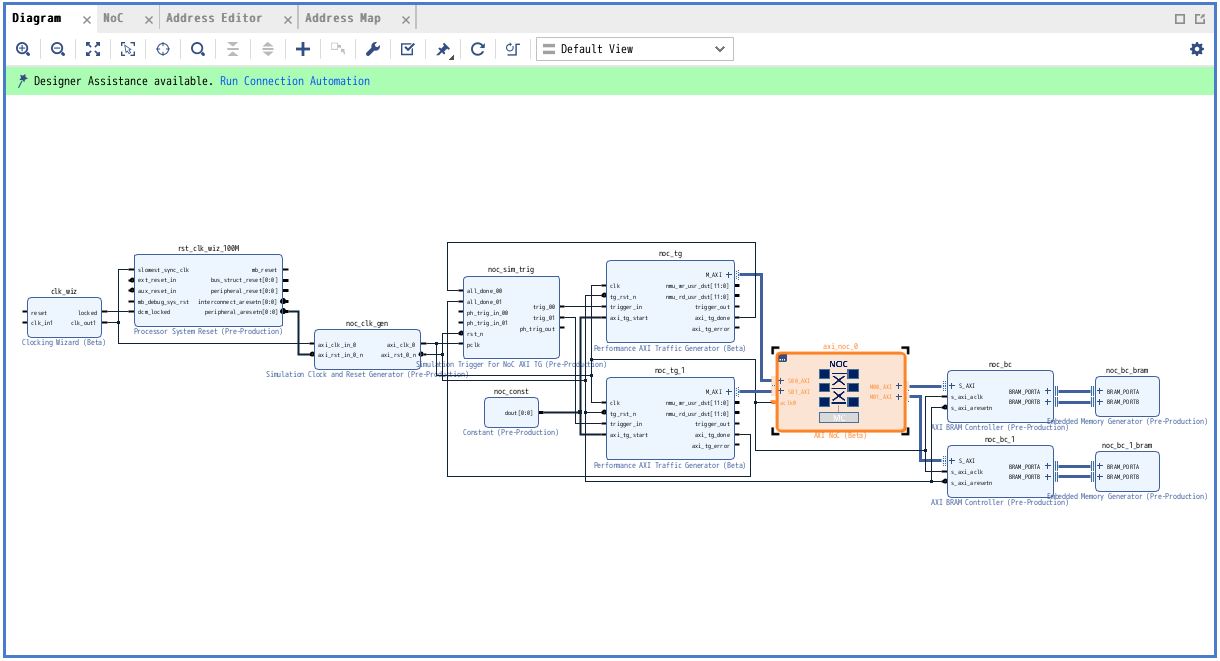

以下の画面となります。

さらに緑色のバーから「Run Connection Automation」をもう一度選択します。

出典:Vivado® ML Edition

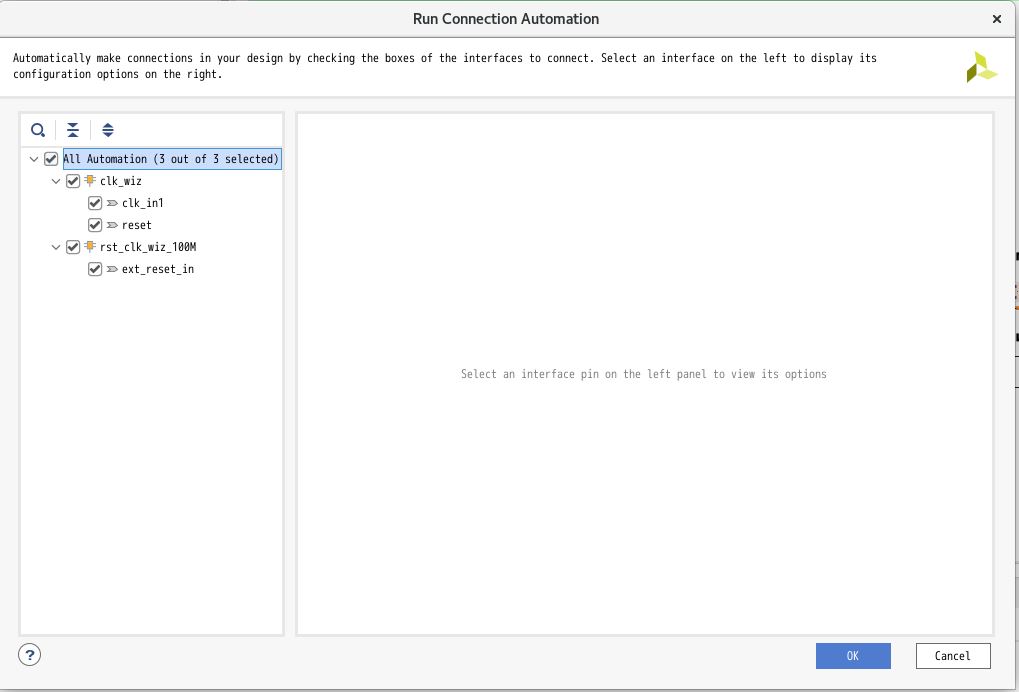

外部インターフェースのクロック系とリセット系の設定を行います。

こちらも今回は、「ALL Automation」を選択し、自動配線を行います。

出典:Vivado® ML Edition

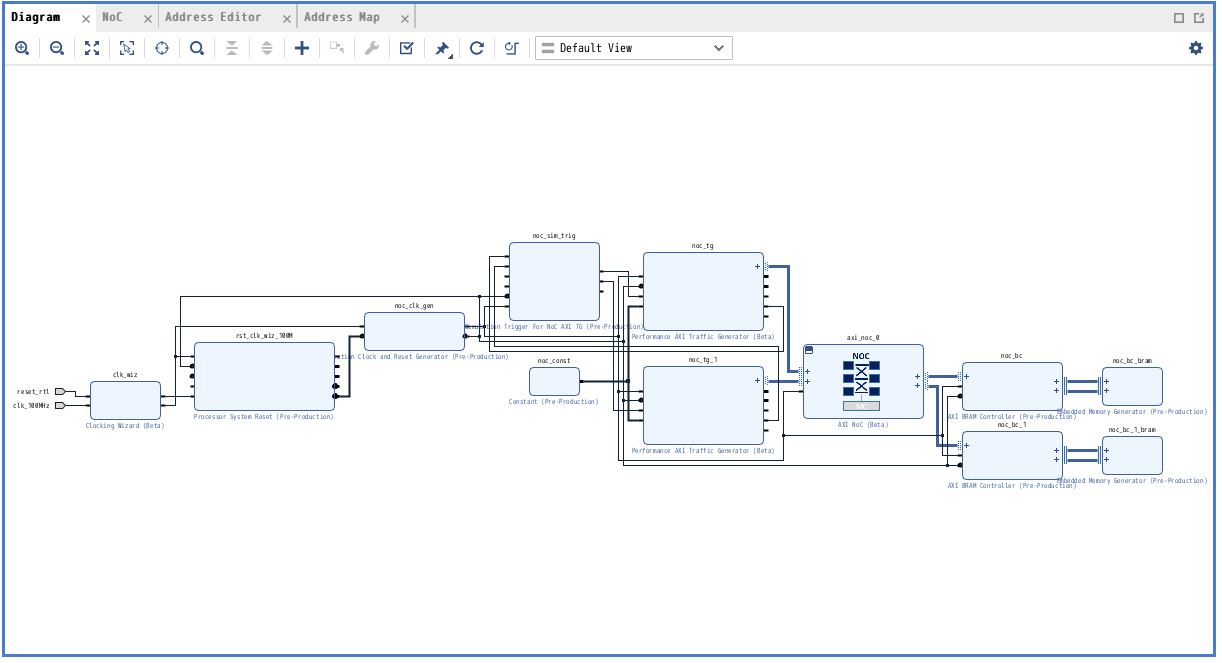

これにて、NoCのSimulation用のIP配置と各IP間の接続は終了となります。

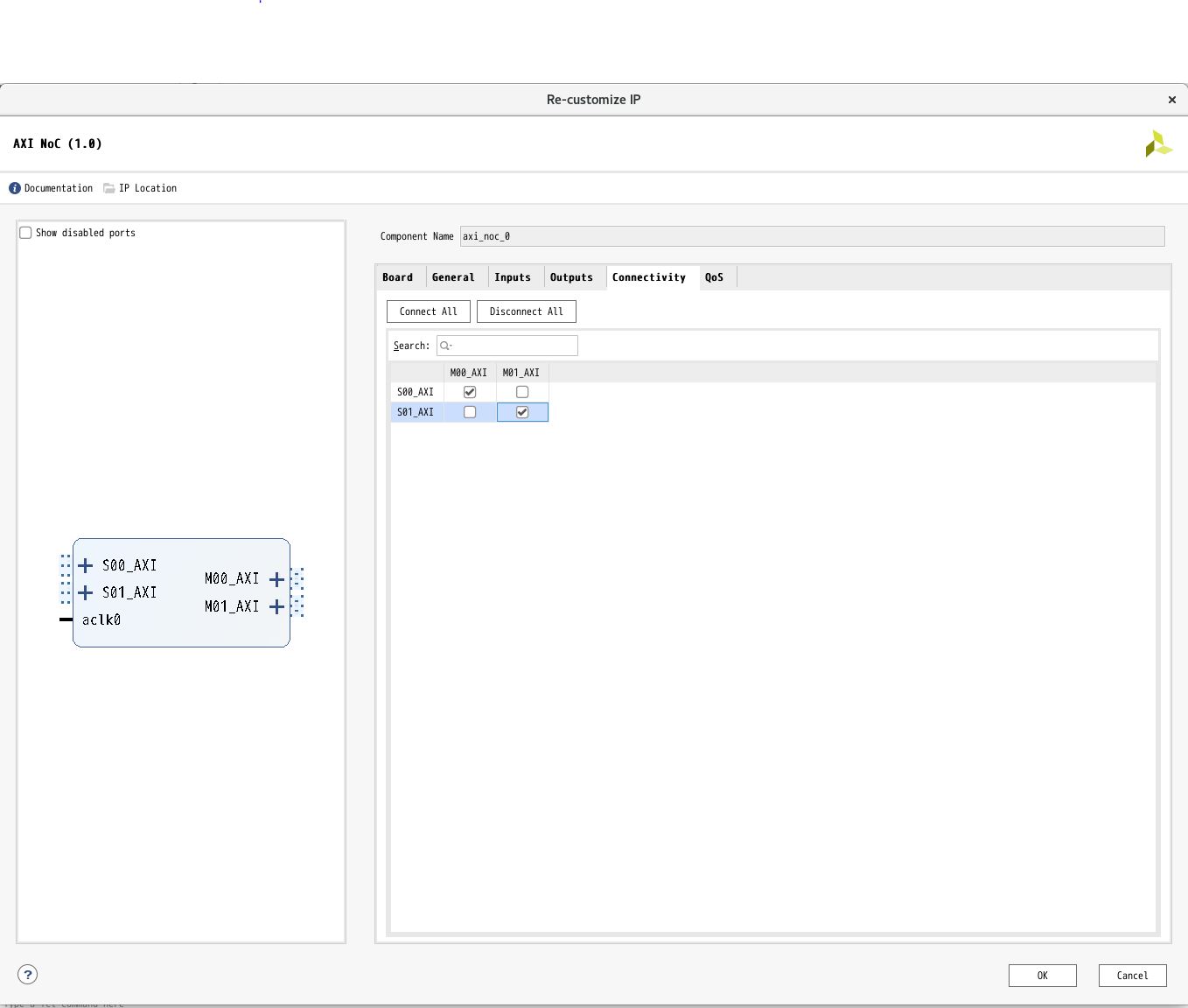

次に、「axi_noc_0」をダブルクリックし、NoCの設定画面を開きます。

出典:Vivado® ML Edition

以下のような画面が表示されます。

「Connectivity」のタブを選択し、S00_AXI⇔M00_AXI, S01_AXI⇔M01_AXIが接続されていることを確認します。

出典:Vivado® ML Edition

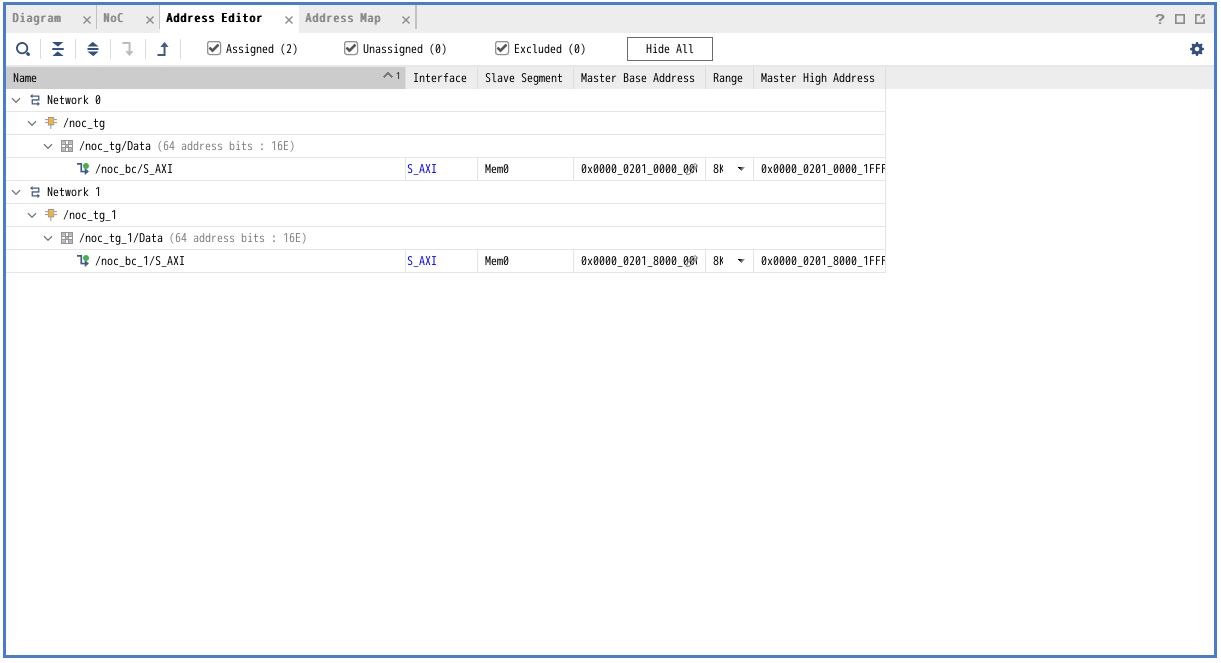

Block Designの「Address Editor」タブにてAddress Assignを選択します。

出典:Vivado® ML Edition

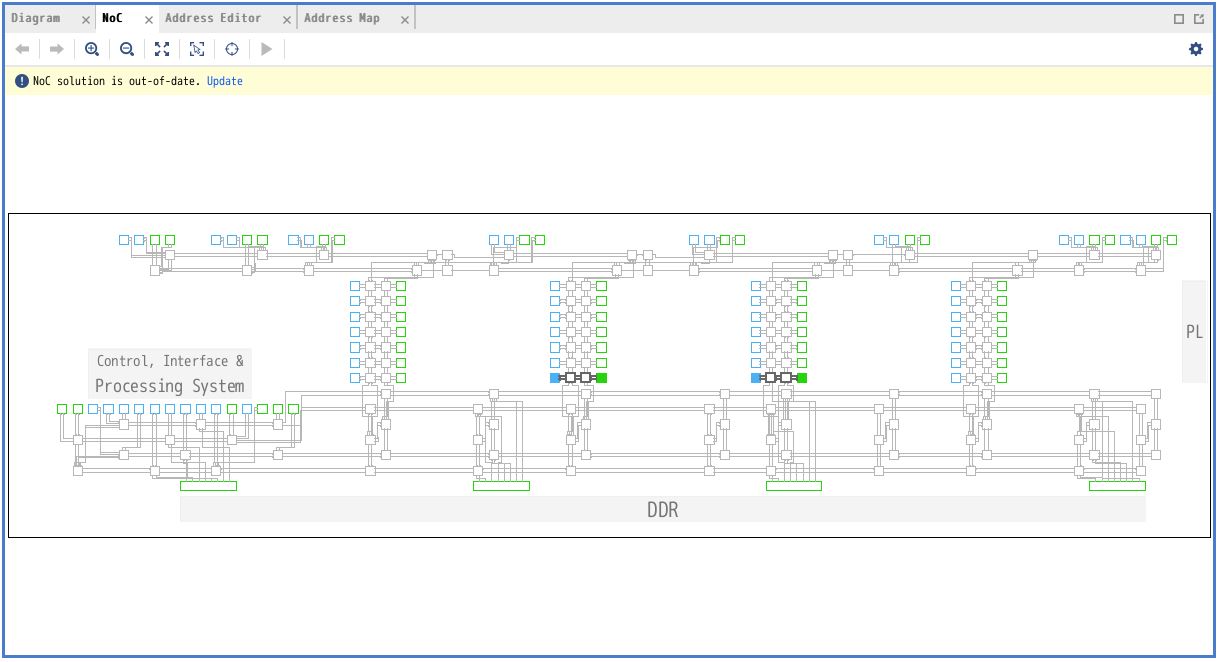

最後に「Validate Design」を実行して接続に問題がないことを確認します。

出典:Vivado® ML Edition

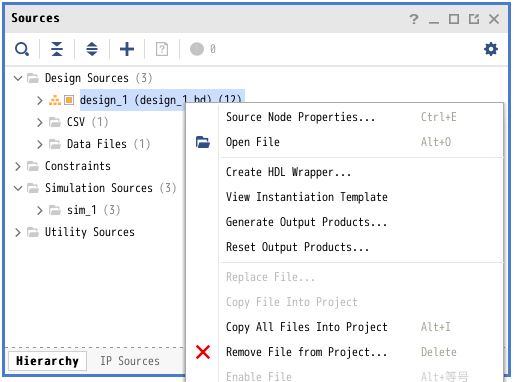

Block Designを閉じ、「Create HDL Wrapper」を実行してSimulationの準備を完了します。

出典:Vivado® ML Edition

以上でNoCを用いたデザインの作成は終了となります。

Simulation実行および帯域などの性能面については次回とさせていただきます。

終わりに

今回は、NoC (Network on Chip)を使用したSimulation用デザインの作成の様子をご覧いただきました。次回以降では、Simulationを通じてNoCのパフォーマンスを紹介できればと思います。

これからもTECHブログを通じて、わかりやすくお伝えできればと思います。

次回のブログもどうぞよろしくお願いいたします。

調査依頼や、設計検討などありましたら、弊社デザインサービス事業までお気軽にお問い合わせください。

このブログは「FPGA設計ブログ一覧」の

Versal Acap関連のひとつです。

最後までお付き合いいただきありがとうございました。