【Vivado® ML Edition 2021.1】を使ってVCK190 評価キットのプロジェクトを作成してみた

VCK190 評価キットのシリーズの第1弾はこちら

【Versal ACAP】 Versal™ AI コア シリーズ VCK190 評価キットを動かしてみた【紹介動画付き】

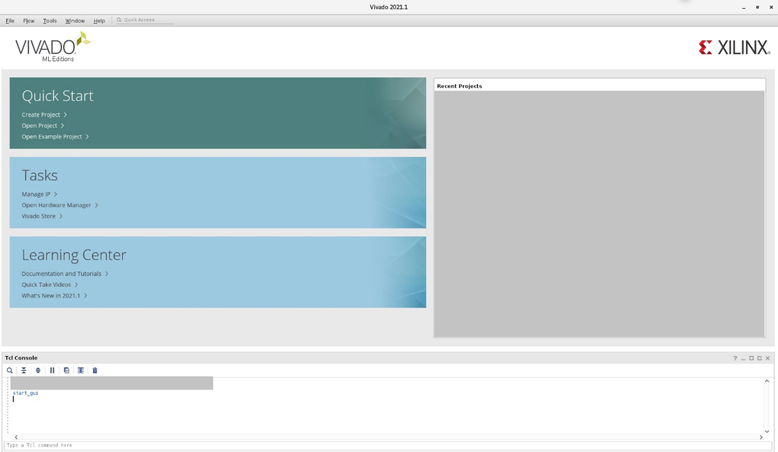

2021年6月末にXilinx社のツールであるVivado® Design Suiteの最新版として「Vivado® ML Edition 2021.1」がリリースされました。

ブロックデザインの中にブロックデザインを配置できるほか、CIPSのUIが変更など、多くの新機能や拡張機能があるようです。

Vivado® ML Editionの新機能はこちらからご確認ください

https://japan.xilinx.com/products/design-tools/vivado/vivado-whats-new.html

今回は、ツールインストールした後、Versal™ AI コア シリーズ VCK190 評価キットのシンプルなプロジェクトを作成し、書き込みしましたので、その内容についてお知らせします。

このブログは「FPGA設計ブログ一覧」の

Versal Acap関連のひとつです。

目次

ツールインストール

ツールインストールはCentOS PCで行います。

使用機材

| PC | OS:CentOS 7.6 | |

|---|---|---|

| 評価キット | Versal™ コア シリーズ VCK190 評価キット(EK-VCK190-G-ED) | |

| USBケーブル | USB Type-C Cable | 評価キット付属品。 WindowsPCとVCK190を接続し、TRDにアクセスします。 |

インストーラーのダウンロードはこちらから

https://japan.xilinx.com/support/download.html

統合版インストーラーは、約52GBとサイズが大きいため、ウェブインストーラーを推奨します。

インストール

早速始めてみましょう。

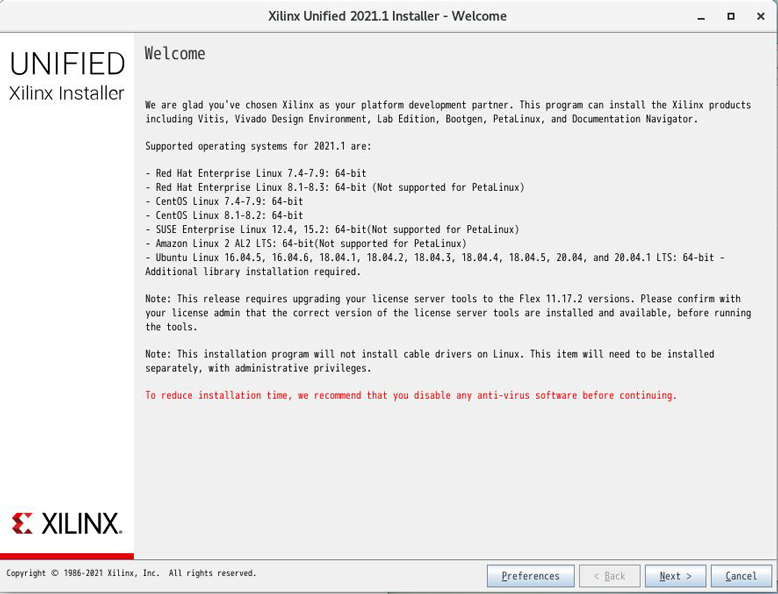

まずはWelcome画面です。

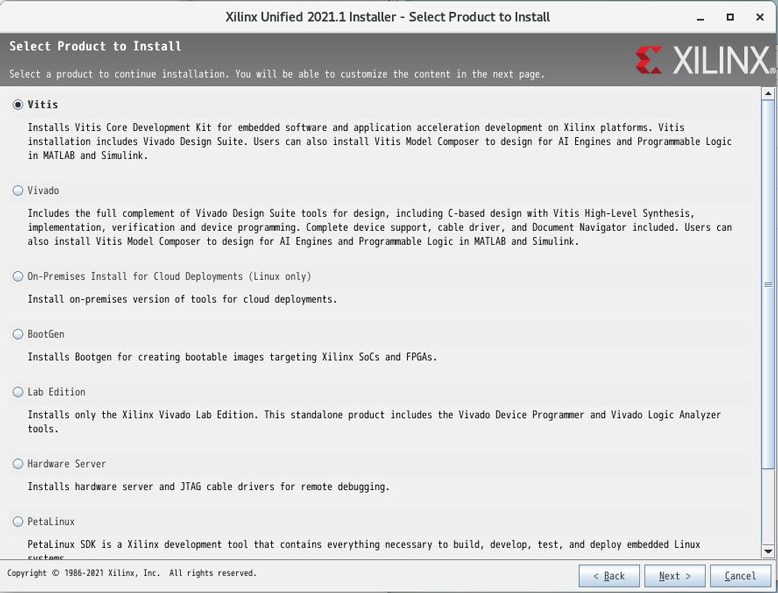

Select Product to Install 画面

Vitisを選択しました。

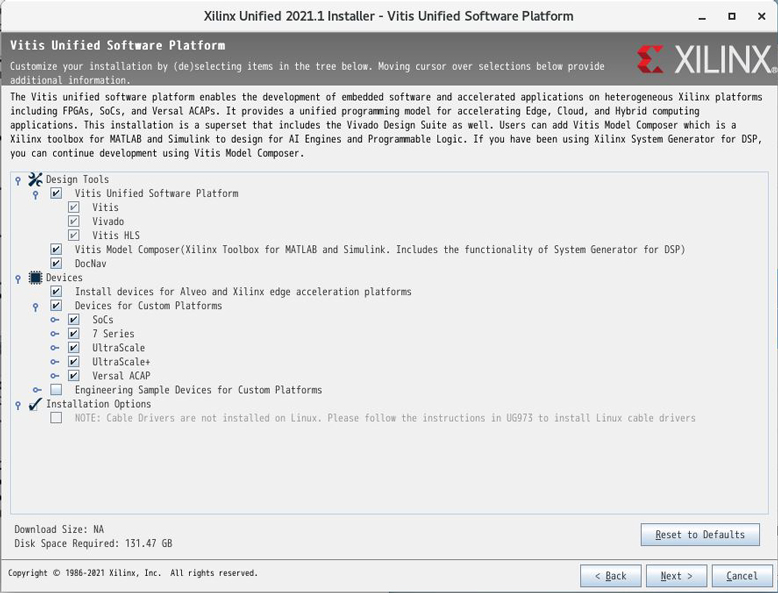

Vitis Unified Software Platform画面。

全てを選択すると必要な領域が大きくなってしまうので、必要な分だけを選択します。

※Accept License Agreements → Select Destination Directoryは割愛します。

インストールを開始して終了を待ちます。

インストールが完了し、起動して終了です。

プロジェクト作成 ~ 書き込みまで

早速プロジェクトを作成します。

こちらも作成までの画面を一部展開します。

✔ プロジェクト作成

Create ProjectからNextを選択して進めます。

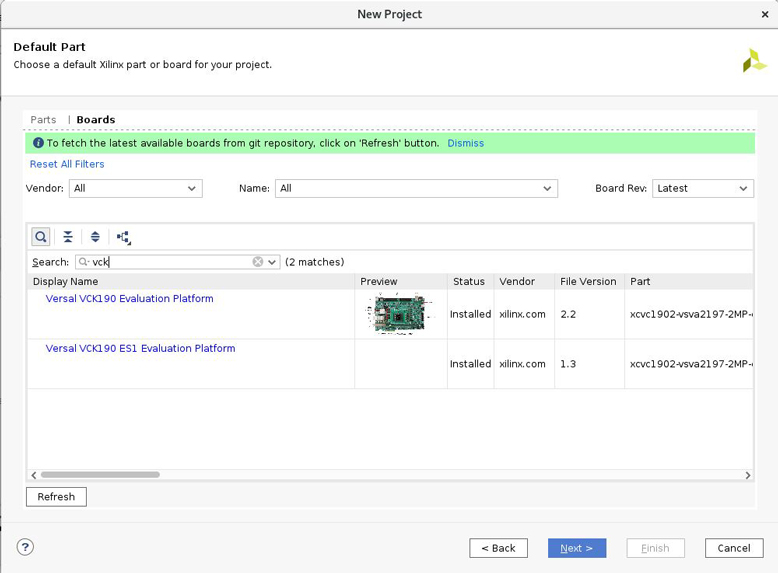

Default Part画面です。今回はVersal™ VCK190 評価キットes版を選択します。

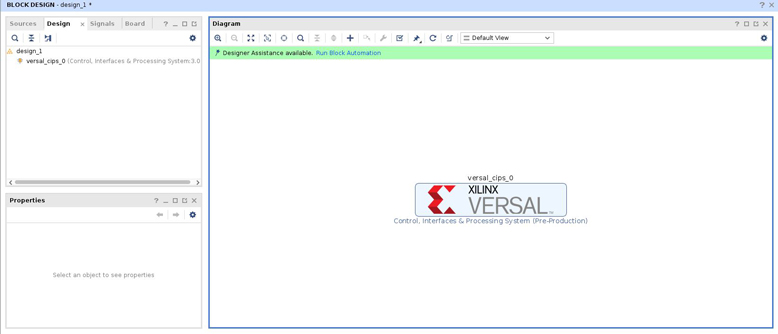

プロジェクトが作成されたら、次にブロックデザインを作成します。

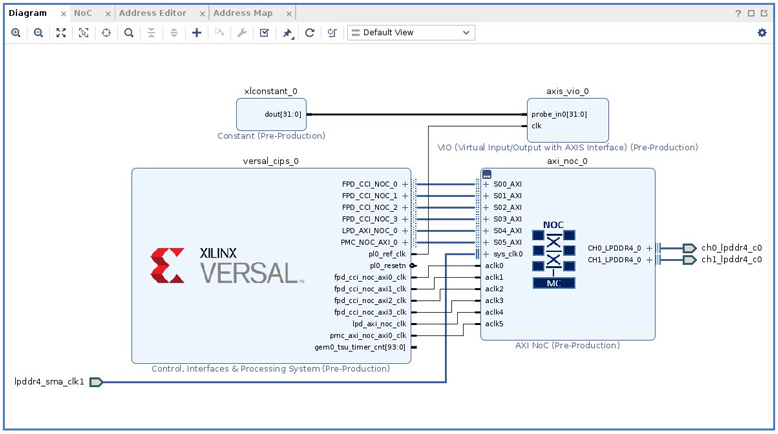

今回は、書き込みするだけなので、CIPSを置きます。

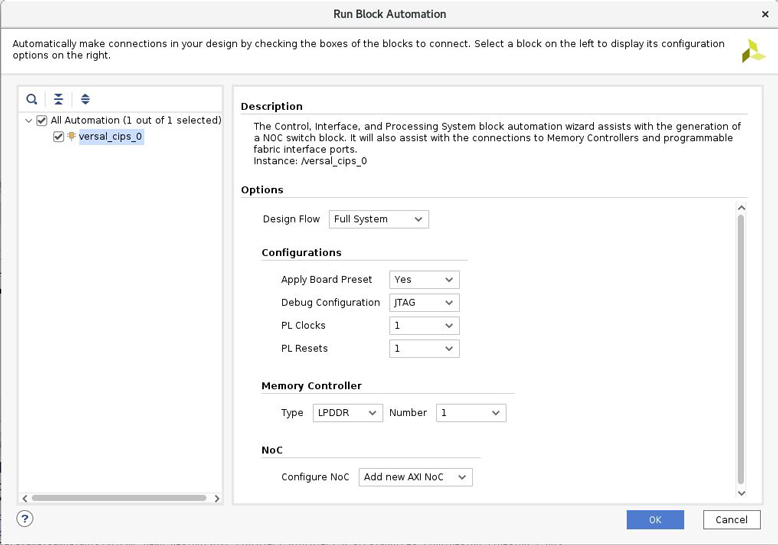

Run Block Automationを選択します。

VIOを置くのでPL Clockを1つとおまけでLPDDR4とNoCも置いてみます。

各IPが生成されました。

書き込み後に作成した日付を確認したいので、VIOとConstantも追加しました。

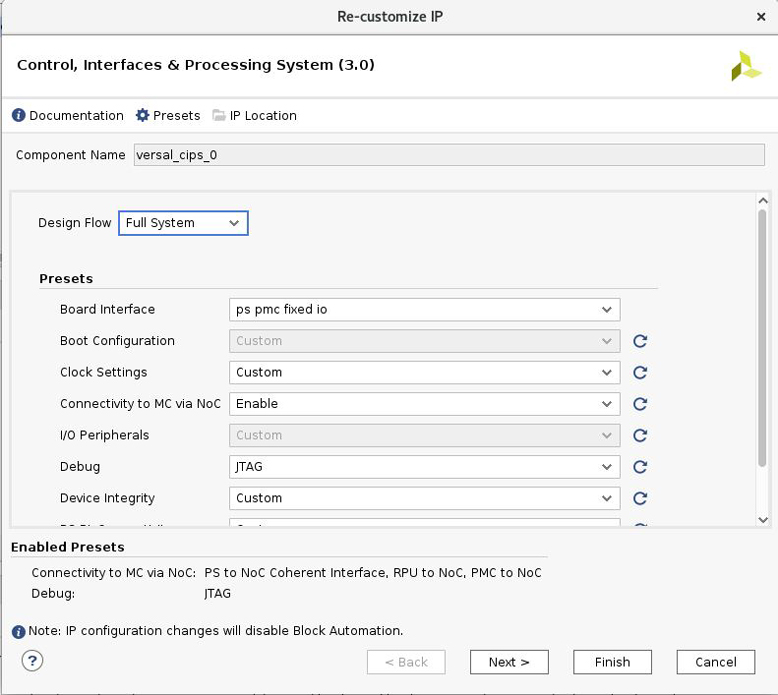

追加の設定は不要ですが、おまけでCIPSのUIです。

Vivado® Design Suite - HLx Edition 2020.xと比べてシンプルになった印象です。

Create HDL Wrapper → Generate Device Image と選択して、書き込み用のPDIファイルを作成します。

✔ 書き込み

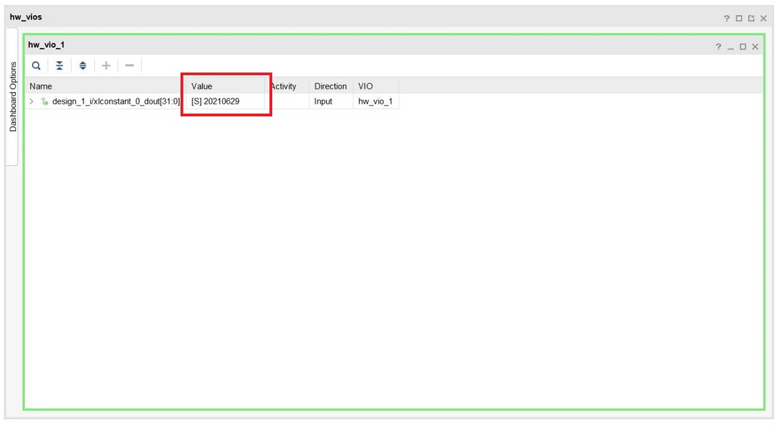

PDIファイル作成後、書き込んでVIOの値を見てみます。デザイン作成日時(2021/6/29)が表示されることが確認できました。

終わりに

今回は、「Vivado® ML Edition 2021.1」でシンプルなデザインを作成してみました。 様々な新機能が追加されているようなので、TECHブログを通じてわかりやすくお伝えできればと思います。

調査依頼や、設計検討などありましたら、弊社デザインサービス事業までお気軽にお問い合わせください。

このブログは「FPGA設計ブログ一覧」の

Versal Acap関連のひとつです。

最後までお付き合いいただきありがとうございました。