【Versal™ACAP】機能紹介 NoC Simulation編 part2

みなさんこんにちは。

前回はVivado®上にてNoCのSimulationの様子をお見せしましたが、 今回も作成したデザインについて触れていきたいと思います。

今回の内容を知らなければ、Simulation時にNoCが動かないかもしれません(筆者経験談)ので、是非ご覧ください。

以下あわせてご確認ください!!

【Versal™ ACAP】機能紹介 NoC編

https://www.paltek.co.jp/techblog/techinfo/211116_01

【Versal™ACAP】機能紹介 NoC編(2)

https://www.paltek.co.jp/techblog/techinfo/211223_01

【Versal™ACAP】機能紹介 NoC Simulation編

https://www.paltek.co.jp/techblog/techinfo/220111_01

それでは、始めましょう。

このブログは「FPGA設計ブログ一覧」の

Versal Acap関連のひとつです。

目次

今回は、以下の環境で実行します。

- CentOS 7.6

- Vivado®2020.2

自動生成されるSimulationファイルについて

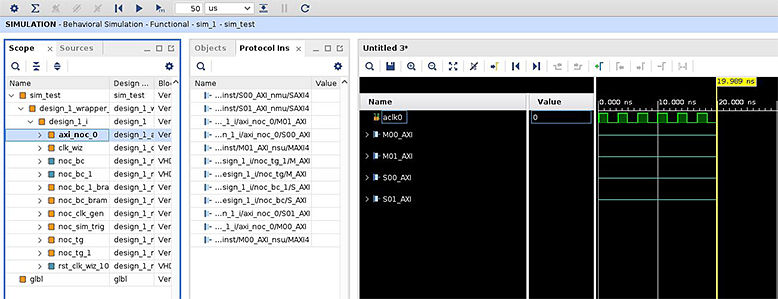

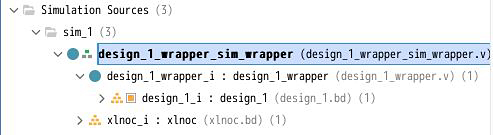

前回の記事では、「ブロックデザイン作成」⇒「ラッパーの準備」⇒「Simulation実行」 と手順を踏みましたが、「Simulation実行」の際にSimulationファイルと、もうひとつブロックデザインが自動で生成されます。

出典:Vivado® ML Edition

こちらのファイルの役割についてですが、 結論から申しますとSimulation時のNoCの動作を行っています。

sim_wrapperについて

自動生成されたdesign_1_wrapper_sim_wrapperを開いてみましょう。

出典:Vivado® ML Edition

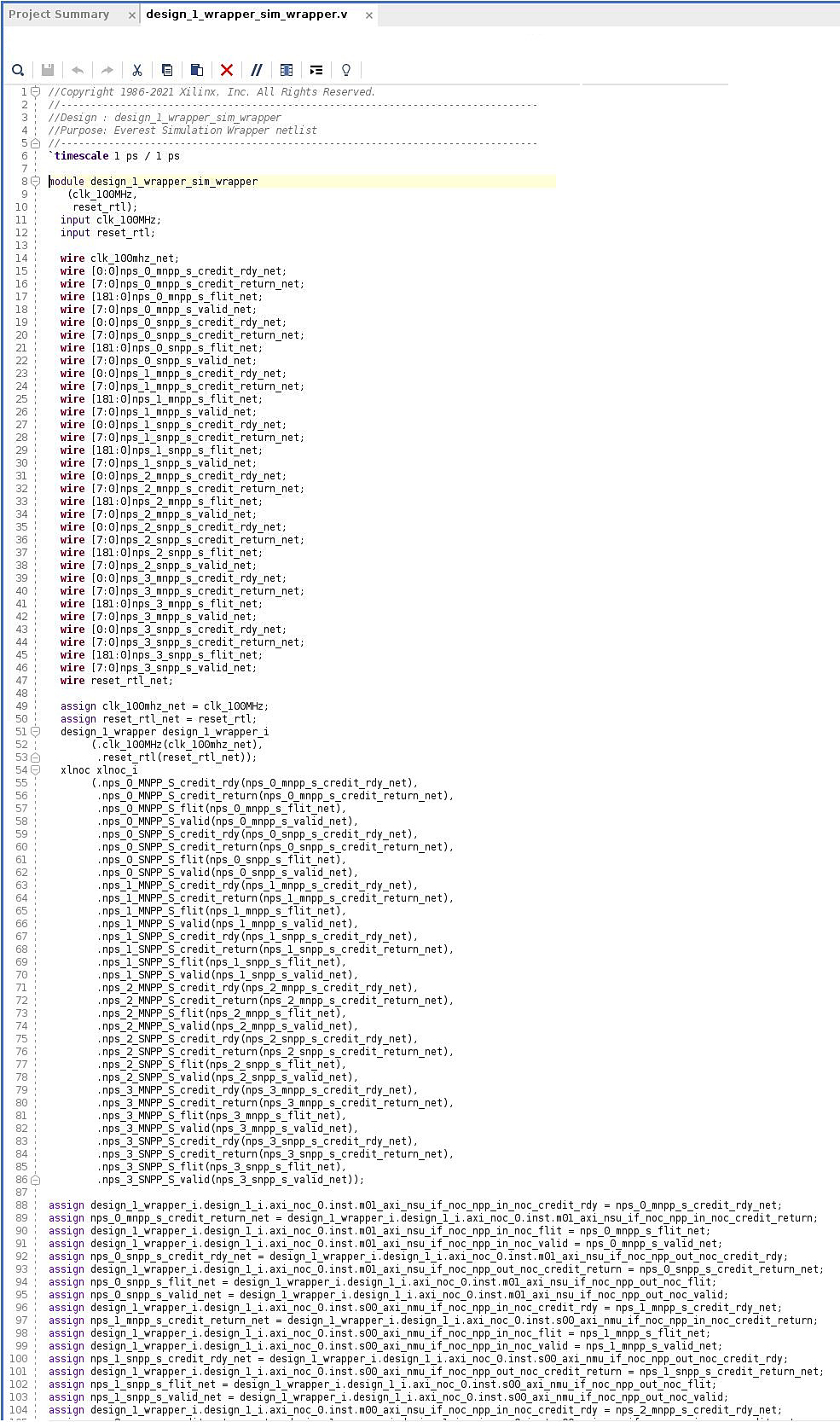

ソースあくまで一部ではありますが、

sim_wrapper内で、design_1_wrapperとxlnoc.bdを呼び出して信号接続をしています。

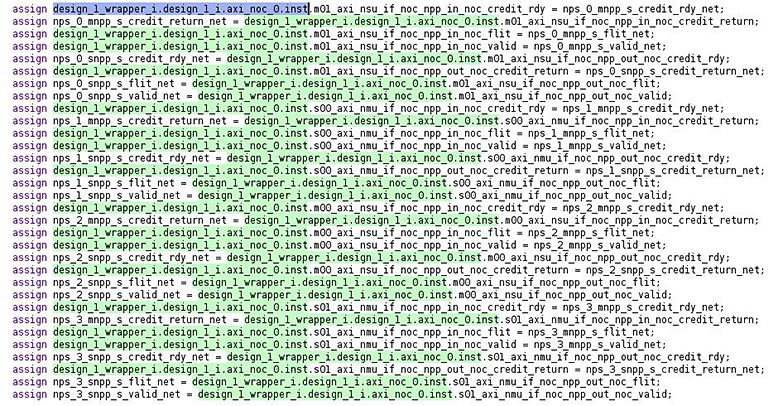

assign分に注目してみると

出典:Vivado® ML Edition

Design_1のNoCのマスター側とスレーブ側、それぞれをxlnocに接続していることがわかります。

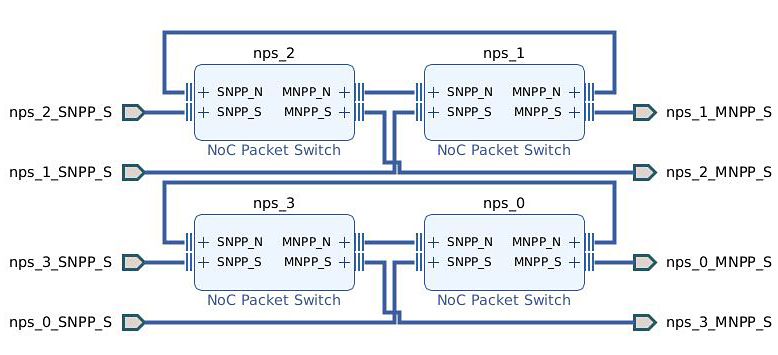

xlnoc.bdとNoC Packet Switchについて

次にxlnoc.bdを見てみましょう。

出典:Vivado® ML Edition

入力信号と出力信号が、「NoC Packet Switch」に接続されていることがわかります。

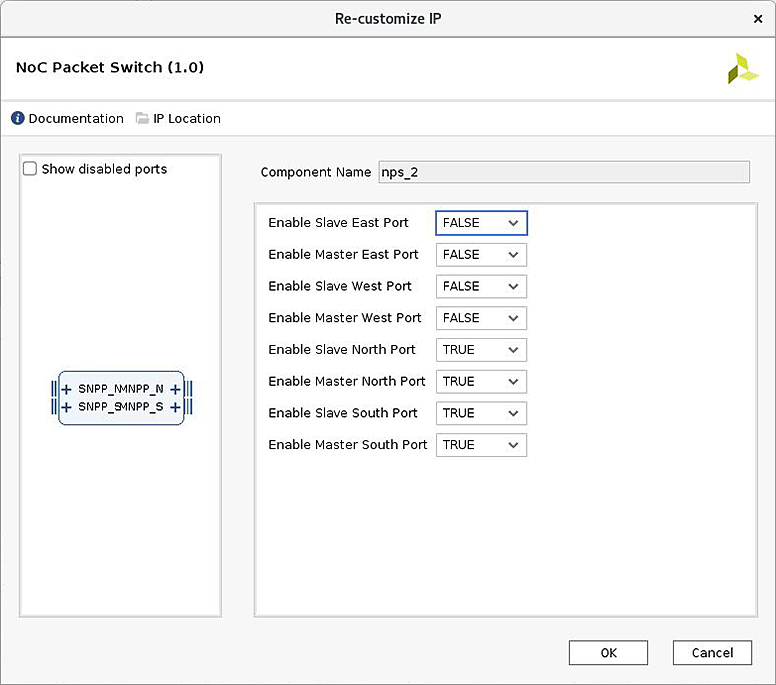

出典:Vivado® ML Edition

IPを開いた画面ですが、詳細まではわかりません。

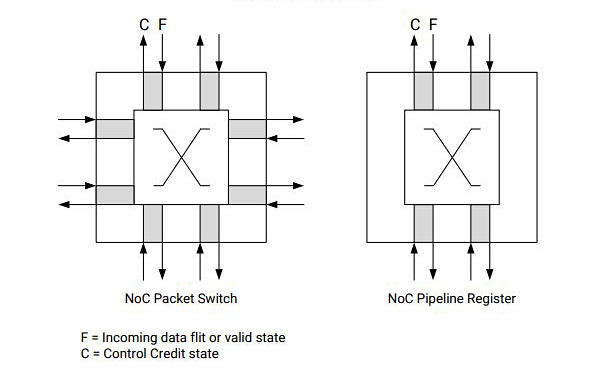

ですが、pg313-network-on-chip[1]を見てみると以下のような図があります。

NoC バケット スイッチ

出典:Versal ACAP Programmable Network on Chip and Integrated Memory Controller

https://japan.xilinx.com/content/dam/xilinx/support/documentation/ip_documentation/axi_noc/v1_0/j_pg313-network-on-chip.pdf

(参照2022-02-24)

Xlnoc.bdのIPの名前「NoC Packet Switch」と一致しています。

Sim_wrapperのassign文と合わせて見てみるとNoCの役割に相当していることが推測できます。

Sim_wrapperでのassign文は、NoCのマスター側、スレーブ側に繋がるそれぞれのIPをこちらに繋げているようです。

sim_wrapperとxlnoc.bdを除いた場合

話は変わりますが、FPGAデザイン設計時にSimulationを実行する際には、テストベンチを用意している方も多いかと思われます。

テストベンチを作る際に基本的に用意するのは、FPGA外のインターフェースの信号となります。

クロック、リセット、データ信号、etc…

IPの中身を用意するということは考慮しにくいかもしれません。

では、今回のこちらのsim_wrapperのassign文、xlnoc.bdがない場合、どうなるかを確認してみましょう。

※画像クリックで大きな画像が表示されます。

出典:Vivado® ML Edition

即興ですがsim_wrapperからxlnoc.bdとassign文を除いたSimulation用ファイルを用意しました。

Simulation用のクロック、リセットIPが用意されているため、クロックは動作していますが、NoCのマスター側、スレーブ側共に全く動かなくなりました。

やはりxlnoc.bdを用意しないとNoCのSimulationはできないようです。

また、NoCの設定を変えた際は、sim_wrapper、xlnoc.bd共に自動で再生成されます。

余談ですが、筆者はテストベンチを自分で用意した結果、NoCをSimulationできず苦労しました。

NoCを使用したデザインでSimulationを実行する際は、気を付けなければいけません。

おわりに

今回は、Simulation実行時に生成されるsim_wrapperとxlnoc.bdについて説明させていただきました。

新規デバイスに代わることで予想外のスケジュール遅延が起きないよう、TECHブログでは今回のような事例もお伝えできればと思います。

次回のブログもどうぞよろしくお願いいたします。

調査依頼や、設計検討などありましたら、弊社デザインサービス事業までお気軽にお問い合わせください。

最後までお付き合いいただきありがとうございました。

このブログは「FPGA設計ブログ一覧」の

Versal Acap関連のひとつです。