【Versal™ACAP】PCIe Link Debug②【Vivado® ML 2021.2】

みなさん、こんにちは。

今回は、前回ご紹介したPCIe Link Debugの機能について、もう少し確認してみた結果を紹介したいと思います。

今回の記事は前回記事をベースに作成していますので、よろしければ先に前回記事からご覧ください。

それでは、始めましょう。

このブログは「FPGA設計ブログ一覧」の

Versal Acap関連のひとつです。

目次

今回は、以下の環境で実行します。

- ・HostPC CentOS 7.6

- ・Vivado® ML Edition 2021.2

必要事項

前回は、IPの「Versal® ACAP Integrated Block for PCI Express®」からExample Designを生成する形で実行しました。

しかし、Example Designではいろいろなソースが生成されるため、他のソースとマージして使おうとすると、難しくなります。

IP製品ガイドを読む限りでは、Link Debugを有効にした「Versal ACAP Integrated Block for PCI Express」と

「AXI4 Debug Hub」、「Processor System Reset」、「CIPS」をつなぐことでLink Debug機能を有効[1]にできるようです。

参照: AMD Xilinx PG343 - Enabling PCIe Link Debug

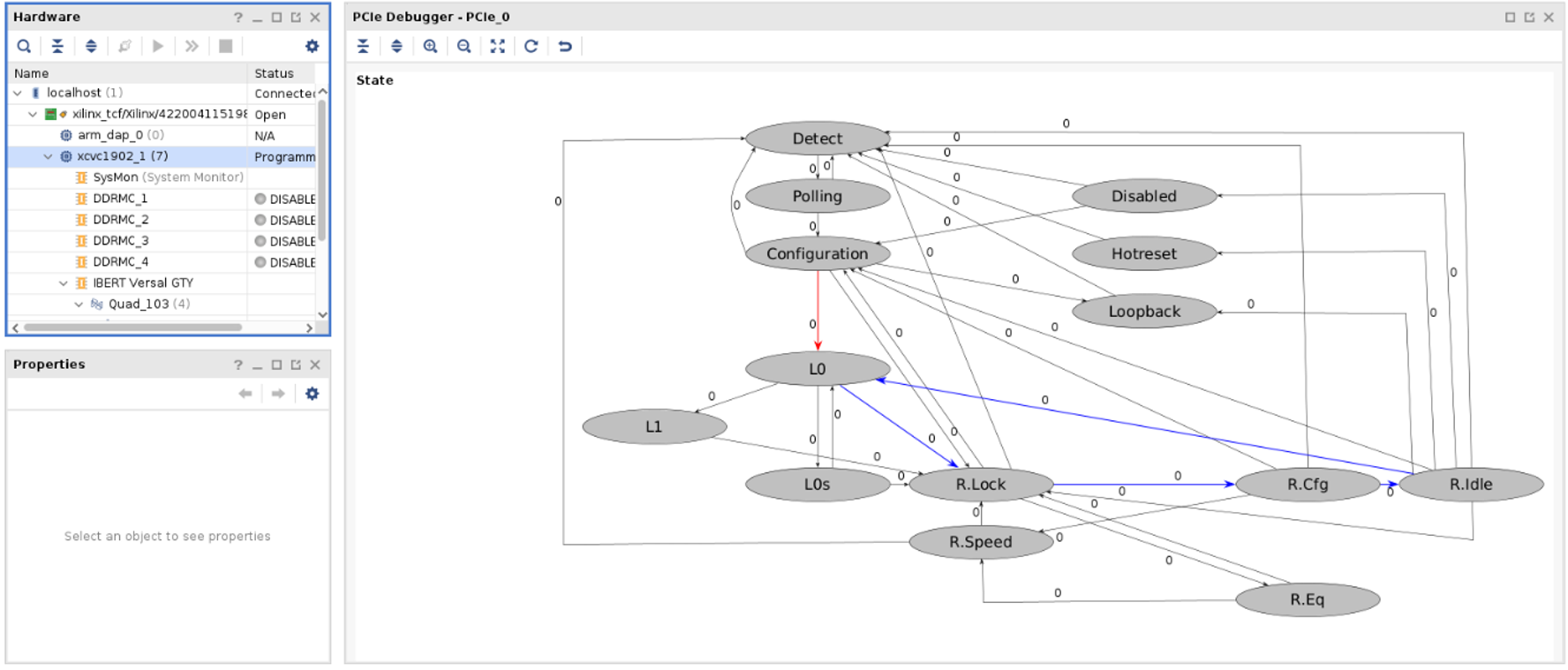

参照先のデザインを作成して確認してみましたが、以下の画面のような形でLink Debug機能の画面は開きますが、そこから先の確認はできませんでした。

出典:Vivado® ML Edition

そこで、今回はひとまず扱いやすい形にするために、Block DesignとつながるソースをIP PackageでIP化し、Example Designと同様の動作ができることを確認したいと思います。

Vivado® ML Edition

それでは、デザインを作成していきます。

まずは、前回作成したデザインを別プロジェクトで保存します。

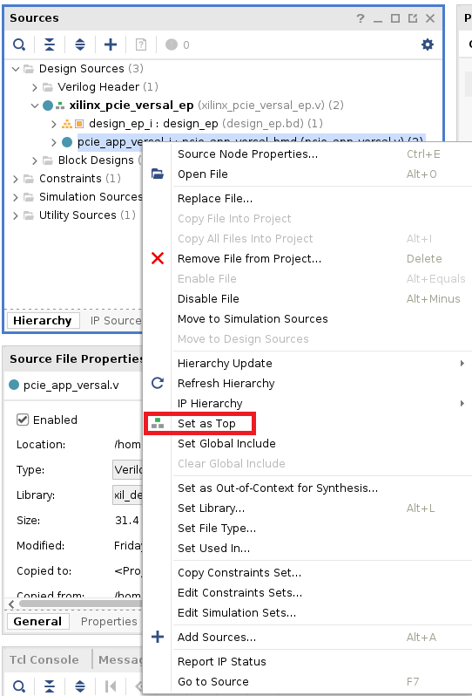

次に今回IP化をする対象になるpcie_app_versal_bmdを右クリックし、「Set as Top」でTOPソースに設定します。

出典:Vivado® ML Edition

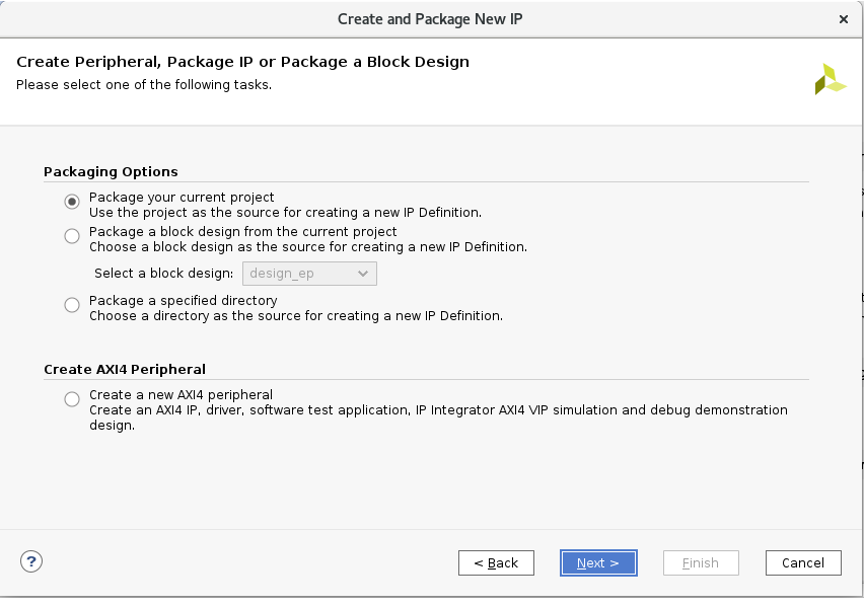

ToolsからCreate and Package New IPを選択します。

Packaging Optionsは一番上を選択します。

出典:Vivado® ML Edition

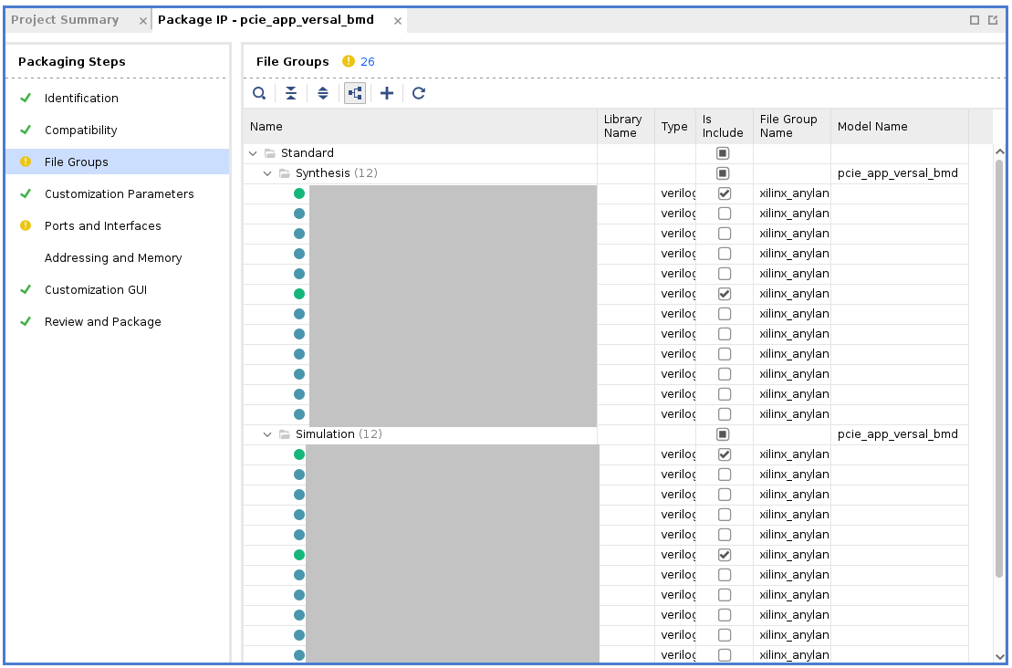

Package IPの画面が開くので、ベースプロジェクトと干渉しないように不要なファイルは削除します。

出典:Vivado® ML Edition

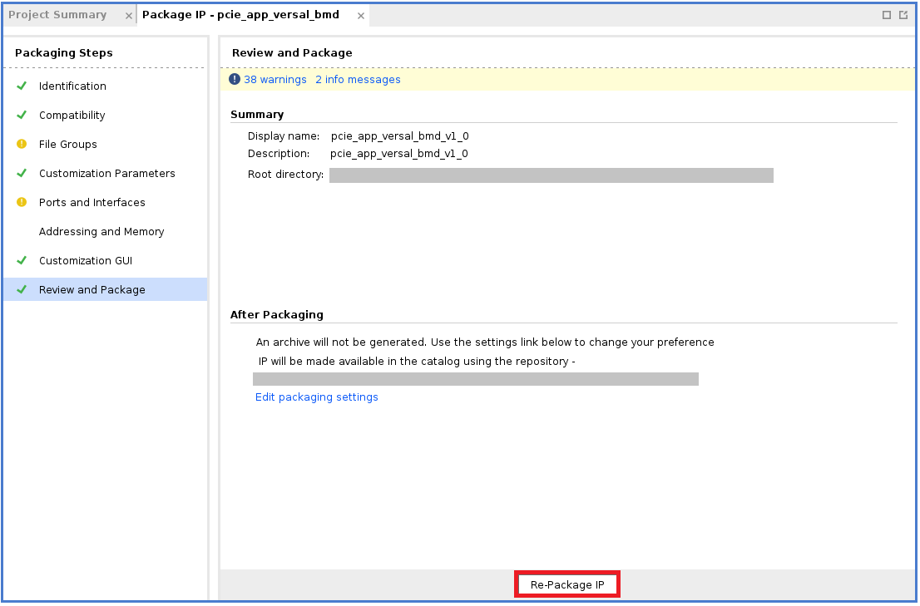

他エラーなどがなければPackage IPを実行します。

出典:Vivado® ML Edition

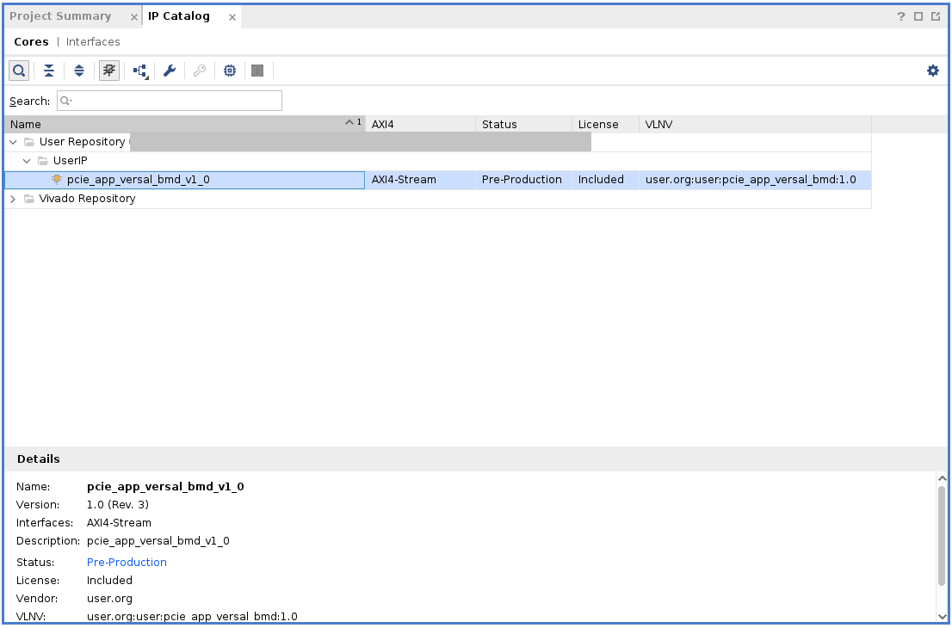

Package IPの画面は、閉じてIP Catalogに先ほど作成したIP「pcie_app_versal_bmd_v1_0」が追加されていることを確認します。

追加されていない場合は、IP Catalog上で右クリックし、Add Repositoryを実行して、生成したIPがあるフォルダを指定してください。

出典:Vivado® ML Edition

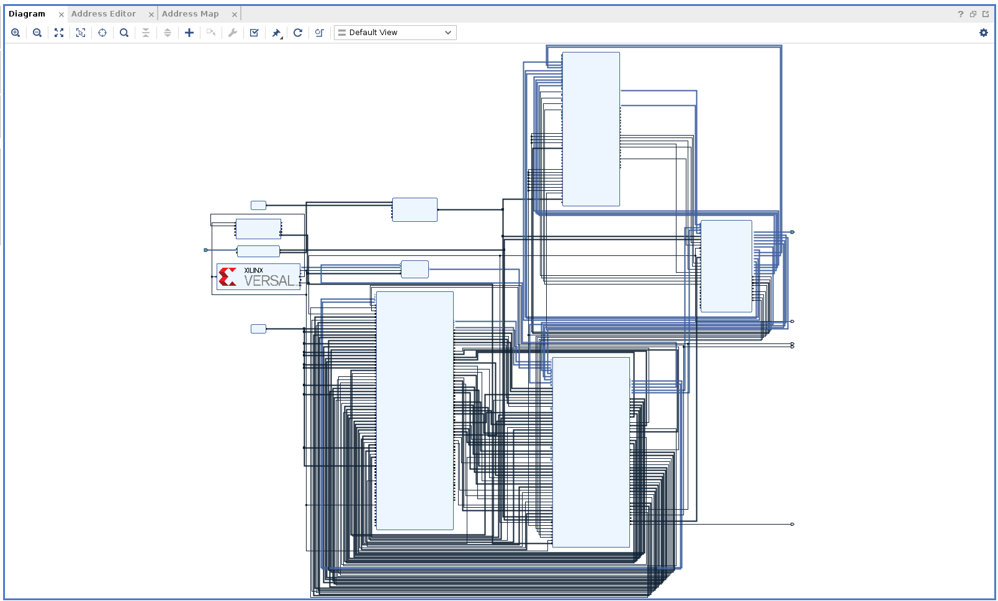

ブロックデザインを開き、先ほどのIPを呼び出します。

ベースのExample Designにならって、「Versal® ACAP Integrated Block for PCI Express®」と接続をすると、下図のような繫ぎになります。

今回は、1ピンずつ繋いだため、拡大しないと見えないくらいの規模になっています。

出典:Vivado® ML Edition

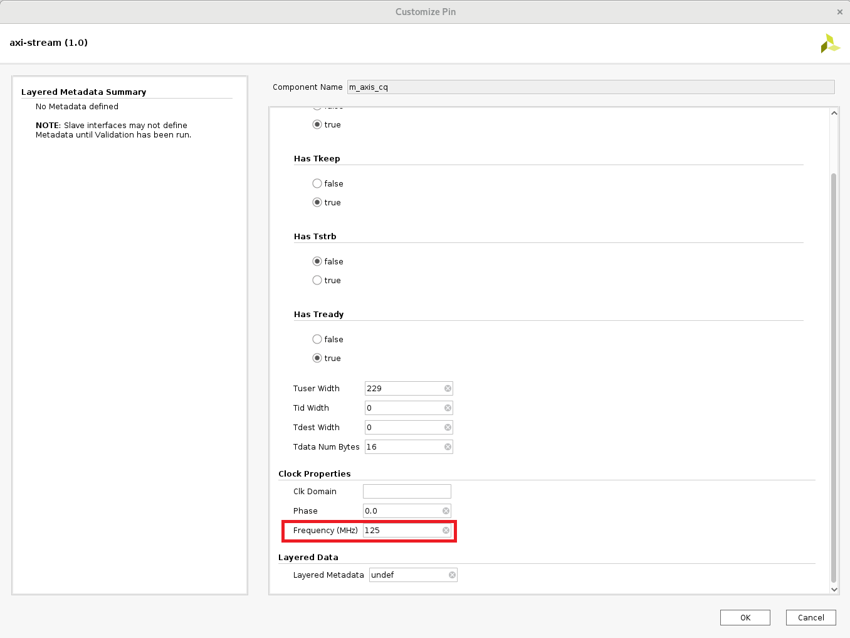

繋ぎ終えたら、Validate Designを実行します。

IP生成時の初期設定では、4つのaxisのポートの周波数が100MHzになっているので、125MHzに変えていないとここでエラーが出ます。

出典:Vivado® ML Edition

最後に、TOPソースコードからpcie_app_versal_bmdに関する記述を削除、またはコメントアウトします。

問題がなさそうであれば、Implementして、エラーが出ないことを確認します。

Generate Device Imageを実行して準備完了です。

実行

PDIファイルが作成できましたら、次はVCK190に書き込みを行います。

今回も前回同様、VCK190側がEnd、RootとしてZCU102を使います。

VCK190とZCU102を接続後、VivadoでOpen Hardware Managerを実行し、PDIファイルとLTXファイルを選択して書き込みを実行します。

ZCU102側は電源をOFFにしています。

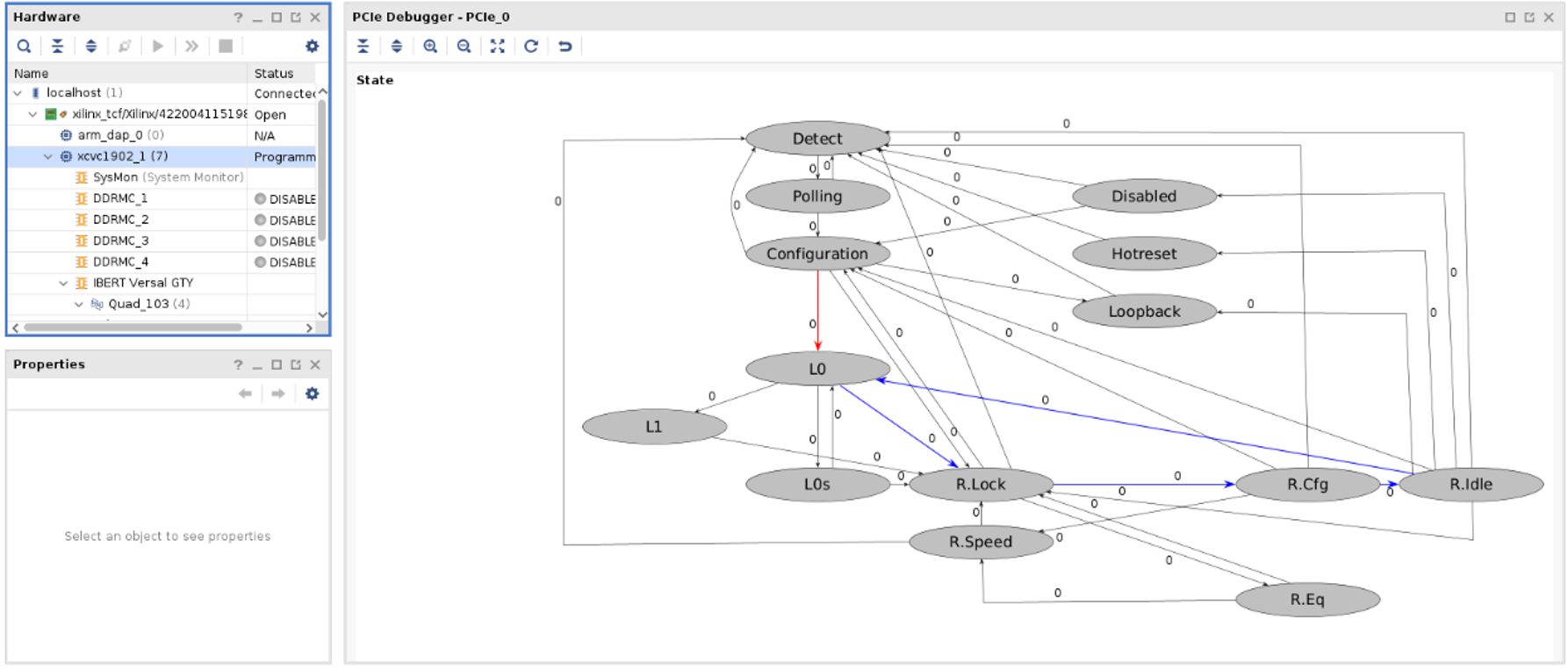

書き込み後、Vivado上でPCIe Debuggerが見えます。

出典:Vivado® ML Edition

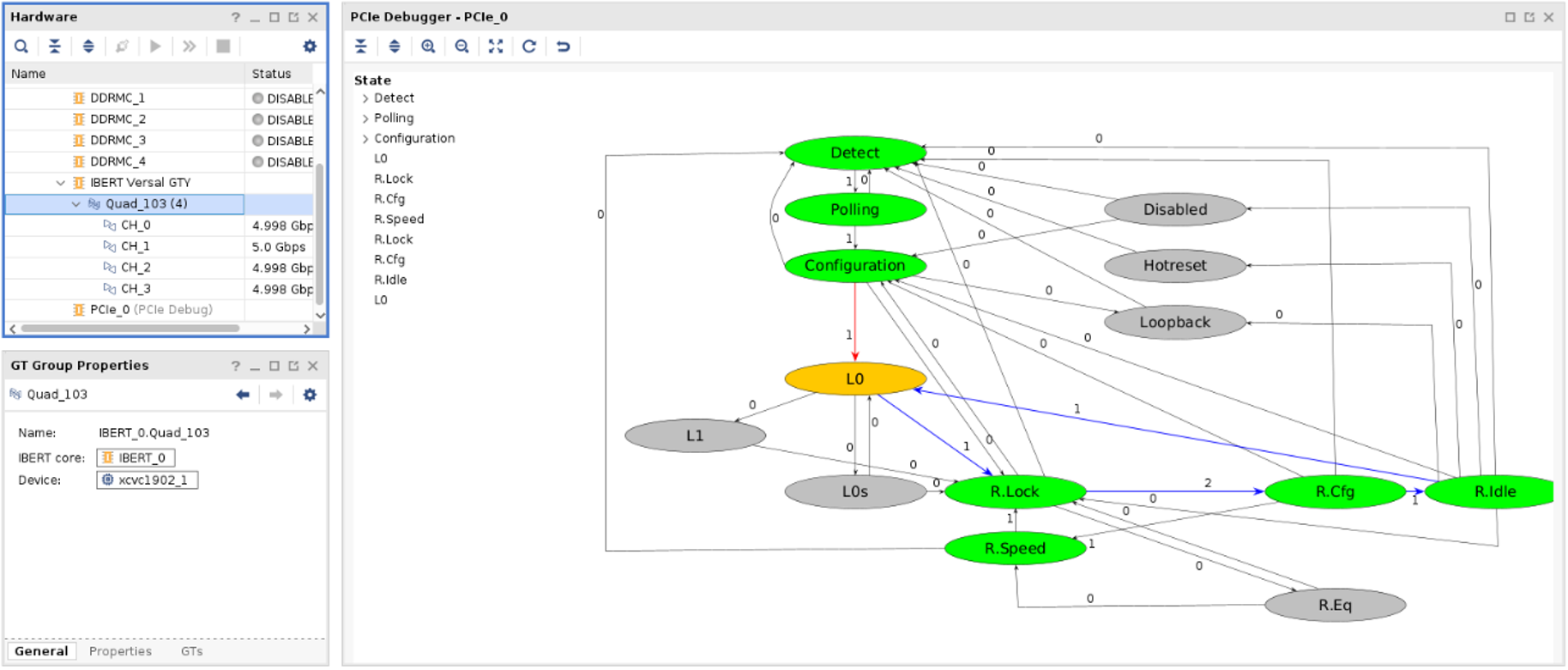

ZCU102の電源をONにし、PCIe Debuggerを更新するとLTSSMが確認できるようになりました。

出典:Vivado® ML Edition

ひとまずIP Packageしても同様の動作することが確認できました。

おわりに

今回は、前回に続きVCK190でPCIe Link Debugの機能を確認しました。

他の機能はもちろん、活用する方法についても、実機で確認でき次第、ブログを通じてお伝いできればと思いますので、次回のブログもどうぞよろしくお願いいたします。

調査依頼や、設計検討などありましたら、お気軽にお問い合わせください。

このブログは「FPGA設計ブログ一覧」の

Versal Acap関連のひとつです。

最後までお付き合いいただきありがとうございました。