【Versal™ACAP】PCIe Link Debug【Vivado® ML 2021.2】

みなさん、こんにちは。

今回は、VCK190上でPCIe Link Debugの機能を確認してみたいと思います。

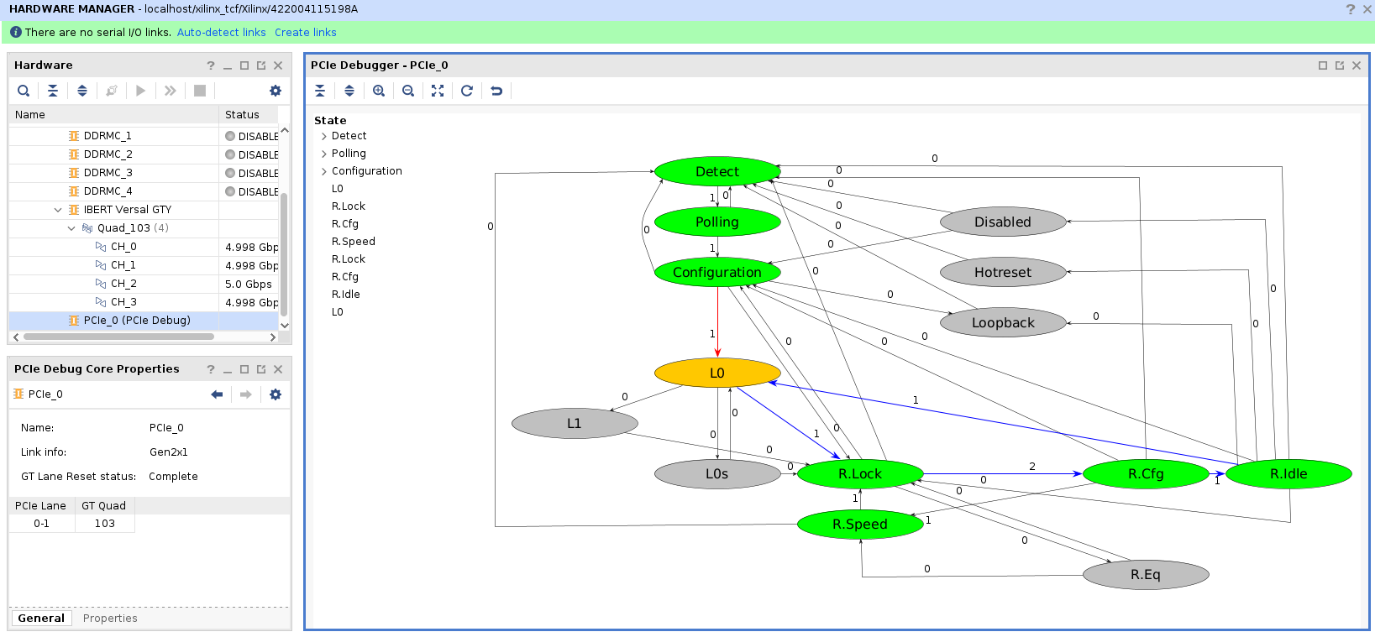

本機能を使うと、下図のようにILAなどを使わずにPCIeのLink状態をLTSSMステータスで確認することができます。

出典:Vivado® ML Edition – Versal ACAP Integrated Block for PCI Express Example Design

それでは、始めましょう。

このブログは「FPGA設計ブログ一覧」の

Versal Acap関連のひとつです。

目次

今回は、以下の環境で実行します。

- ・HostPC CentOS 7.6

- ・Vivado® ML Edition 2021.2

Vivado® ML Edition

それでは、デザインを作成していきます。

今回のデザインは、PCIe Link Debug Demo [1]を参照しておりますので、そちらも是非参照ください。

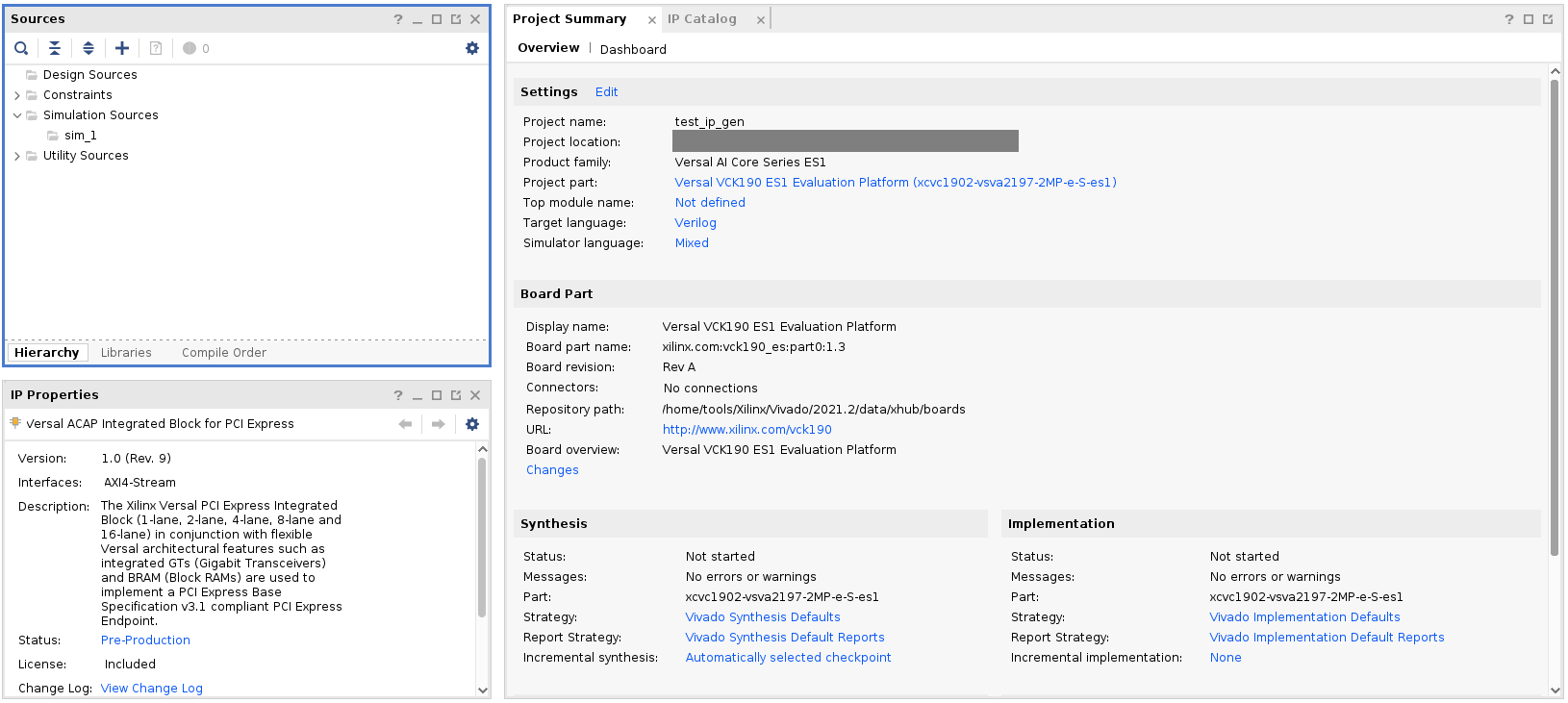

VCK190 es評価ボードを選択したプロジェクトを作成

出典:Vivado® ML Edition

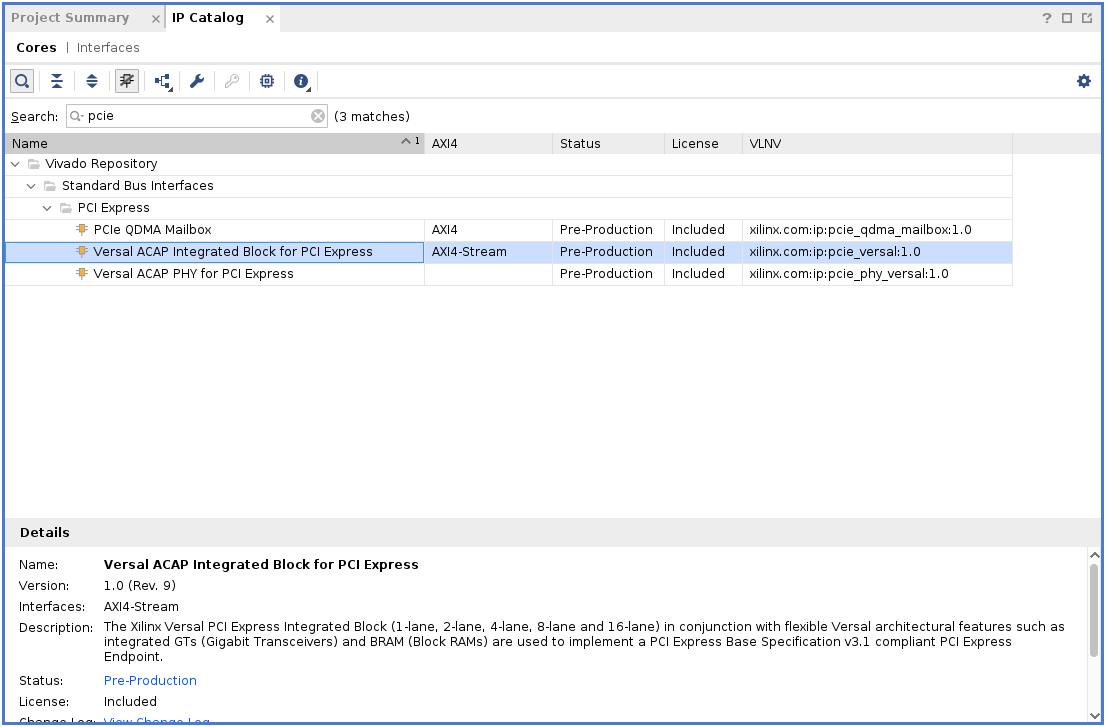

IP Catalogから「Versal ACAP Integrated Block for PCI Express」を生成

出典:Vivado® ML Edition

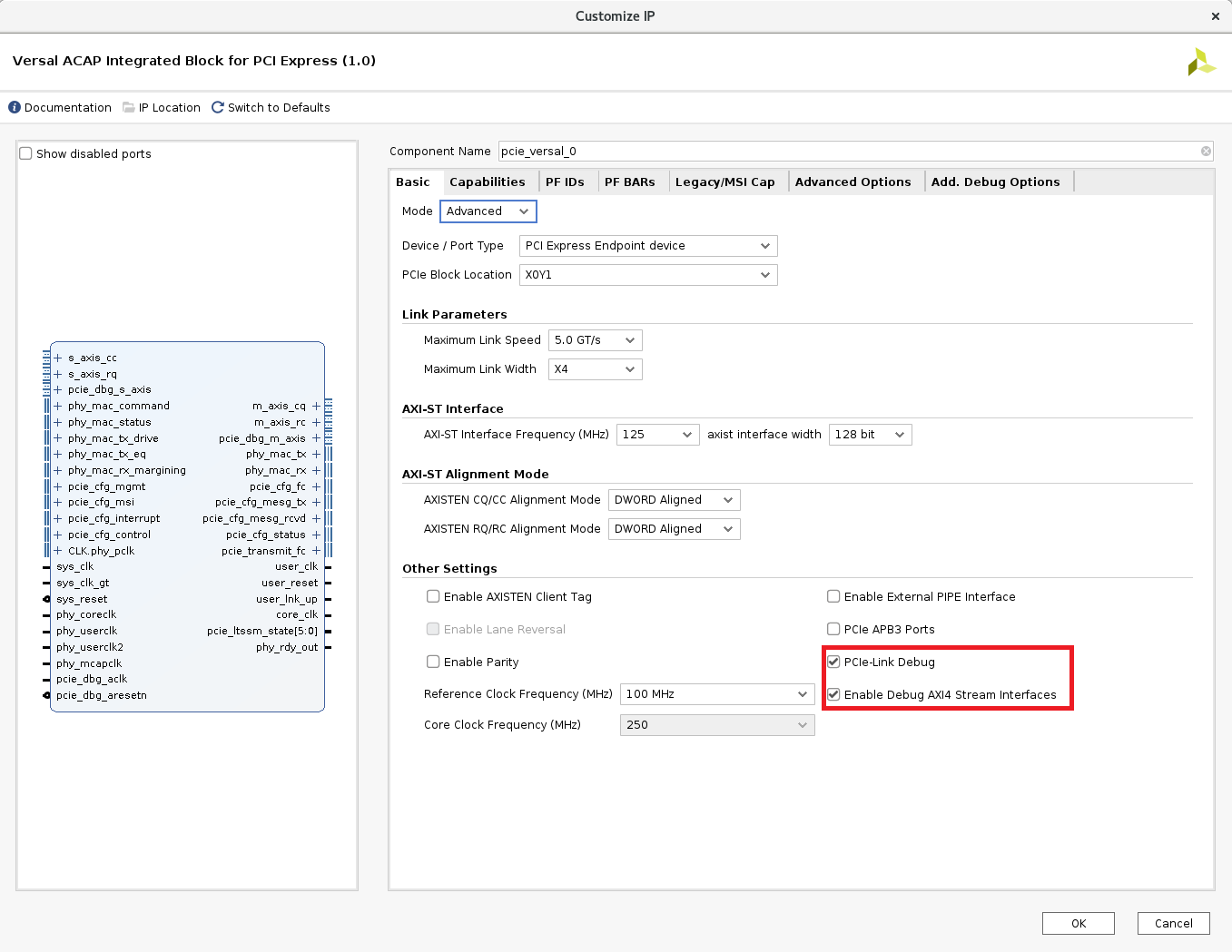

今回は、VCK190側をEndとし、Gen2 x4の設定にします。

このとき、「PCIe-Link Debug」と「Enable Debug AXI4 Stream Interfaces」を有効にすることが重要です。

出典:Vivado® ML Edition

以下コマンドをTcl Consokeで実行します。

set_property config.insert_cips {true} [get_ips pcie_versal_0]- ※

- もしIPを生成したのが、Block Design上の場合、上記コマンドではなく、Block Designを開いて以下コマンドを実行します。

set_property config.insert_cips {true} [get_bd_cells /pcie_versal_0]IPを右クリック⇒Open IP Example Designを実行

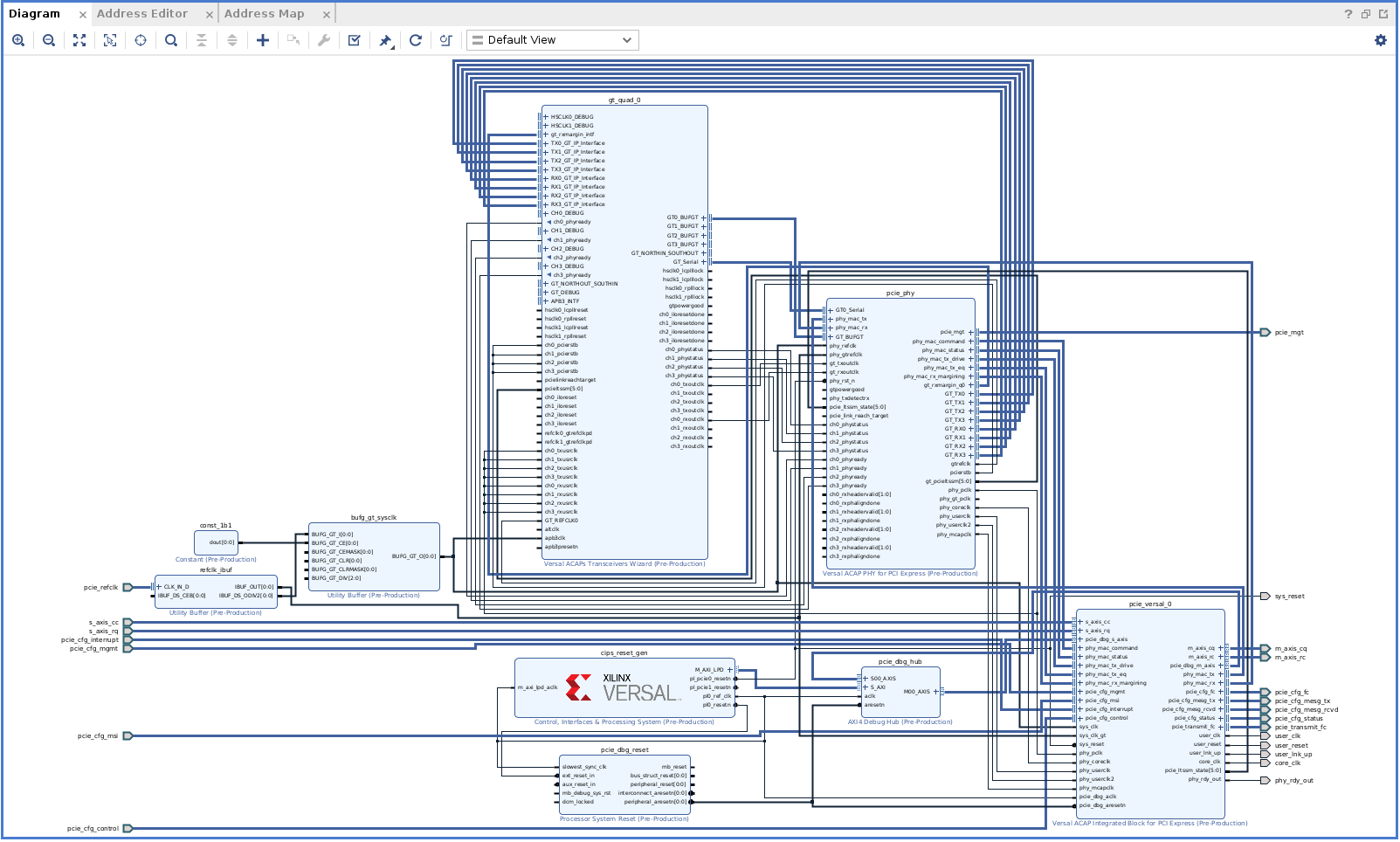

以下図のようなBlock Designとテスト用ソースが生成されます。

出典:Vivado® ML Edition

Generate Device Imageを実行し、PDIファイルを作成できれば準備完了です。

実行

PDIファイルが作成できたら、次はVCK190に書き込みを行います。

今回は、VCK190側がEndなので、RootとしてZCU102を使います。

ZCU102側はPSにPCIeを設定後、Linuxが立ち上がるように作成しています。

こちらについては、詳細を割愛します。

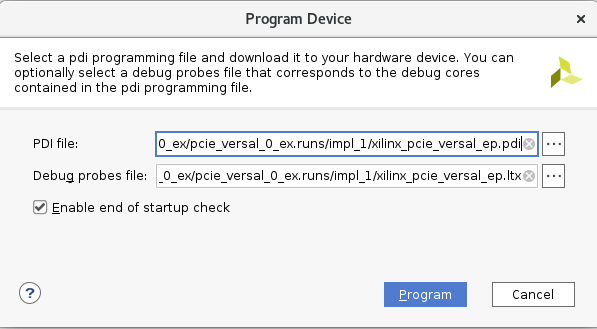

VCK190とZCU102を接続後、Vivado® ML Edition でOpen Hardware Managerを実行し、PDIファイルとLTXファイルを選択して書き込みを実行します。

ZCU102側は電源をOFFにしています。

出典:Vivado® ML Edition

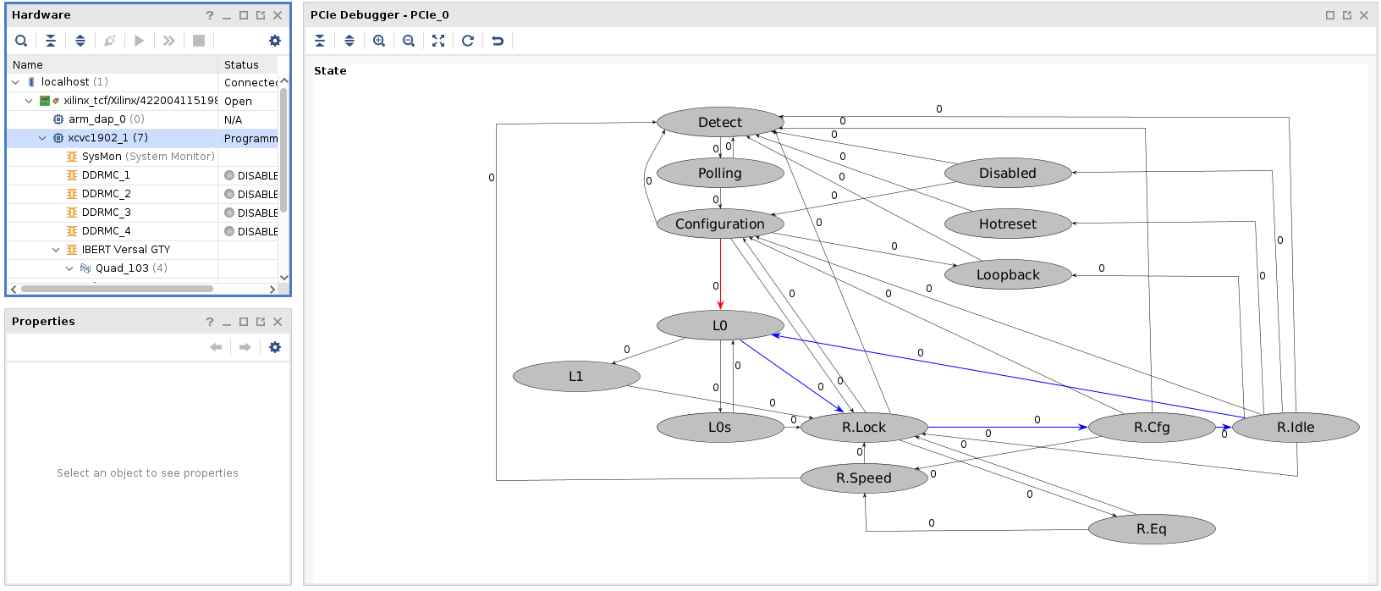

書き込み後、Vivado® ML Edition 上でPCIe Debuggerが見えます。

出典:Vivado® ML Edition

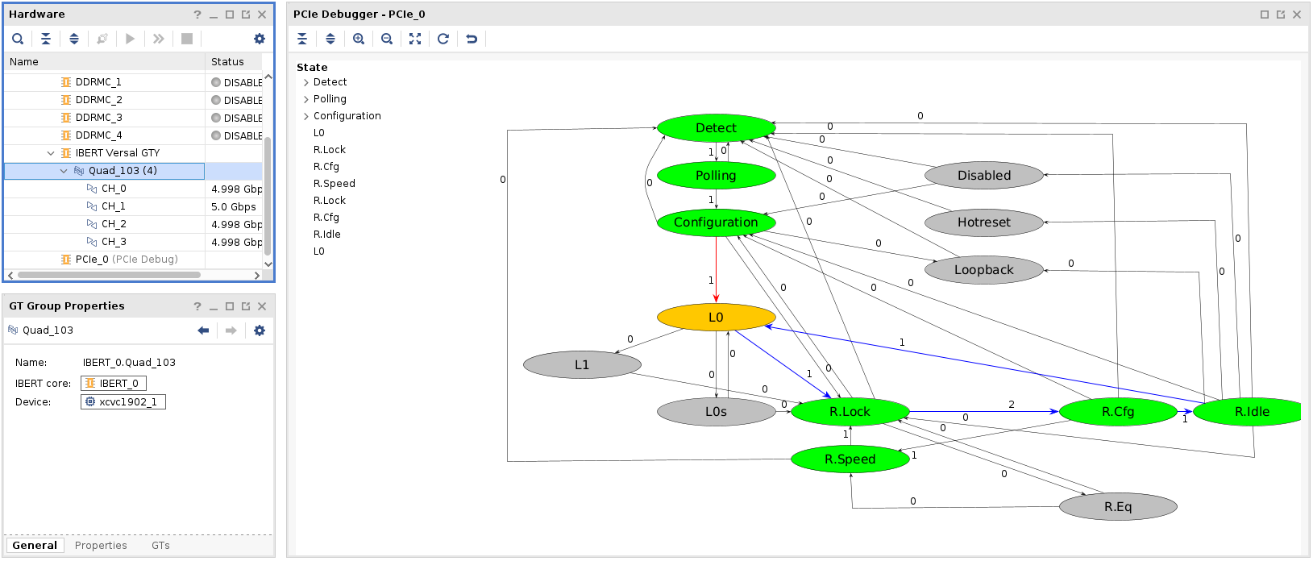

ZCU102の電源をONにして、PCIe Debuggerを更新するとLTSSMが確認できるようになりました。

出典:Vivado® ML Edition

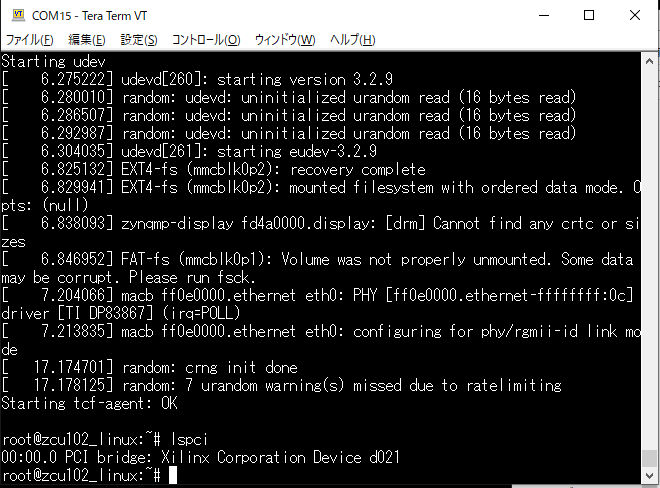

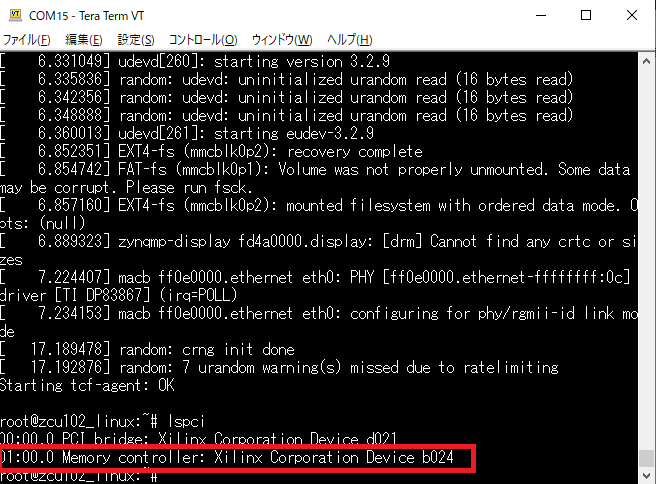

ZCU102側からもPCIデバイスが増えたことが確認できました。

1枚目が未接続、2枚目が接続後になります。

出典:シリアルコンソール画面

出典:シリアルコンソール画面

おわりに

今回は、VCK190でPCIe Link Debugの機能を実機で確認しました。

PCIeの機能を用いたデザインに対して、活用する方法[2][3]についても、実機で確認でき次第、ブログを通じてお伝えできればと思いますので、次回のブログもどうぞよろしくお願いいたします。

調査依頼や、設計検討などありましたら、お気軽にお問い合わせください。

このブログは「FPGA設計ブログ一覧」の

Versal Acap関連のひとつです。

最後までお付き合いいただきありがとうございました。