【Vivado® ML 2022.1】をインストールしてVCK190 評価キットのプロジェクトを作成してみた

みなさん、こんにちは。

今回は、Vivado® ML Edition 2022.1をインストールした後、VCK190評価キットのシンプルなプロジェクトを作成し書き込みしてみます。

それでは、始めましょう。

このブログは「FPGA設計ブログ一覧」の

Versal Acap関連のひとつです。

目次

今回は、以下の環境で実行します。

- ・HostPC CentOS 7.6

- ・Vivado® ML Editon 2022.1

ツールインストール

今回、ツールインストールはCentOS PCで行います。

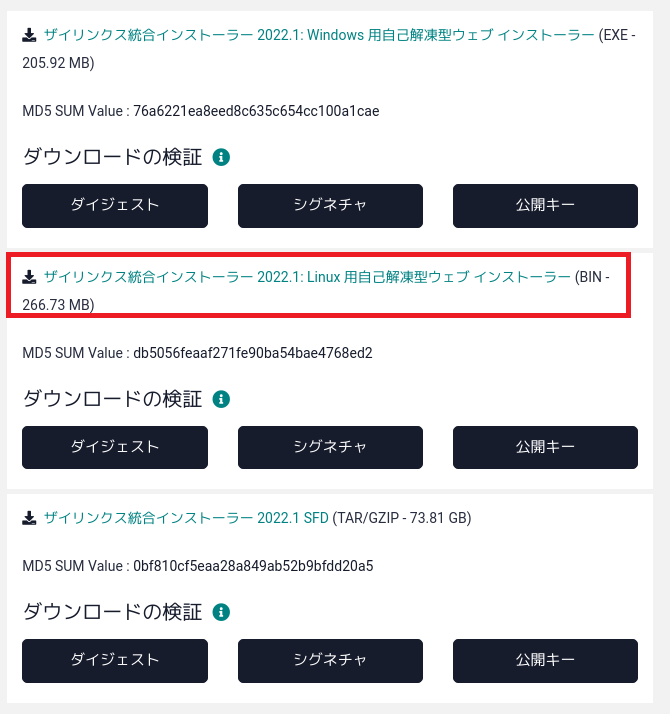

インストーラーのダウンロードは こちら から

統合版インストーラーは、ウェブインストーラーと比べてファイルサイズが大きいため、ウェブインストーラーのLinux版を使用します。

出典: AMD ザイリンクスダウンロード

早速始めてみましょう。

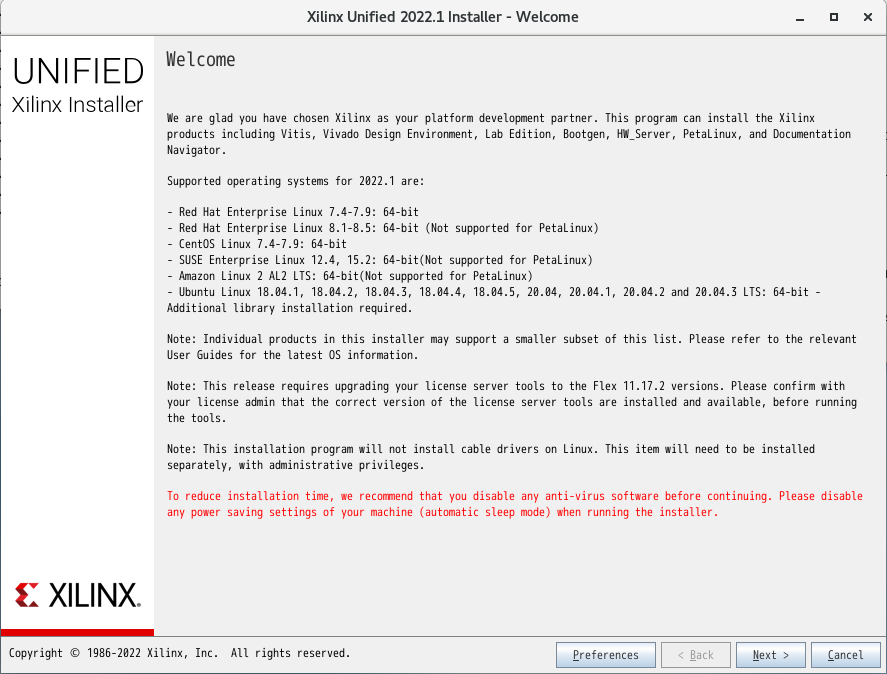

まずはダウンロードしたインストーラーに対して、実行権限を付与してから実行します。

chmod +x ./Xilinx_Unified_2022.1_0420_0327_Lin64

./Xilinx_Unified_2022.1_0420_0327_Lin64.bin以下Welcome画面です。

出典:Vivado® ML Edition ウェブインストーラー

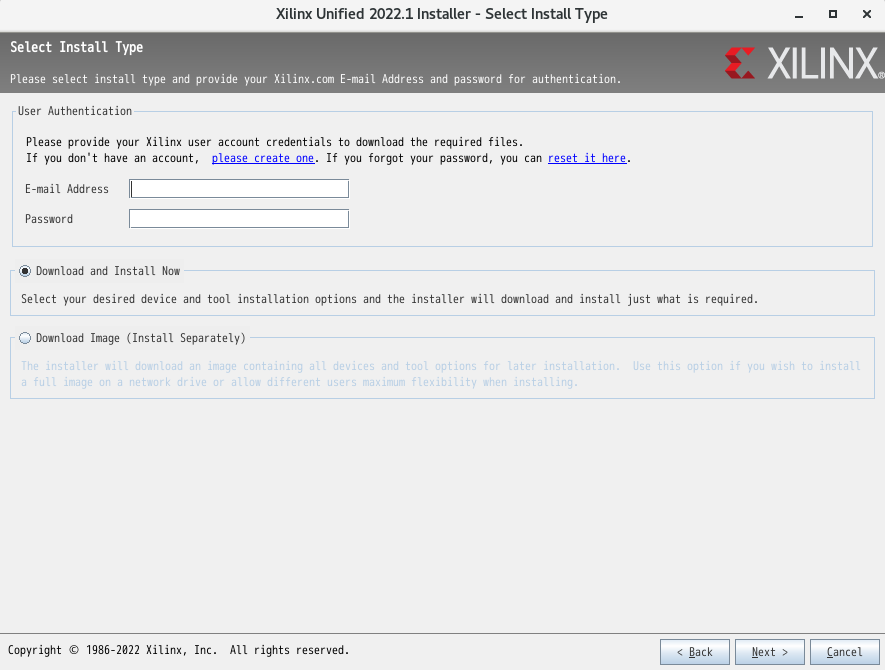

以下Select Install Type画面です。

AMD ザイリンクス アカウントのE-mail AddressとPasswordを入力します。

出典:Vivado® ML Edition ウェブインストーラー

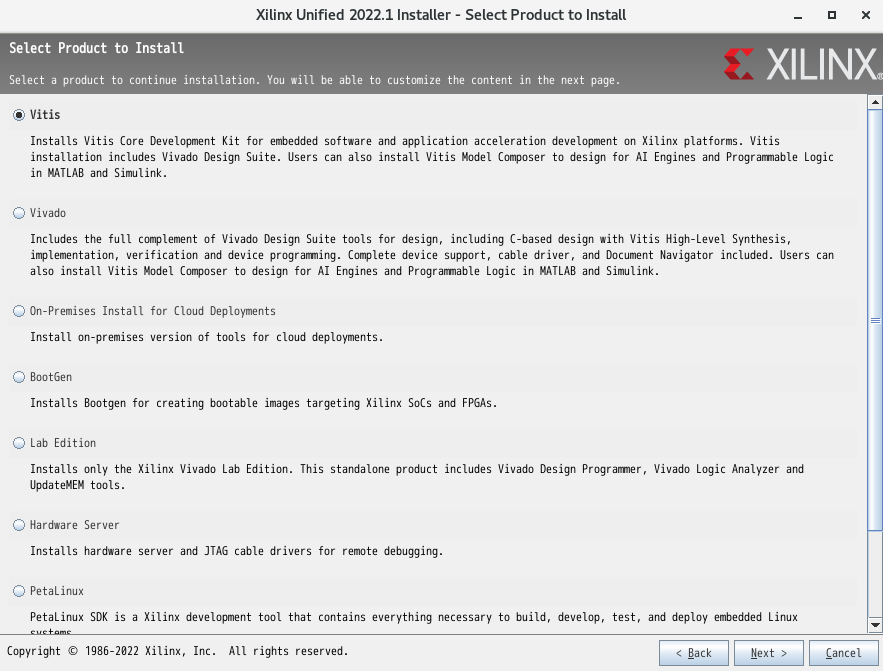

以下Select Product to Install 画面です。Vitisを選択します。

出典:Vivado® ML Edition ウェブインストーラー

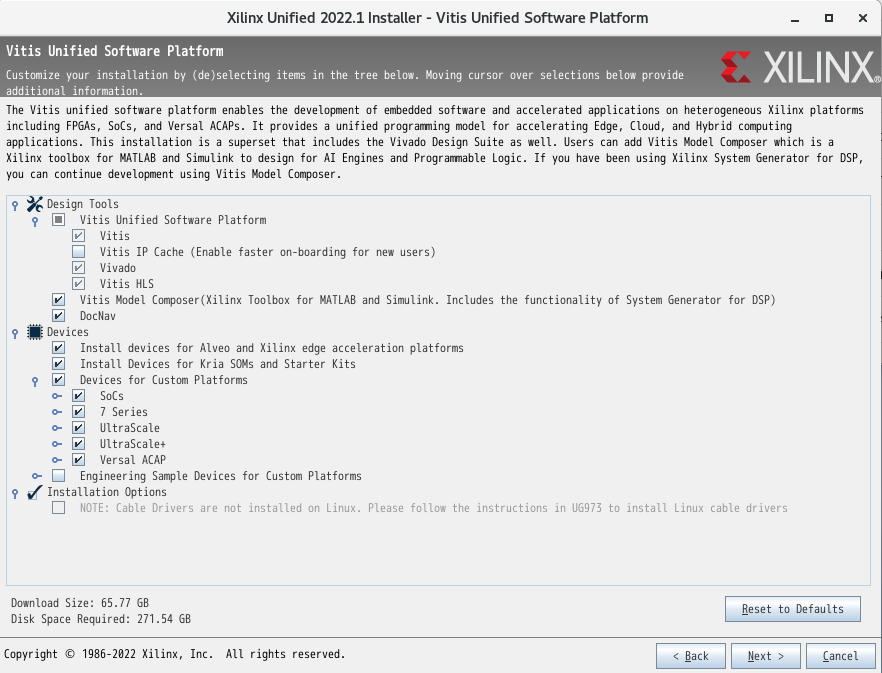

以下Vitis Unified Software Platform画面です。

すべてを選択するとその分だけ必要な領域は大きくなりますので、必要な分だけ選択します。

出典:Vivado® ML Edition ウェブインストーラー

※Accept License Agreements →

Select Destination Directoryは割愛します。

インストール開始して終了を待ちます。

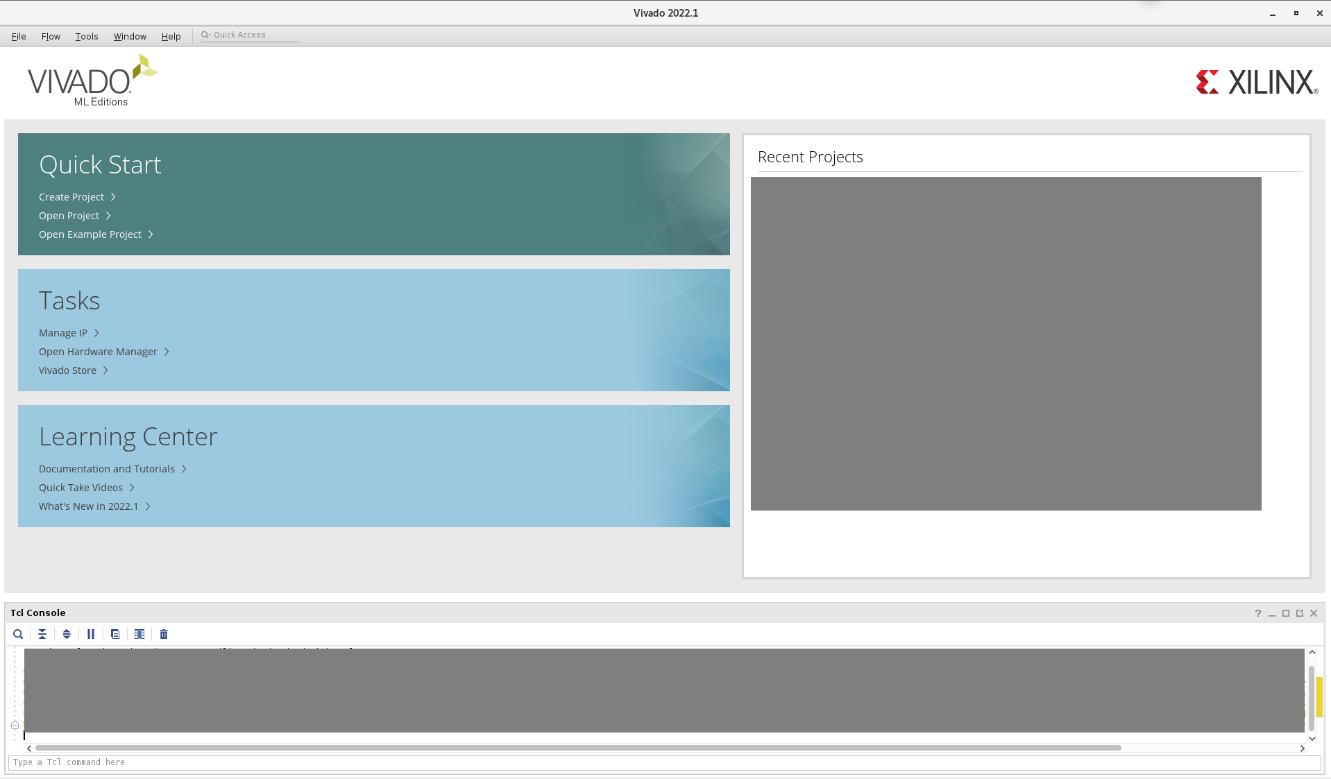

インストールが完了し、起動して終了です。

出典:Vivado® ML Edition

プロジェクト作成

~ PDI作成まで

早速プロジェクトを作成してみます。こちらも作成までの画面を一部展開します。

プロジェクト作成

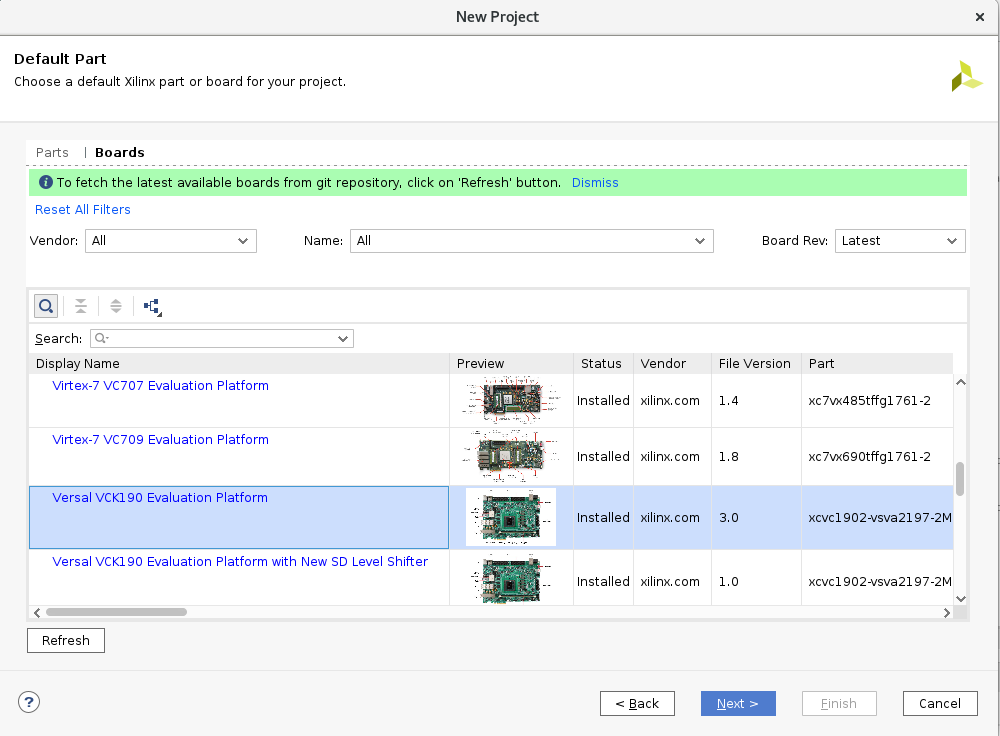

Create ProjectからNextを選択して進めます。Default Part画面です。

今回はVersal VCK190評価キットを選択します。

出典:Vivado® ML Edition

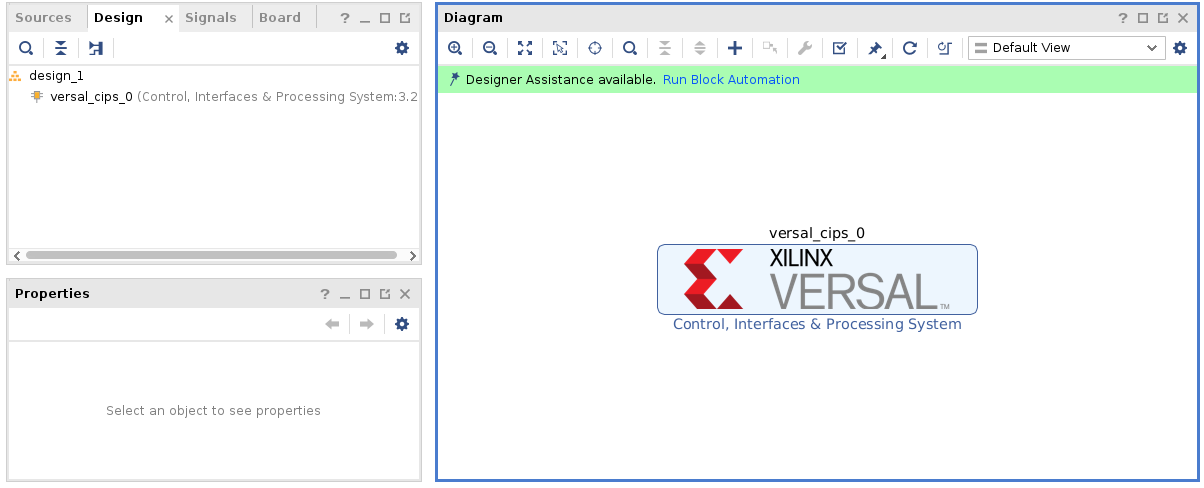

プロジェクトが作成されたら、次にブロックデザインを作成します。

とりあえず、CIPSを置きます。

出典:Vivado® ML Edition

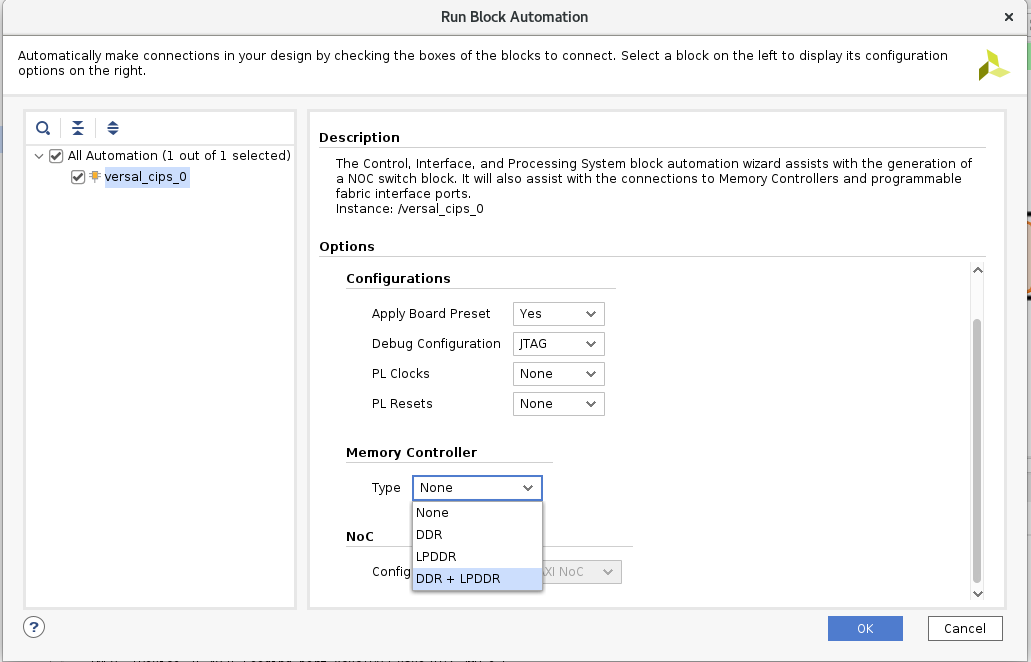

Run Block Automationを選択します。

DDR+LPDDR4が選択可能になっているので、有効にしてみます。

出典:Vivado® ML Edition

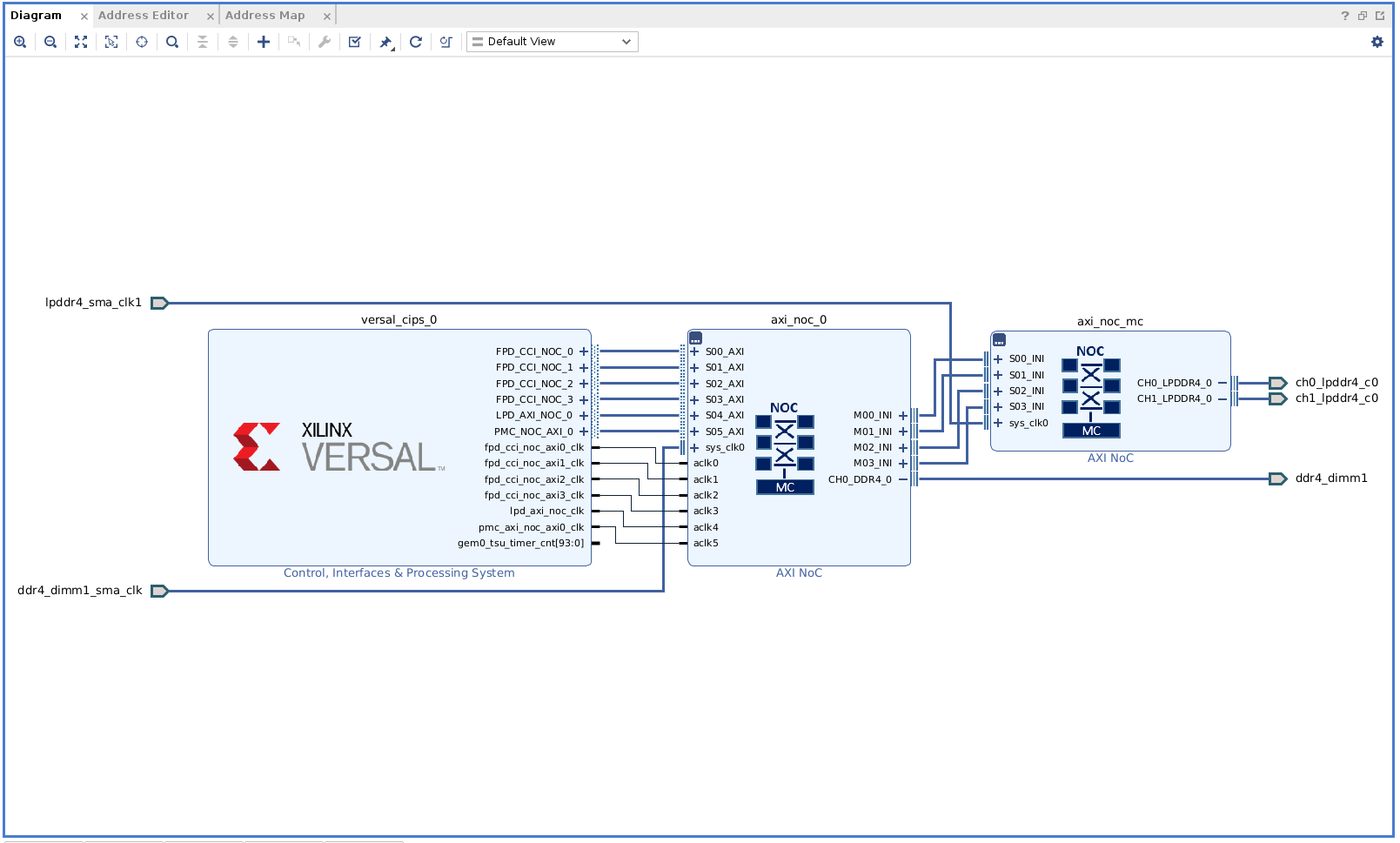

各IPが生成されました。

出典:Vivado® ML Edition

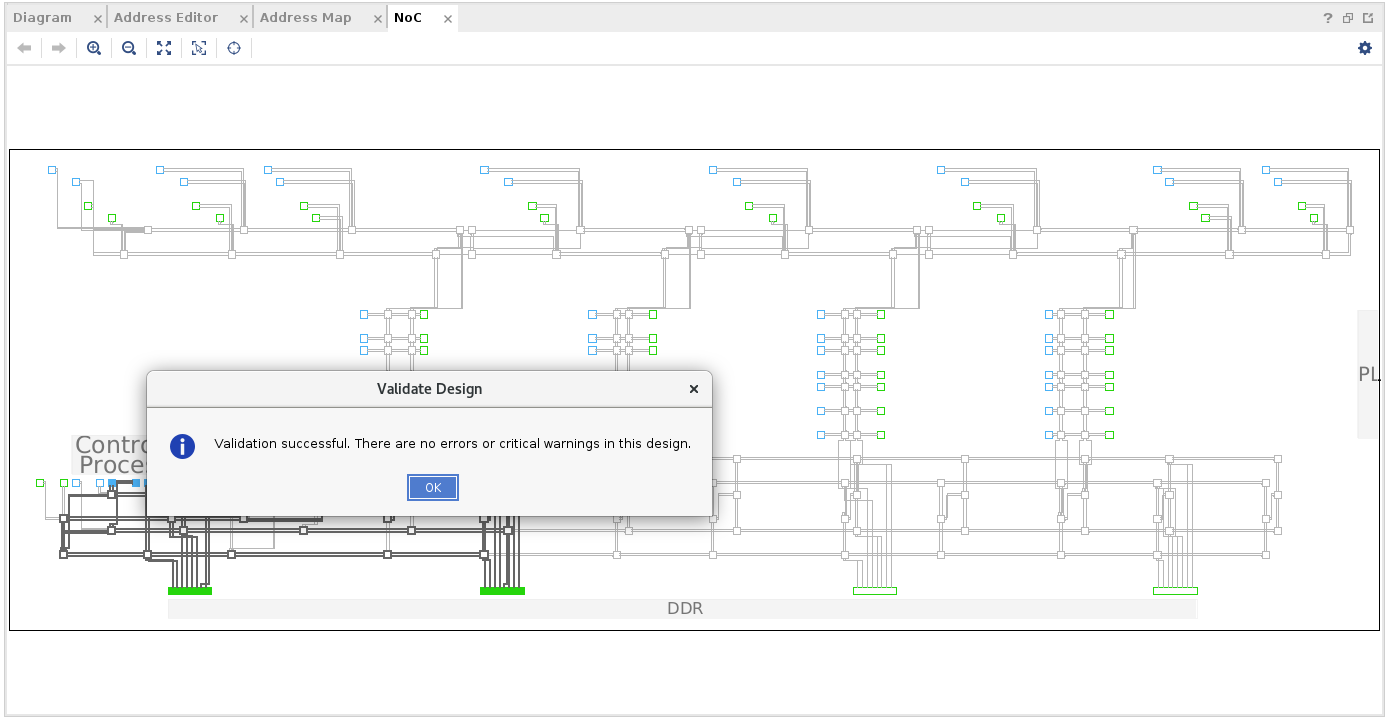

F6を押すなどをして、Validateを実行します。

出典:Vivado® ML Edition

PDI作成

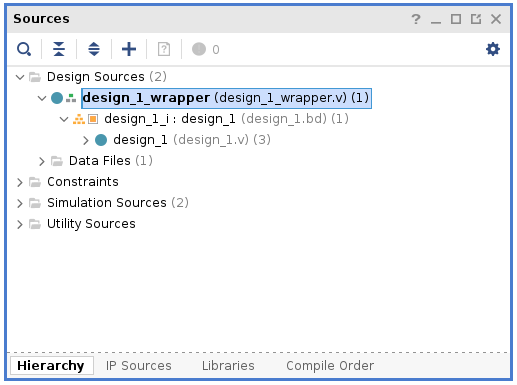

Create HDL Wrapper → Generate Device Image と選択して、書き込み用のPDIファイルを作成します。

出典:Vivado® ML Edition

PDIファイルの作成が完了できました。

インプリメント時に使うコア数が半分くらいで、時間はトータルで10分程度でした。

ここで書き込みまで行う予定でしたが、今手元にはVCK190es版しかなく、どうやらVivado® ML 2022.1では、VCK190esのデバイスであるXCVC1902-ES1がサポートされていないようです。[1]

今回は、PDI作成までとします。

おわりに

今回は、Vivado® ML 2022.1のインストールとシンプルなデザインを作成してみました。

今回は、PDI作成までとなりましたが、実機確認についての様子もブログを通じてお伝えできればと思いますので、次回のブログもどうぞよろしくお願いいたします。

調査依頼や、設計検討などありましたら、お気軽にお問い合わせください。

最後までお付き合いいただきありがとうございました。

弊社ではFPGA設計や回路図設計、レイアウト設計、ソフトウェア設計、筐体設計などを受託開発しています。サービス内容をWEBサイトに掲載していますので、ぜひご覧ください。

このブログは「FPGA設計ブログ一覧」の

Versal Acap関連のひとつです。