【Versal™ACAP】HDMI Example Design【Vivado® ML 2021.2】

みなさん、こんにちは。

今回は、VCK190上でHDMI Example Designを動かしてみました。

動作が確認できるまでの過程や注意点をまとめましたので紹介します。

それでは、始めましょう。

このブログは「FPGA設計ブログ一覧」の

Versal Acap関連のひとつです。

目次

今回は、以下の環境で実行します。

- ・HostPC CentOS 7.6

- ・Vivado® ML Edition 2021.2

- ・Vitis™ 2021.2

Vivado® ML Edition

それではデザインを作成していきます。

基本的に、詳細はHDMI 1.4/2.0 Transmitter Subsystem Product Guide (PG235) [1]に記載されているので、大まかな流れと注意点に絞って記載していきます。

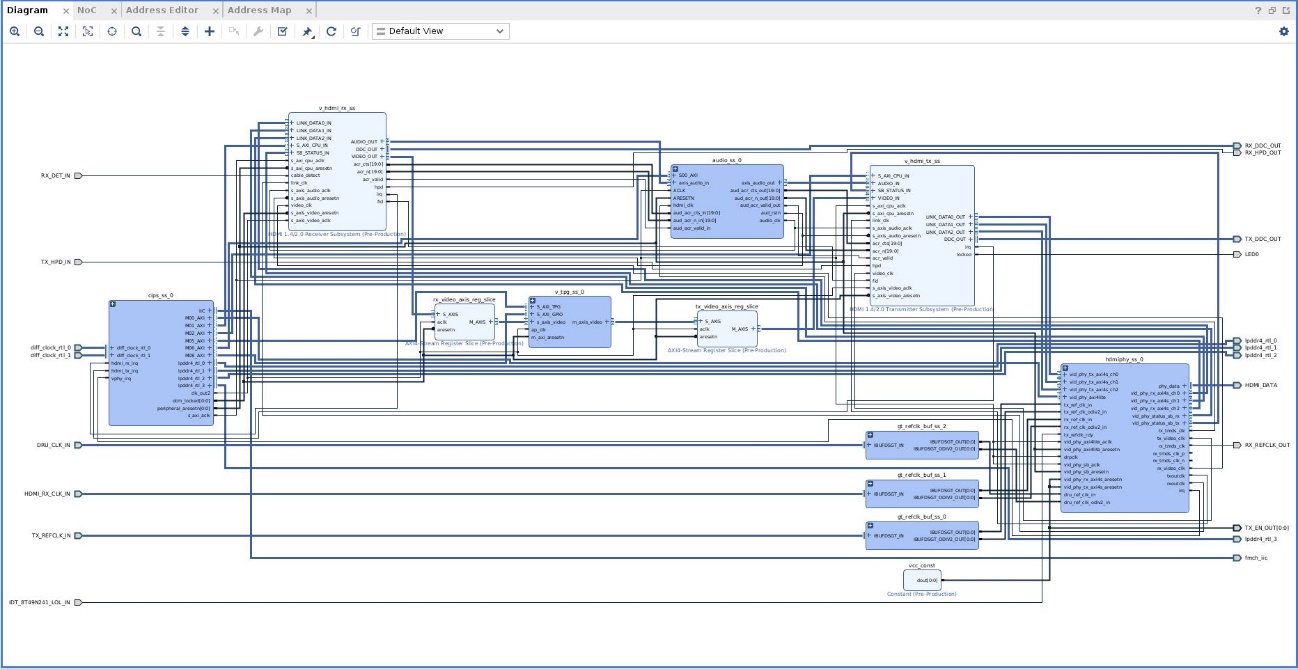

VCK190 es評価ボードを選択したプロジェクト生成後、IP Catalogから「HDMI 1.4/2.0 Transmitter Subsystem」を生成し、右クリック ⇒ Open IP Example Designを実行します。

下図のようなデザインが生成されます。

※画像クリックで大きな画像が表示されます。

出典:Vivado® ML Edition - HDMI Example Design

注意点①

※デザインをImplimentする前にご確認ください。

Versal™ AI コア シリーズ VCK190 評価キットでDIMMを使用したデザインをVitis Baremetalで操作する際は、インプリメントする前に以下のコマンドをTclで打ち込む必要があります。

set_param noc.enableNOCClockGating 0詳細は以下リンク[2]を参照してください。

注意点②

2022年移行で、次のパッチを当てていない場合、Implimentの途中でエラーが発生する可能性があります[3]。詳細は、以下を参照してください。

https://support.xilinx.com/s/article/76960?language=ja

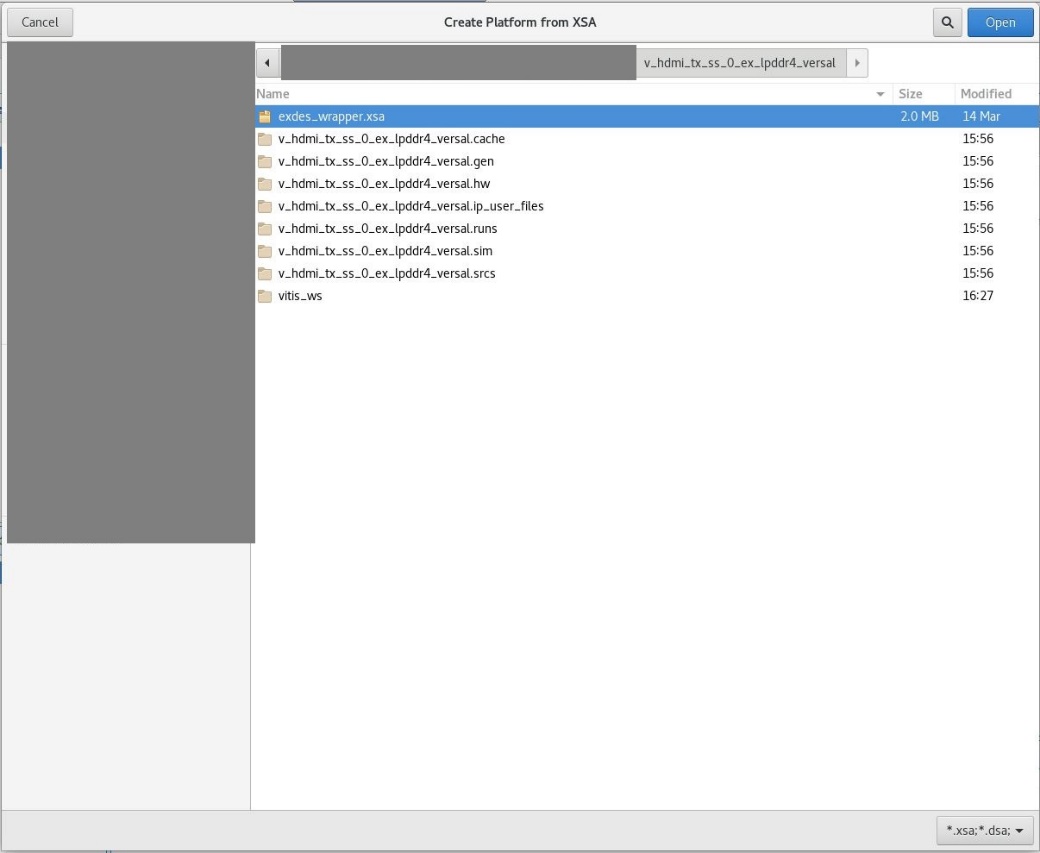

インプリメント完了後、HW ExportでXSAを生成します。

Vitis™

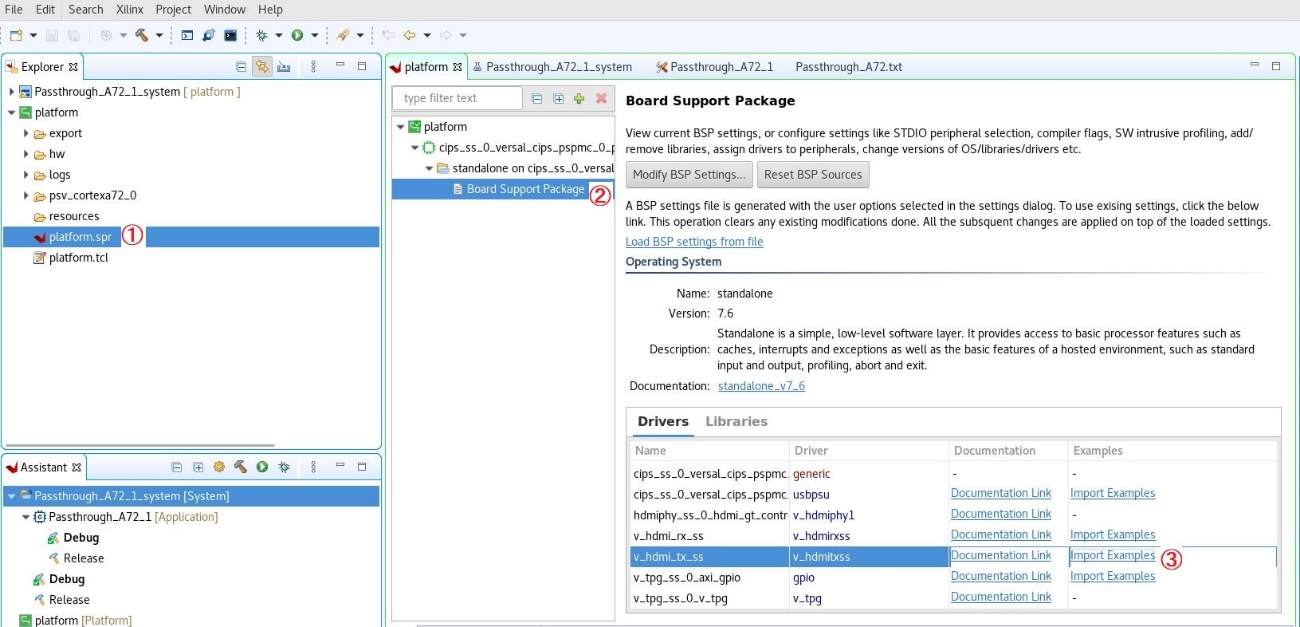

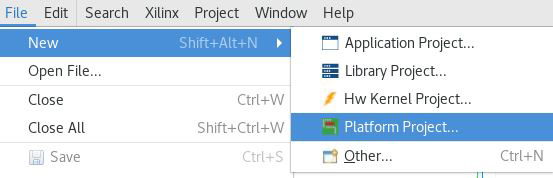

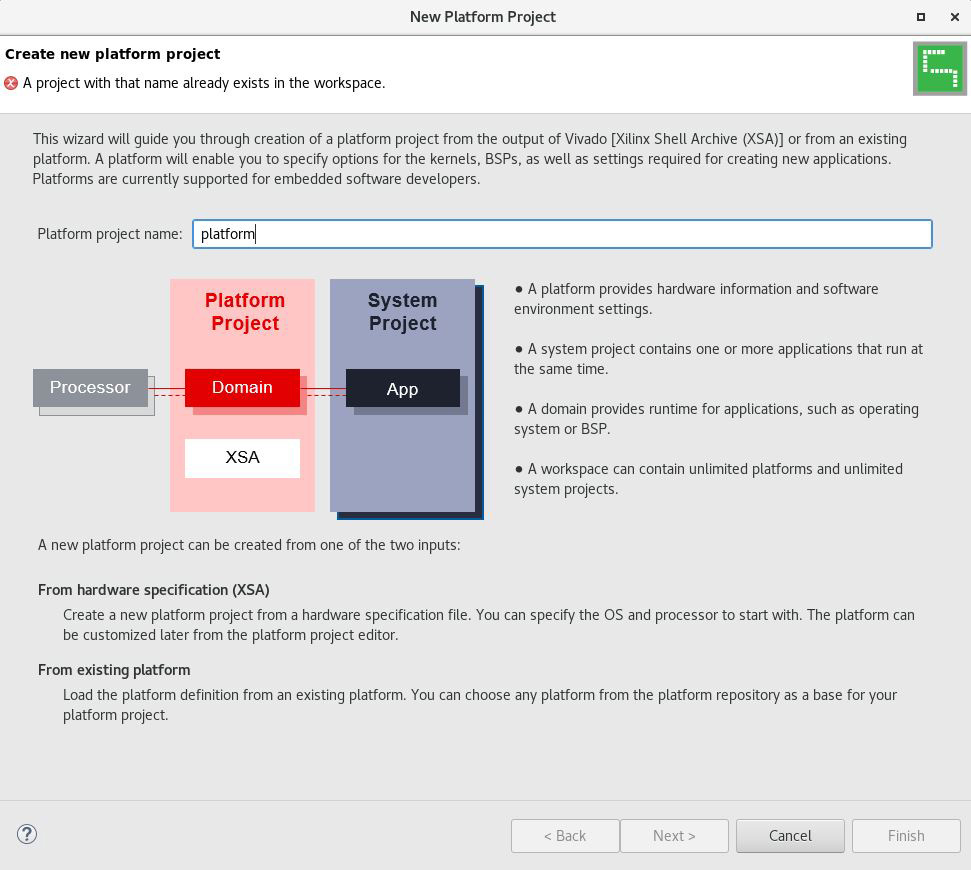

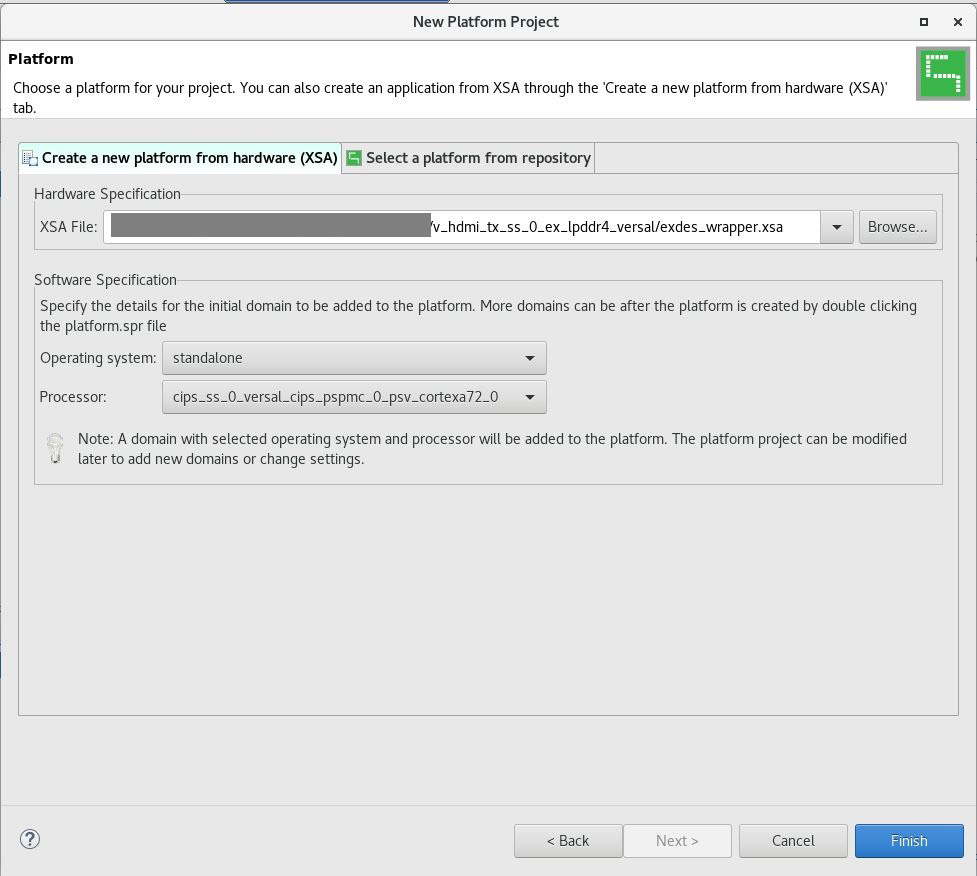

まずPlatform Project作成します。

出典:Vitis™

出典:Vitis™

出典:Vitis™

出典:Vitis™

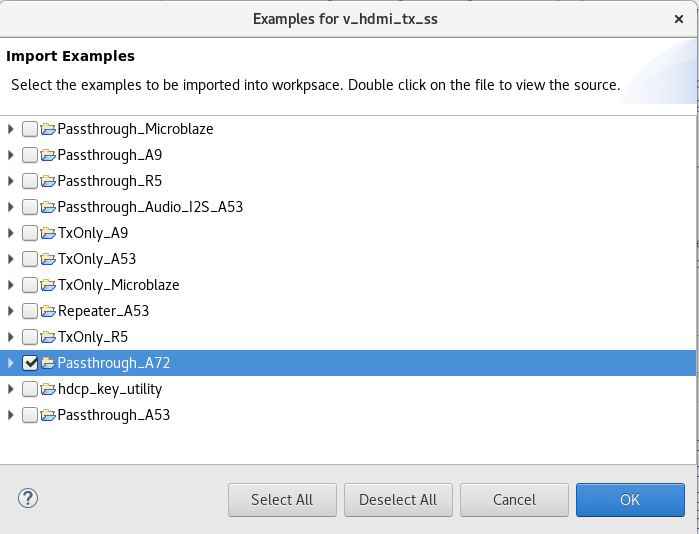

Platform Project作成後、platform.spr > Board support package > v_hdmi_tx_ss のImport Exampleから「Passthrough_A72」を選択します。

※画像クリックで大きな画像が表示されます。

出典:Vitis™

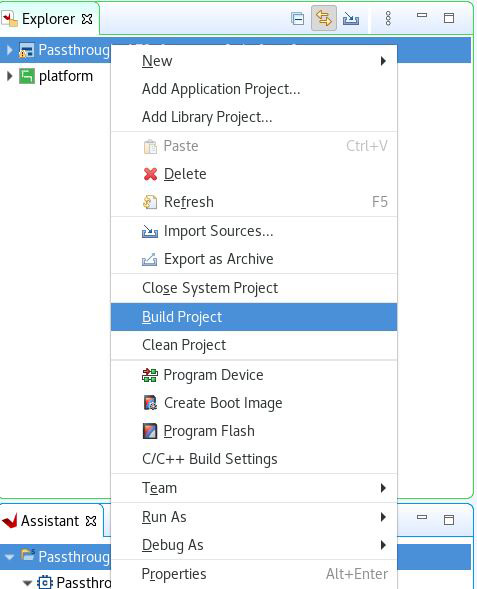

出典:Vitis™

出典:Vitis™

Build完了後、実行に移ります。

実行

ここからは、端末上からの操作に移行します。

Exampleデザインの階層にCurrent Directoryで移動します。

$cd ./<IP instance name>_exその後、システムデバッガーを使うため、xsdbを起動します。

$ vivado -mode tcl

Vivado% xsdbJTAGターゲットをリストします。

xsdb% connect

xsdb% targets

1 Versal vjtag40

2 RPU (PS POR is active)

3 Cortex-R5 #0 (PS POR is active)

4 Cortex-R5 #1 (PS POR is active)

5 APU (FPD domain isolation)

6 Cortex-A72 #0 (FPD domain isolation)

7 Cortex-A72 #1 (FPD domain isolation)

8 PPU

9 MicroBlaze PPU (Sleeping after reset)

10 PSM

11 PMC

12 PL

13 DPCPDIをダウンロードします。

xsdb% device program ./<IP instance name>_ex.runs/impl_1/exdes_wrapper.pdi

xsdb% after 1000ターゲットプロセッサーをセットします。

xsdb% targets -set -filter {name =~ "Cortex-A72 #0"}

xsdb% rst -proc

xsdb% after 1000.elfをダウンロードします。

xsdb% dow ./<vitis_workspace>/<application_name>_1/Debug/<application_name>_1.elf実行します。

xsdb% conXSDBを出るときは、以下を実行します。

xsdb% exit注意点③

con実行時、HDMIの入力にノートPCを使用する際、HDMI出力がうまく映らない場合は、ノートPCの設定を画面複製ではなく、画面拡張にするとうまく映る可能性があります。

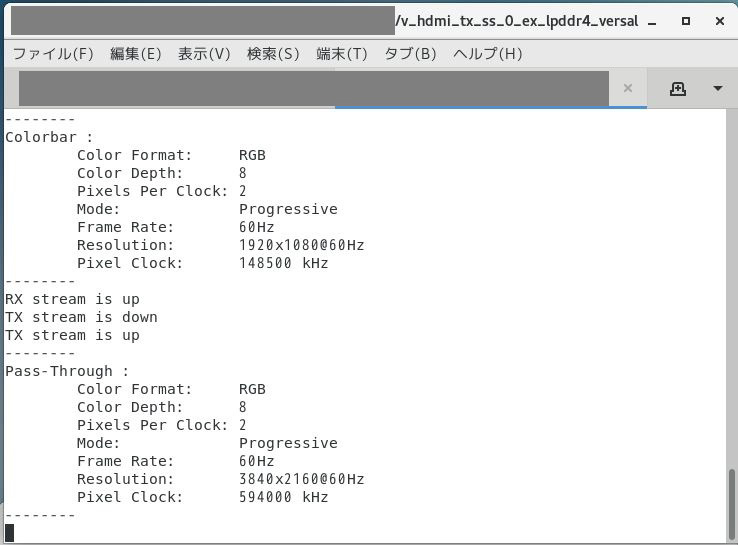

con実行後、シリアルコンソールに以下のような状態が表示されます。

出典:シリアルコンソール画面

出力先選択後、HDMIのカメラの映像が映りました。

おわりに

今回は、VCK190でHDMI Example Designの実機確認と実行までの注意点について解説しました。

別インターフェースのExampleデザインについても、ブログを通じてお伝えできればと思いますので、次回のブログもどうぞよろしくお願いいたします。

調査依頼や、設計検討などありましたら、お気軽にお問い合わせください。

このブログは「FPGA設計ブログ一覧」の

Versal Acap関連のひとつです。

最後までお付き合いいただきありがとうございました。

- 参考文献

-

[1] HDMI 1.4/2.0 Transmitter Subsystem Product Guide

https://japan.xilinx.com/content/dam/xilinx/support/documentation/ip_documentation/v_hdmi_tx_ss/v3_2/pg235-v-hdmi-tx-ss.pdf

[2] Cannot run a bare-metal PS application with Cortex A72 using Vitis IDE on VCK190

https://support.xilinx.com/s/question/0D52E00006ihQLlSAM/cannot-run-a-baremetal-ps-application-with-cortex-a72-using-vitis-ide-on-vck190?language=ja

[3] Export IP Invalid Argument / Revision Number Overflow Issue (Y2K22)

https://support.xilinx.com/s/article/76960?language=ja