【Versal™ACAP】I2C Example Design【Vivado® ML 2021.1】

みなさんこんにちは。

今回は、Versal AI コア シリーズ VCK190 評価キット上でI2C Example Designを動かしてみました。

動作が確認できるまでの過程や注意点をまとめたので紹介します。

それでは、始めましょう。

このブログは「FPGA設計ブログ一覧」の

Versal Acap関連のひとつです。

目次

今回は、以下の環境で実行します。

- ・HostPC CentOS 7.6

- ・Vivado® ML Edition 2021.1

- ・PetaLinux 2021.1

Vivado® ML Edition

それではデザインを作成します。

今回は以下リンクの内容に沿って進めていきます。詳細はリンク先を参照ください[1]。

https://github.com/Xilinx/Embedded-Design-Tutorials/tree/master/examples/versal/lowspeed_IPs

PLとPS両方のI2Cインターフェースを確認するので、ps_i2cのページとaxi_i2cのページを参照します。

まず端末を起動し、以下コマンドでGitHubからファイル一式をダウンロードします。

$ git clone --recursive https://github.com/Xilinx/Embedded-Design-Tutorials出典:Linuxコンソール画面

ダウンロードが完了したら、フォルダを移動し手順に従って、bd.tclを実行します。

axi_i2c/scriptにあるbd.tclを実行していますが、どれも同じのようです。

※ターゲットデバイスがプロダクト品向けになっていますが、今回使用するボードはes品のため、切り替えます。

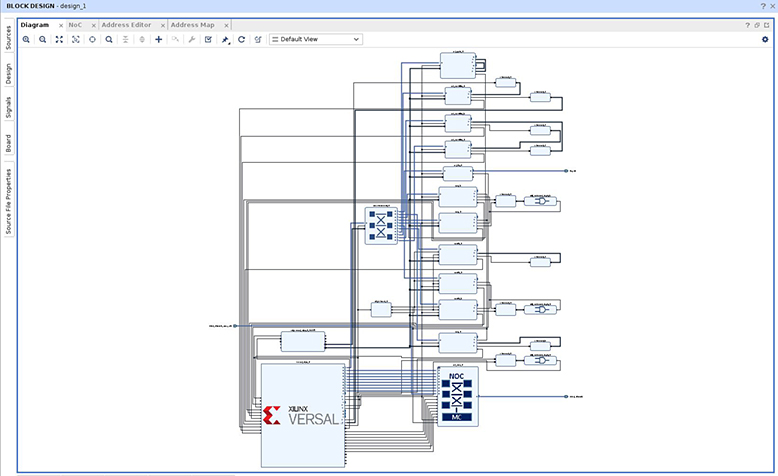

以下のようなブロックデザインが生成されます。

※画像クリックで大きな画像が表示されます。

出典:Vivado® ML Edition

注意点①

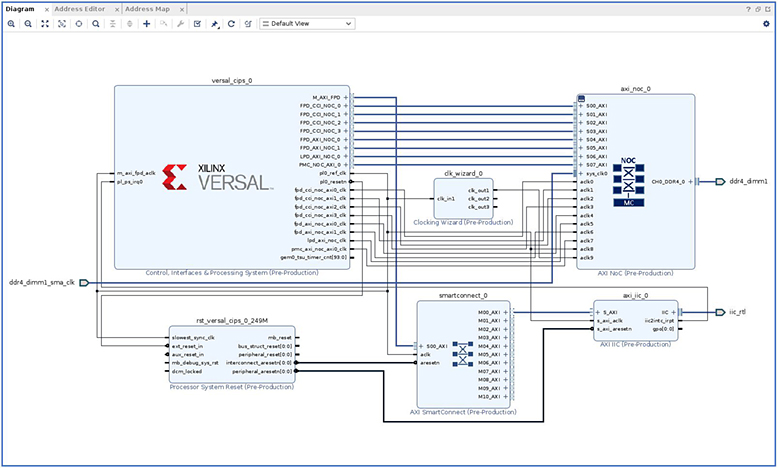

本デザインでは他のインターフェースもテストできるようにI2C以外のIPも配置されていますが、今回は使用しないのと、canfdはライセンスを所持していないので、ブロックデザインから削除します。

以下のようなデザインになりました。

※画像クリックで大きな画像が表示されます。

出典:Vivado® ML Edition

Create HDL Wrapper⇒Generate Device Imageと実行します。

完了後、Export Hardwareを実行し、XSAファイルを生成します。

これでVivado側の作業は終了です。

PetaLinux

GitHubに書かれている手順には、VitisでBaremetalアプリケーションを実行する方法と、PetaLinuxで確認する手順がありますが、今回はPetaLinuxで実行します。

以下コマンドでPetaLinux Projectを作成します。

$ petalinux-create --type project --template versal --name <name_of_project>

$ cd <name_of_project>出典:PetaLinuxコンソール画面

XSAファイルを構成します。

$ petalinux-config --get-hw-description=<PATH TO XSA>出典:PetaLinuxコンソール画面

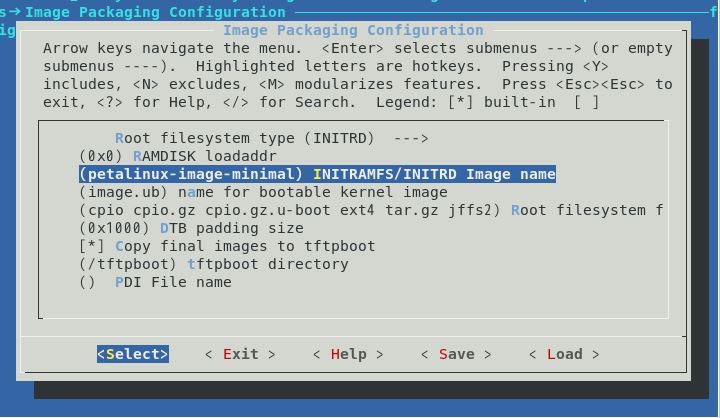

注意点②

PetaLinux 2021.1以前のユーザーはSD Bootファイルを作成する際に以下設定[2]が必要です。

https://support.xilinx.com/s/article/76842?language=en_US

petalinux-config ---> Image Packaging Configuration ---> Root filesystem type --->(INITRD)

petalinux-config ---> Image Packaging Configuration ---> INITRAMFS/INITRD Image Name (petalinux-image-minimal)出典:PetaLinuxコンソール画面

出典:PetaLinux設定画面

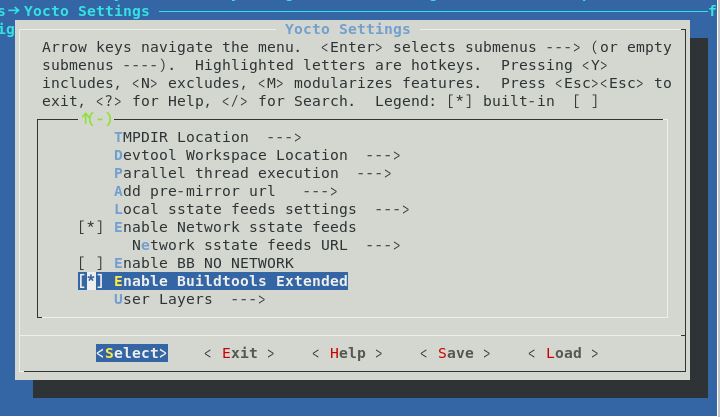

あわせてYocto Setting → EnableBuildtools Extendedも有効にします。

出典:PetaLinux設定画面

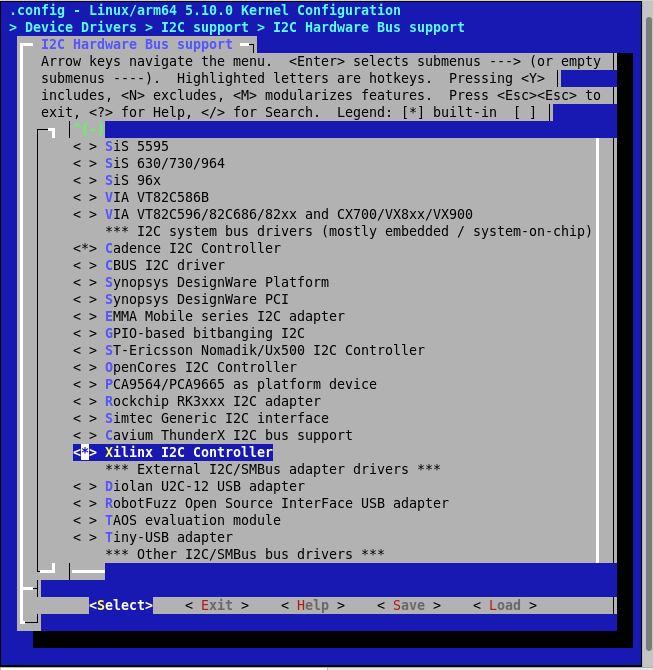

注意点③

petalinux-buildを実行する前に以下コマンドを実行して設定を確認します。

設定が有効になっていない場合は、有効にして、Saveします。

$ petalinux-config -c kernel

Device Drivers ->I2C support -> Hardware Bus support ->enable Xilinx I2C Controller ->Save ->exit

出典:PetaLinuxコンソール画面

出典:Petalinux設定画面

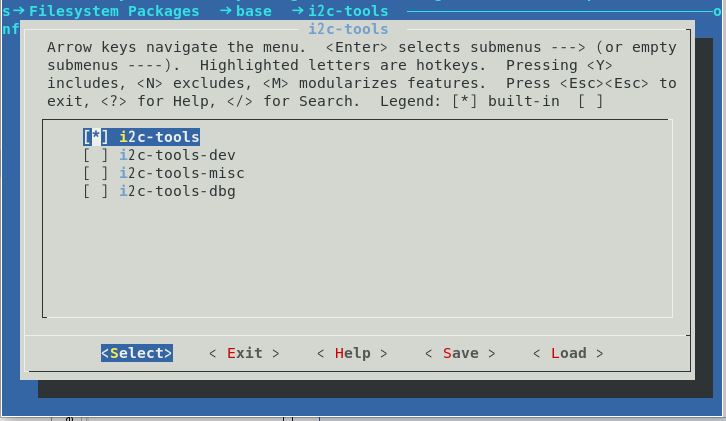

$ petalinux-config -c rootfs

Filesystem Packages ->Base ->i2c-tools ->enable i2c-tools ->save ->exit

出典:Petalinuxコンソール画面

出典:Petalinux設定画面

Buildします。

$ petalinux-build

Filesystem Packages ->Base ->i2c-tools ->enable i2c-tools ->save ->exit

出典:Petalinuxコンソール画面

Build完了後、ブートイメージを作成します。

$ cd ./images/linux

$ petalinux-package --boot --plm --psmfw --uboot --dtb --force

出典:Petalinuxコンソール画面

SDにBOOT.BIN, boot.scr, image.ubを移動します。

これでPetaLinuxの作業は終了です。

実行

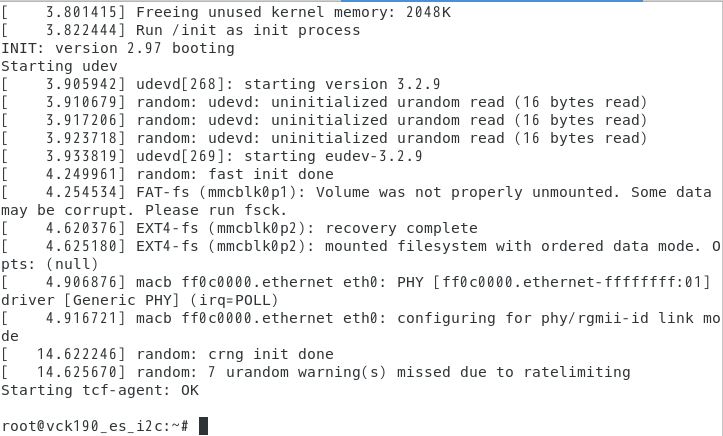

SDカード取り付け後、Dipスイッチの設定を確認して、Versal AI コア シリーズ VCK190 評価キットを起動します。

シリアルコンソールにLinuxが立ち上がることを確認します。

出典:シリアルコンソール画面

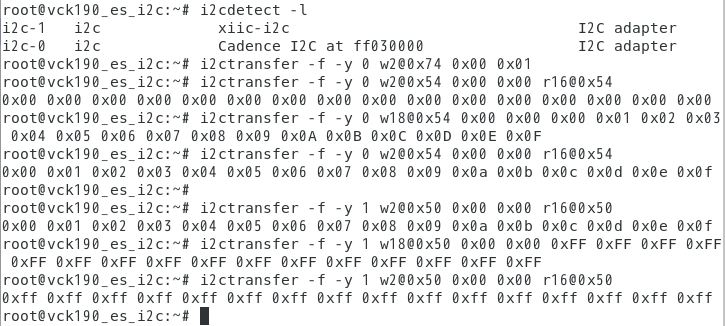

PL、PS共に問題なくRead/Writeができました。

出典:シリアルコンソール画面

おわりに

今回は、Versal AI コア シリーズ VCK190 評価キットを使ってI2C Example Designの実機確認と実行までの注意点について解説しました。

別インターフェースのExampleデザインについても、ブログを通じてお伝えできればと思いますので、次回のブログもどうぞよろしくお願いいたします。

調査依頼や、設計検討などありましたら、お気軽にお問い合わせください。

このブログは「FPGA設計ブログ一覧」の

Versal Acap関連のひとつです。

最後までお付き合いいただきありがとうございました。

- 参考文献

-

[1] Xilinx Embedded-Design-Tutorials:versal/lowspeed_IPs

https://github.com/Xilinx/Embedded-Design-Tutorials/tree/master/examples/versal/lowspeed_IPs

[2] Xilinx known issue 76842:Versal and Zynq UltraScale+ MPSOC: PetaLinux does not mount full rootfs when boot INITRD images are built using the template method

https://support.xilinx.com/s/article/76842?language=en_US