【Versal™ACAP】機能紹介 NoC Simulation編

みなさんこんにちは。

前回はVivado® 上にてNoCのSimulationを行う準備をお見せしました。

【Versal™ ACAP】機能紹介 NoC編

https://www.paltek.co.jp/techblog/techinfo/211116_01

【Versal™ACAP】機能紹介 NoC編(2)

https://www.paltek.co.jp/techblog/techinfo/211223_01

今回は、実際にSimulationの様子をお見せしつつ、作成したデザインについて簡単に紹介させていただきたいと思います。

ご不明点などございましたら、本ページ下部からお気軽に問い合わせいただければと思います。

それでは、始めましょう。

このブログは「FPGA設計ブログ一覧」の

Versal Acap関連のひとつです。

目次

Simulationの実行まで

今回は、以下の環境で実行します。

- CentOS 7.6

- Vivado® 2020.2

前回の記事で、ブロックデザインとラッパーの準備を行いました。

実は、Simulation実行の準備は既に完了しており、あとはVivado® 上のFlow NavigatorからRun Simulation→Run Behavioral Simulationを実行するだけです。

テストベンチの作成や、リセット系、クロック系の追加設定などは不要です。

これについては後のデザイン紹介にて説明します。

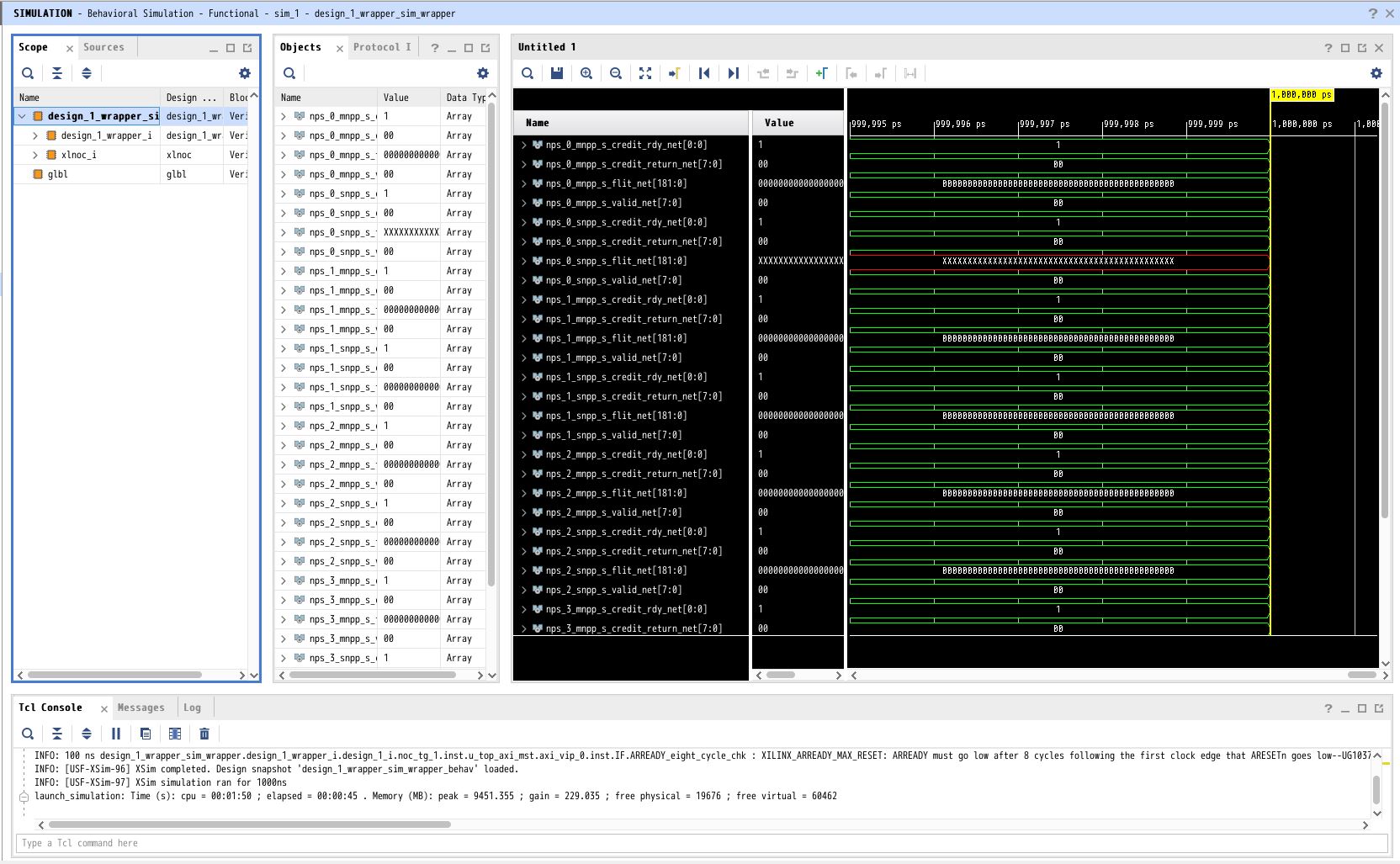

実行するとSimulationが開始され、以下のような画面に切り替わります。

出典:Vivado® ML Edition

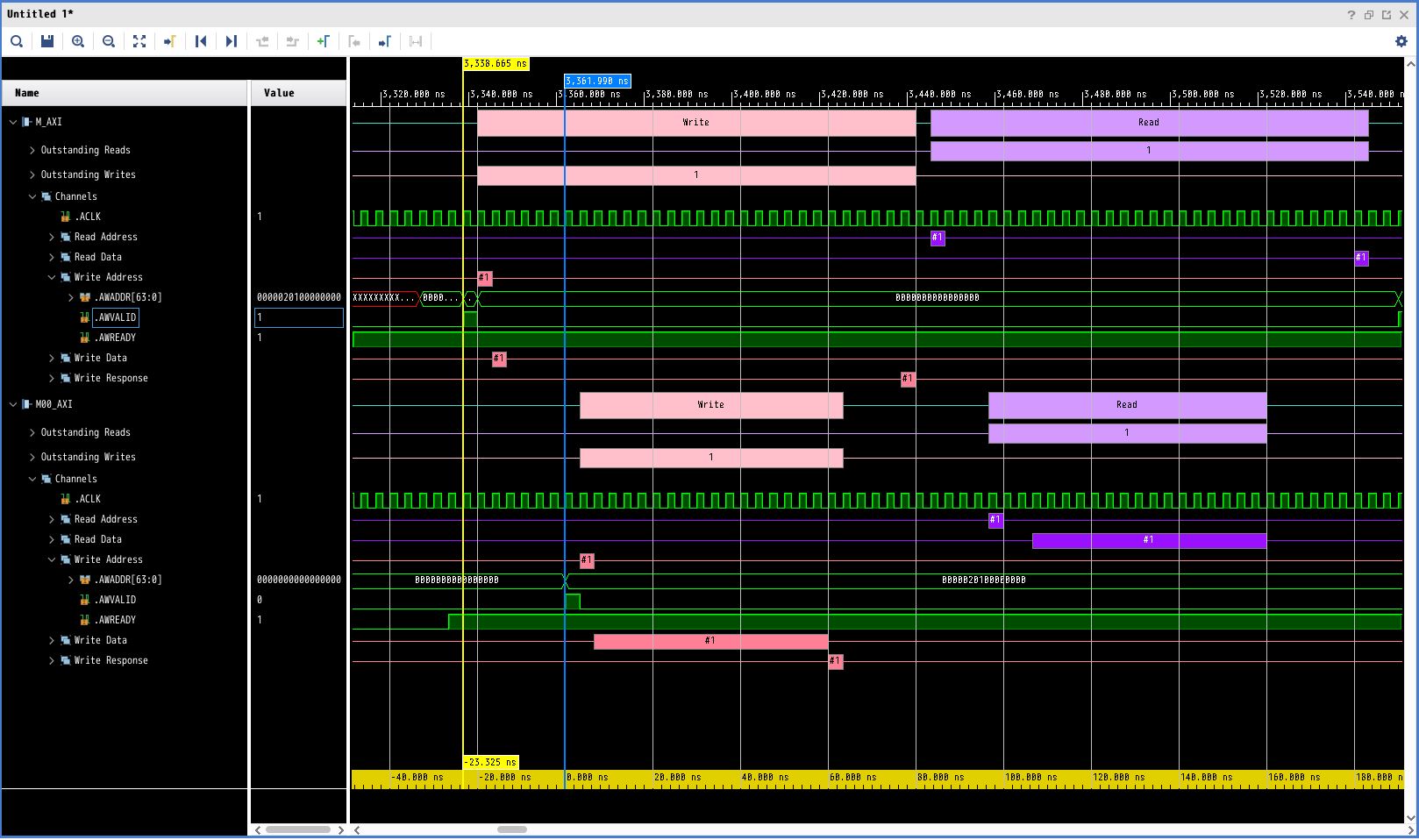

今回は、axi_noc_0のM00_AXIとnoc_tgのM_AXIを追加し、Run ALLを実行します。

出典:Vivado® ML Edition

このように、追加の設定を行わずにTraffic GneratorのAXIマスタからの書き込み要求がNoCスレーブ側に発生するまでのレイテンシを確認することができました。

他の設定の時のレイテンシについても知りたい方は 前回記事を参考に環境を用意していただき、是非確認してみてください。

NoC内部は、約1GHzで動作するため[1]、DDRなどの高速デバイスに対してデータ転送レートでボトルネックになりにくく、NoCのレイテンシはデバイスの性能評価するうえで注目のポイントとなっています。

では、Simulationでの確認をより詳細に行うため、デザインについて紹介します。

デザイン紹介

入力パターン

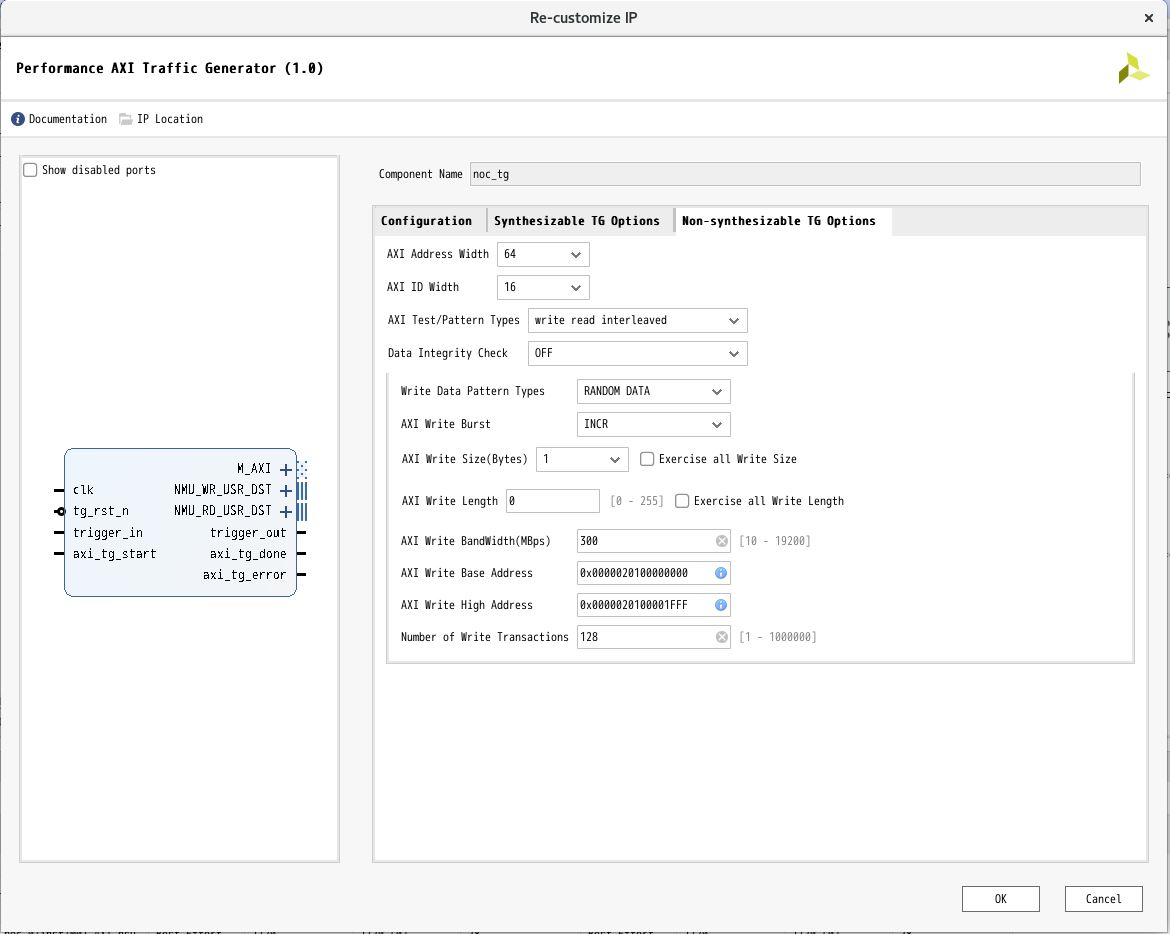

入力パターンは前回の記事で追加したPerformance AXI Traffic Generatorにて生成されています。

入力パターンを変更する際は、このIPをブロックデザイン上で開き、設定を変更します。

出典:Vivado® ML Edition

クロック系、リセット系

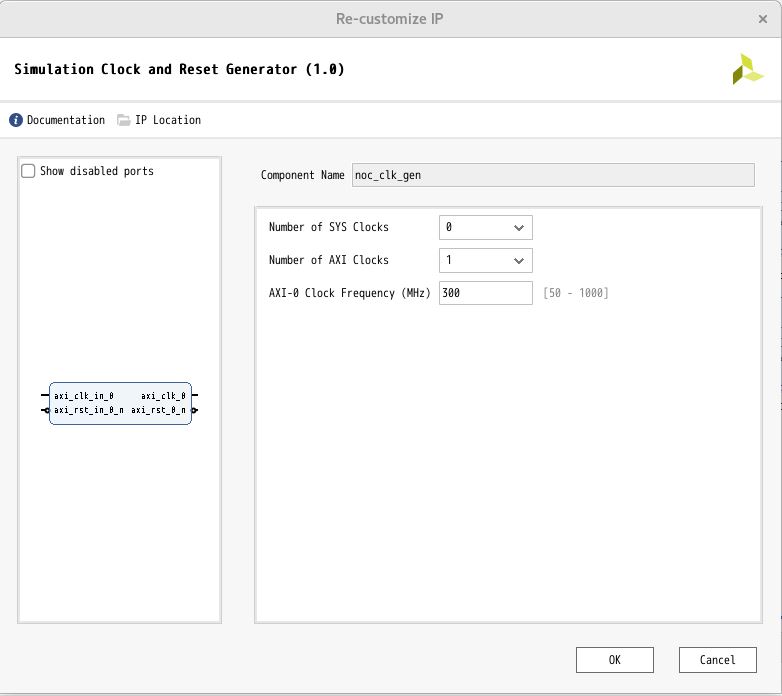

各IPのクロックおよびリセットはブロックデザイン内の、Simulation Clock and Reset Generatorにて生成されます。

こちらのIPによって、テストベンチなどでクロック系、リセット系の定義を行わずとも自動生成されます。

出典:Vivado® ML Edition

このIPはRun Block Automationの過程で自動生成および設定されます。

そのほかの設定

DDRを使用する際は、NoCにて設定を行う必要があります。

今回のデザインでは使用していないため割愛しますが、DDRのパフォーマンスを発揮するには、NoCの設定とSimulationの動作確認を十分に行う必要があります。

こちらについては、次回以降のブログで紹介したいと思います。

おわりに

今回は、Simulation実行までの様子とデザイン内のSimulationに関する機能について紹介させていただきました。

次回以降のブログでは、DDRインターフェースを絡めたSimulation環境の構築や、チューニングについて紹介できればと思います。

これからもTECHブログを通じて、わかりやすくお伝えできればと思います。

次回のブログもどうぞよろしくお願いいたします。

調査依頼や、設計検討などありましたら、弊社デザインサービス事業までお気軽にお問い合わせください。

このブログは「FPGA設計ブログ一覧」の

Versal Acap関連のひとつです。

参考文献

[1] Versal™ ACAP Network on Chip and Integrated Memory Controllerhttps://www.xilinx.com/support/documentation/ip_documentation/axi_noc/v1_0/pg313-network-on-chip.pdf