【Versal™ACAP】I2C Example Design Clock切り替え編 Part1【Vivado® ML 2021.2】

皆さん、こんにちは。

今回は、 以前にブログでご紹介したVCK190のI2C Example Design を使って、

ボード上のOSCをI2Cで設定変更してみました。

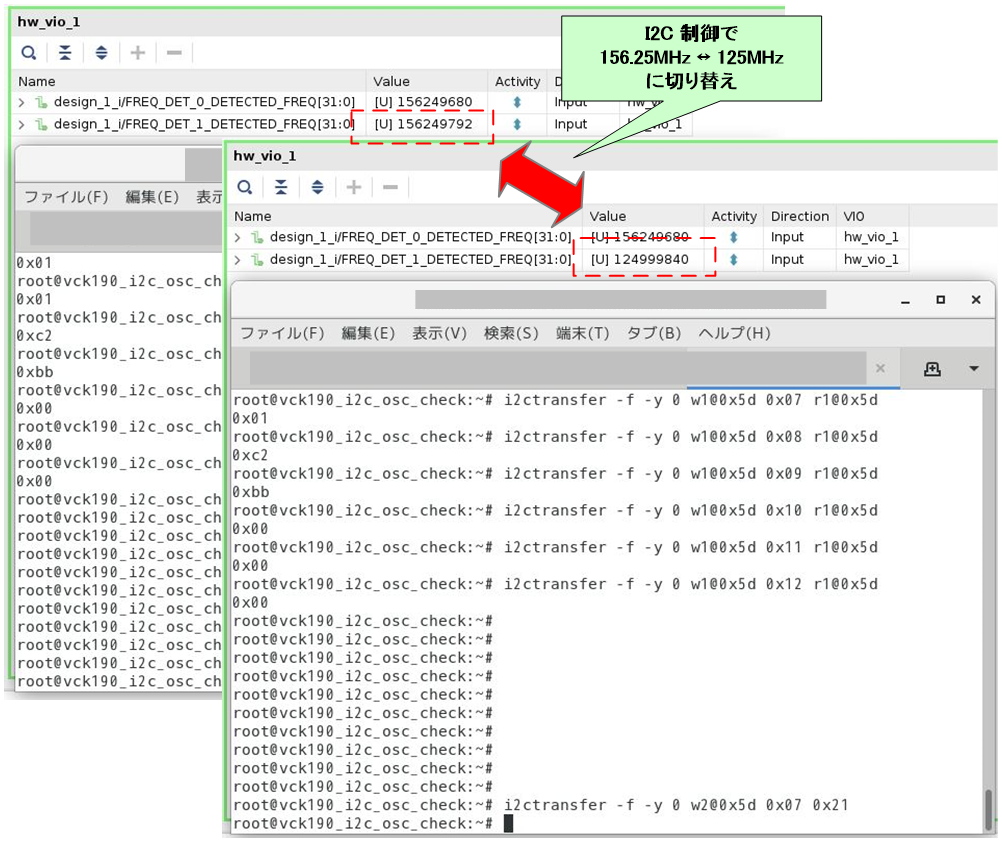

下図のようなI2C制御コマンドで、OSCの周波数が変わる様子をVIOで確認できるまでの過程をまとめましたので紹介します。

第1回の本稿では、デザイン準備でSD Bootイメージ作成まで、

第2回では、実機確認編で周波数切り替わりまでを紹介します。

※画像クリックで大きな画像が表示されます。

出典:Vivado® ML Edition、シリアルコンソール画面

それでは、始めましょう。

このブログは「FPGA設計ブログ一覧」の

Versal Acap関連のひとつです。

目次

今回は、以下の環境で実行します。

- ・HostPC CentOS 7.6

- ・Vivado® ML Edition 2021.2

- ・Petalinux® 2021.2

Vivado® ML Edition

それではデザインを作成します。

以前に紹介したI2C Example Designをベースに作成しているため、今回は途中からとなります。

前回までの内容については、以下リンクから参照ください。

まずは前回作成したI2C Example DesignでLinuxにログインして、I2Cインタフェースを確認します。

# i2cdetect -l

i2c-1 i2c xiix-i2c I2C adapter

i2c-0 i2c Cadence I2C at ff030000 I2C adapter

PL側とPS側に1種類ずつのI2Cインタフェースが確認できます。

アドレスの読み取りや、VCK190の回路図 [1]などを参考にして各デバイスの関係性が見えてきました。

i2c-1:PLのBank406 L18,K17ピンに繋がるI2Cインタフェース。

i2c-0:PSのI2C1,PMC MIO 44,45に繋がるI2Cインタフェース。

i2c-0は、回路図上ではI2C1と表記されているので混乱しますが、PS MIO 46,47のI2C0はi2c_pmcとして使用しているので、i2c detectでは検出されないようです。

次に今回変更を加えるVCK190上のOSCを決めます。

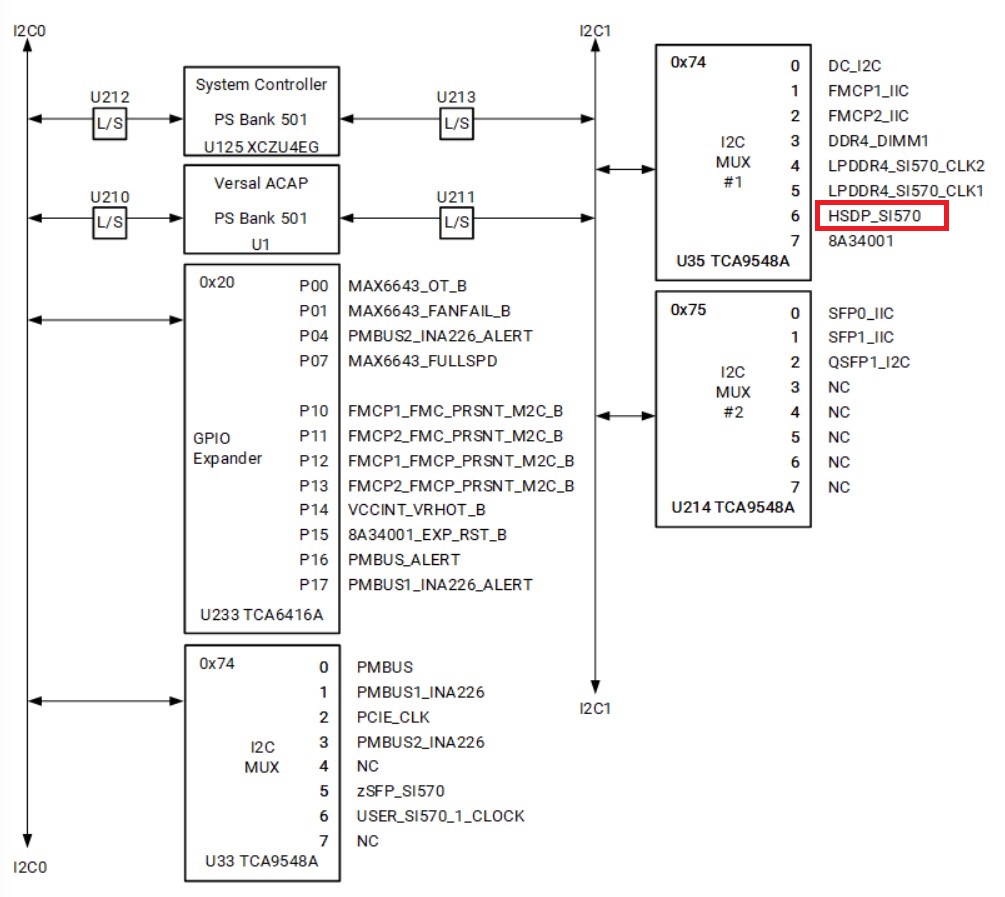

VCK190のユーザーガイド [2]を参考にして、PS_I2C1の接続先を確認します。

今回は、I2C MUX #1の7番目にある「HSDP_SI570」の周波数を変更してみます。

※画像クリックで大きな画像が表示されます。

出典:Xilinx VCK190評価ボード ユーザーガイド(UG1366)

i2cインタフェースが確認できたので、次にVivado® ML Editionを開きデザインに変更を加えます。

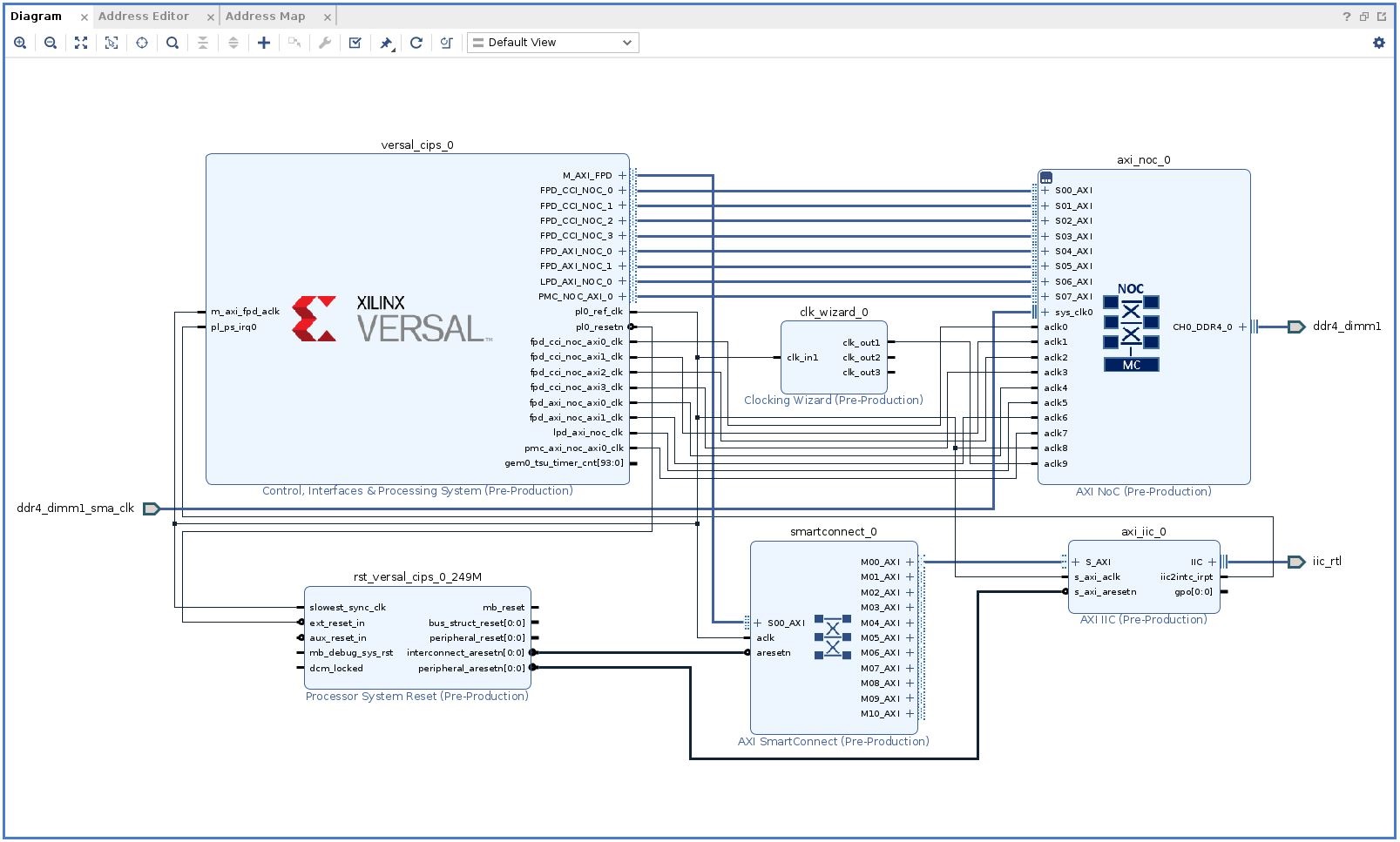

まずは前回記事で作成したデザインを開きます。

※画像クリックで大きな画像が表示されます。

出典:Vivado® ML Edition

PL側のI2Cインタフェースは不要なので、smartconnectとaxi_i2c、 Processor_System_Resetは削除します。

次に、周波数変更したことを確認するためにモニタリング用のClockを追加します。

今回はI2CでHSDP_SI570の設定を変更するため、まずモニタするのはBank105のGTY_REFCLK1になります。

あわせて、比較用に同BankのGTY_REFCLK0もモニタします。

今回、GTY_REFCLK1のピンを参照するため回路図 [1]を参照しましたが、確認の際には、以下のリンクからXTP610のダウンロードが必要です。

※ダウンロードにはアカウント登録が必要となります。

https://japan.xilinx.com/products/boards-and-kits/vck190.html

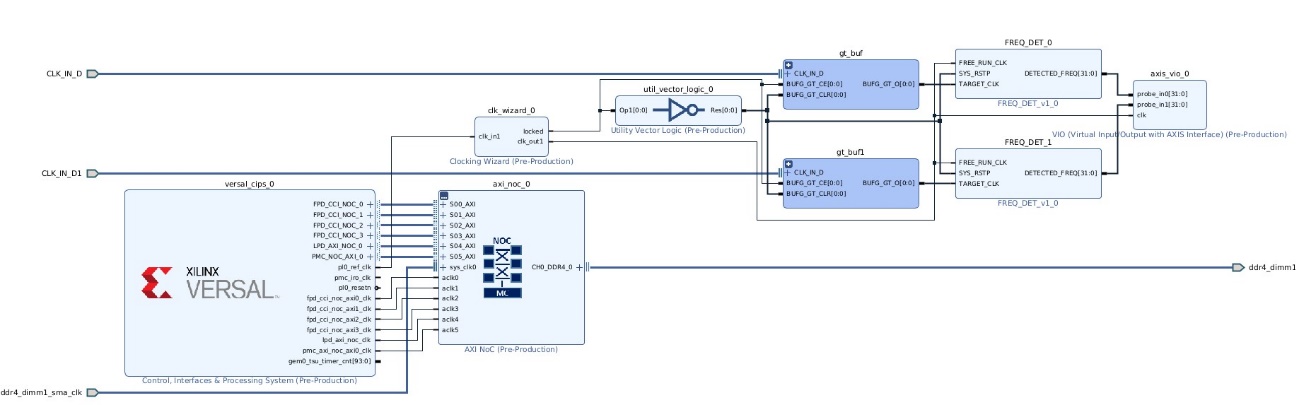

GTのClockを入力するためにBUFG(Utility Buffer IBUFDSGTEとBUFG GT)、 Clockモニタ用にモニタリングIP(Original)とVIO(32bit)、 モニタ用基準Clock生成用にClk_wiz(50MHz,locked)を追加します。

Clockモニタ用のIPは機会があれば紹介しますが、周波数測定はオシロスコープなど代用できるため今回は割愛します。

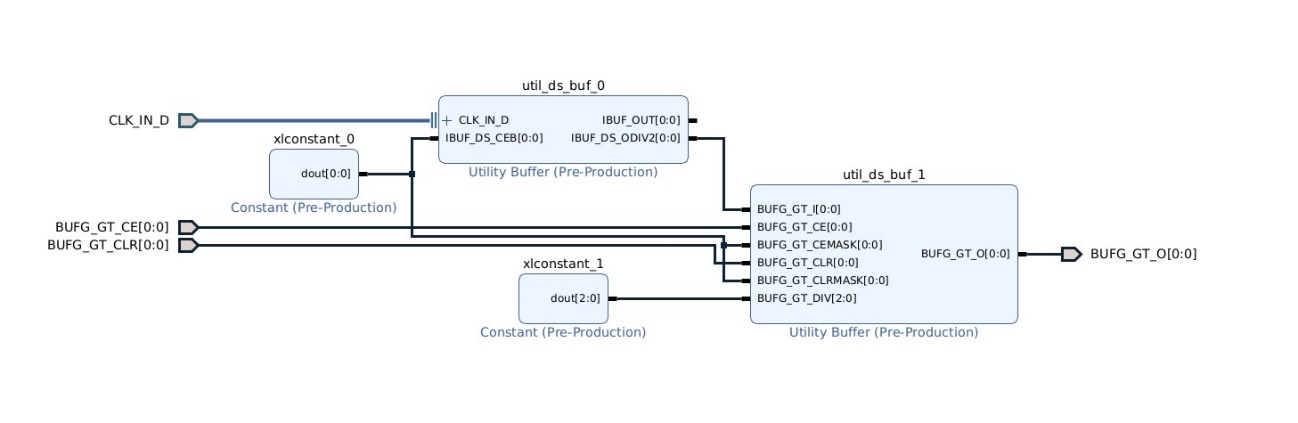

各々を接続し、下図のような構成となりました。

2枚目はgt_bufの構成、Constantは0です。

※画像クリックで大きな画像が表示されます。

出典:Vivado® ML Edition

※画像クリックで大きな画像が表示されます。

出典:Vivado® ML Edition

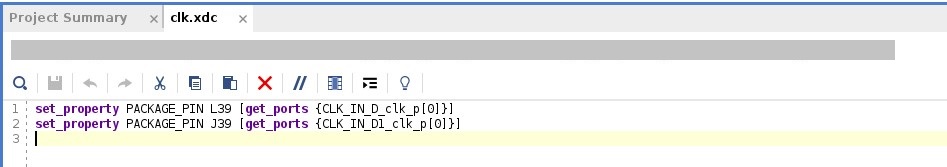

xdcファイルに観測するGTピンを割り当てます。

※画像クリックで大きな画像が表示されます。

出典:Vivado® ML Edition

Create HDL Wrapper ⇒ Generate Device Imageと実行します。

完了後、Export Hardwareを実行し、XSAファイルを生成します。

これでVivado® ML Edition側の作業は終了です。

Petalinux

今回は、LinuxでI2C制御を行うため、 前回記事のPetalinux環境をそのまま引用します。

以下コマンドで前回作成したPetalinux Projectに移動します。

$ cd <name_of_project>XSAファイルを更新します。

前回記事でI2Cに関する設定はすでに追加しているため、今回新たに追加する設定はありません。

$ petalinux-config --get-hw-description=<PATH TO XSA>Buildします。

$ petalinux-buildBuild完了後、ブートイメージを作成します。

$ cd ./images/linux

$ petalinux-package --boot --plm --psmfw --uboot --dtb --force

SDにBOOT.BIN, boot.scr, image.ubを移動します。

これでPetalinuxの作業は終了です。

おわりに

今回は、VCK190でI2C Example DesignでClock切り替えを行うためのデザイン準備までについて解説しました。

次回は、実機でI2C制御をLinuxから行い、実際に周波数が切り替わる様子をご紹介します。

また、別インタフェースのExampleデザインについても、ブログを通じてお伝えできればと思いますので、どうぞよろしくお願いいたします。

調査依頼や、設計検討などありましたら、お気軽にお問い合わせください。

このブログは「FPGA設計ブログ一覧」の

Versal Acap関連のひとつです。

最後までお付き合いいただきありがとうございました。

- 参考文献

-

[1]Xilinx XTP610 VCK190 Schematics

- ※

- リンク内のXTP610から回路図データがダウンロードできます。

ダウンロードには、アカウント登録が必要となります。