ネットリスト選択によるILAのデザインへの挿入

AMD ザイリンクス社のVivado® ML Editionは、波形内部の波形を観測できるILA(Integrated Logic Analyzer)をデザインに挿入することができます。

方法は何種類かありますが、今回は合成後にネットリストを選択して挿入する方法を紹介します。

このブログは「FPGA設計ブログ一覧」の

6. 実機評価のひとつです。

目次

ネットリスト選択によるILAの挿入方法

ネットリスト選択によるILAの挿入方法には以下の2種類のやり方があります。

- 合成後(SYNTHESIS)のデザインからネットリストを探して挿入

- デザインにアトリビュートを追加して合成後のデザインから挿入

今回は単純なカウンタロジックのカウンタ値をILAに挿入する方法を紹介します。

32bitの周回カウンタのロジックで「counter」の信号をILAに挿入してみたいと思います。

// Logic

reg [31:0] counter;

always @(posedge CLK or posedge RSTP) begin

if (RSTP) begin

counter <= 32'd0;

end else begin

counter <= counter + 32'd1;

end

end

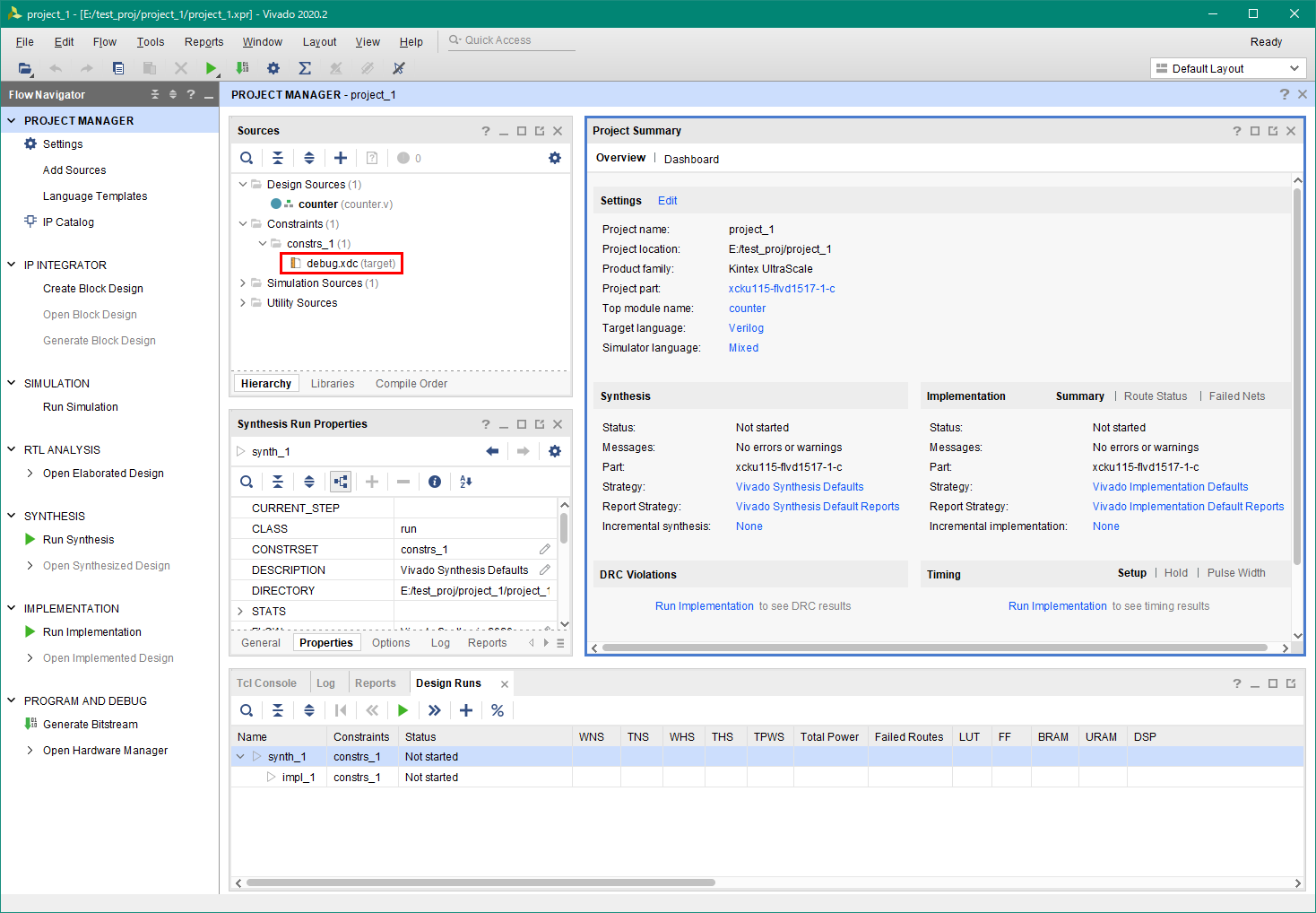

事前準備:デバッグ用のxdcファイルの追加

ILAの情報はxdcファイルに保存されるため、デバッグ用のxdcファイルを1つ用意しておいたほうが便利です。ここでは「debug.xdc」という空のファイルを追加しています。

※画像クリックで大きな画像が表示されます。

(出典:Vivado® ML Edition)

合成後(SYNTHESIS)のデザインから

ネットリストを探して挿入

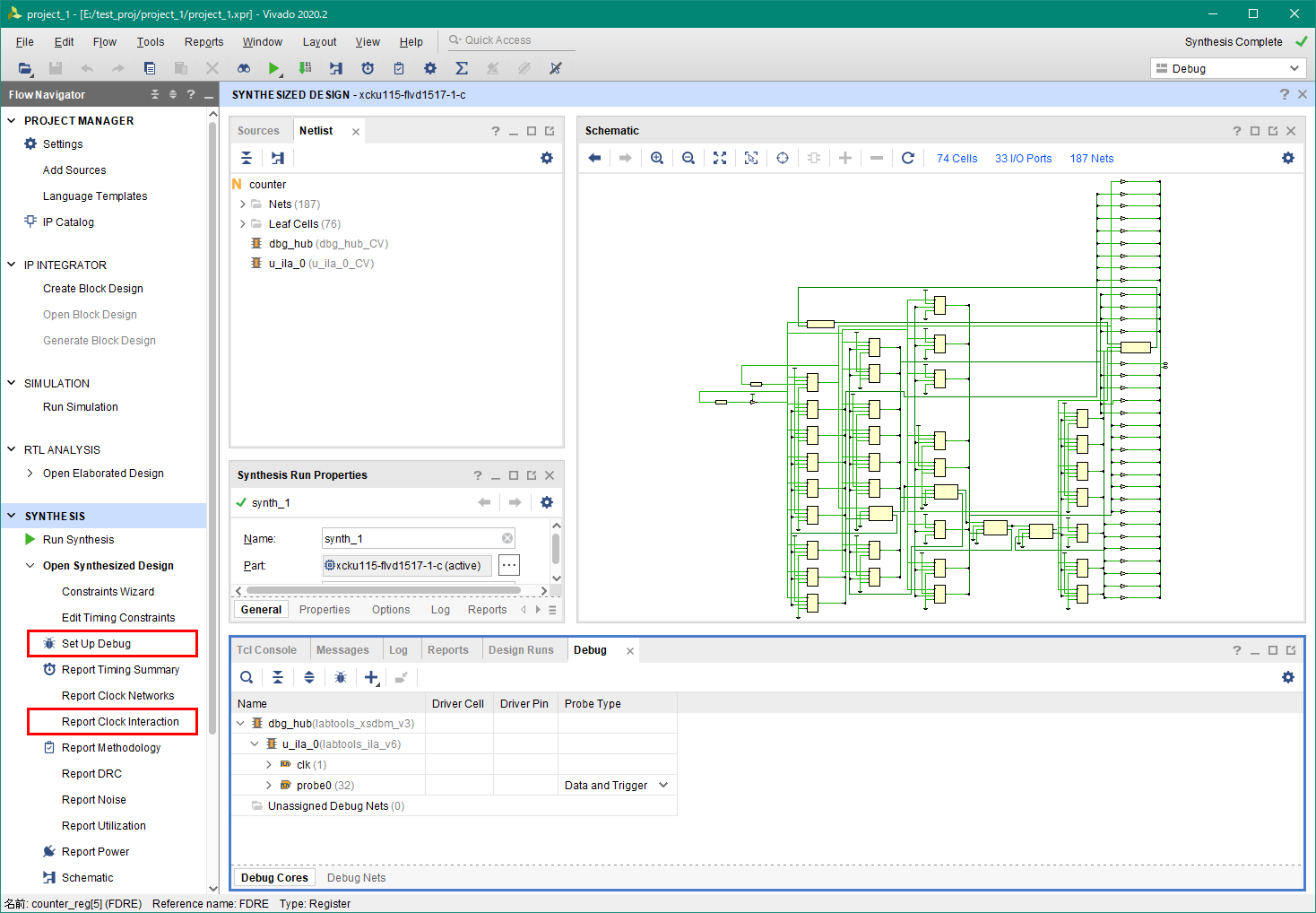

合成後に「Open Synthesized Design」を開き、「Set Up Debug」を選択します。

※画像クリックで大きな画像が表示されます。

(出典:Vivado® ML Edition)

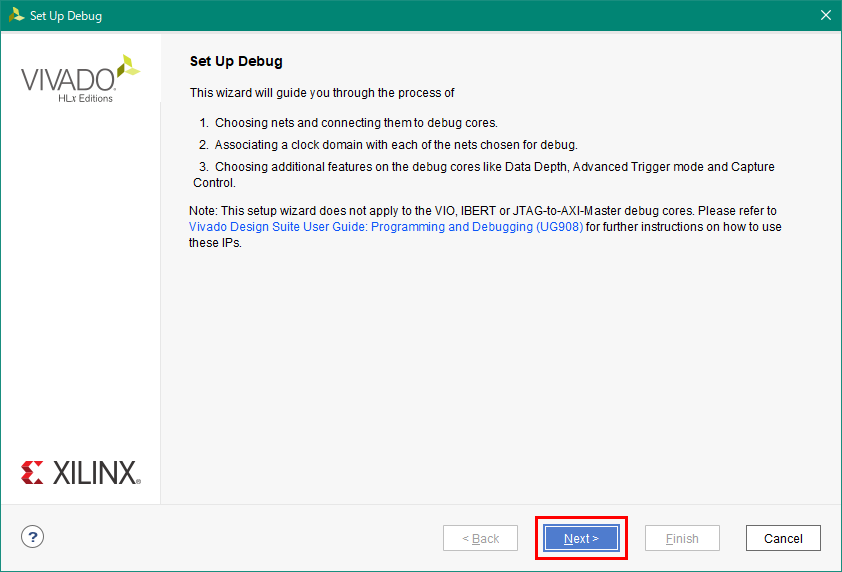

「Set Up Debug」を選択すると以下のウィンドウが表示されるので「Next」を選択します。

※画像クリックで大きな画像が表示されます。

出典:Vivado® ML Edition

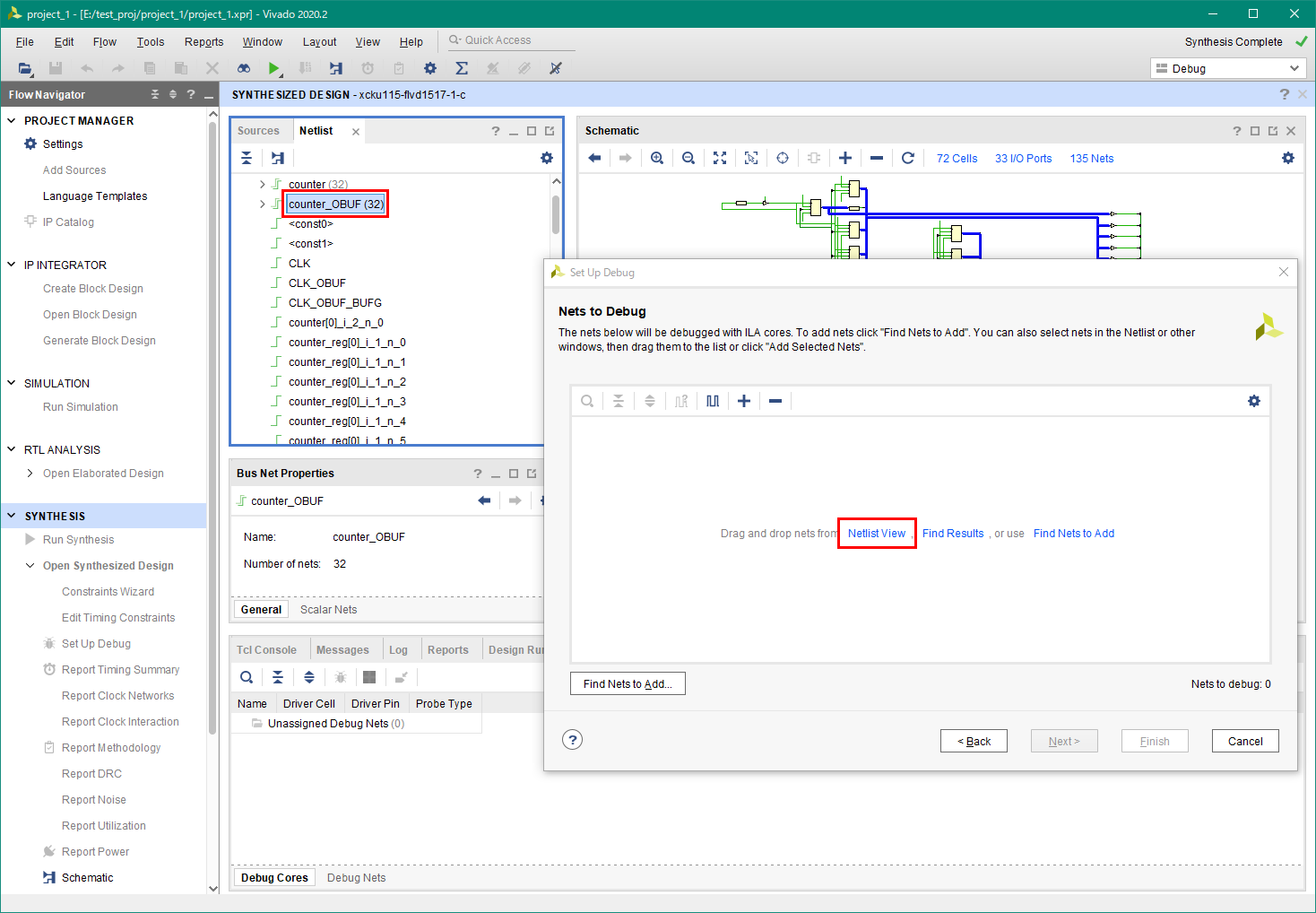

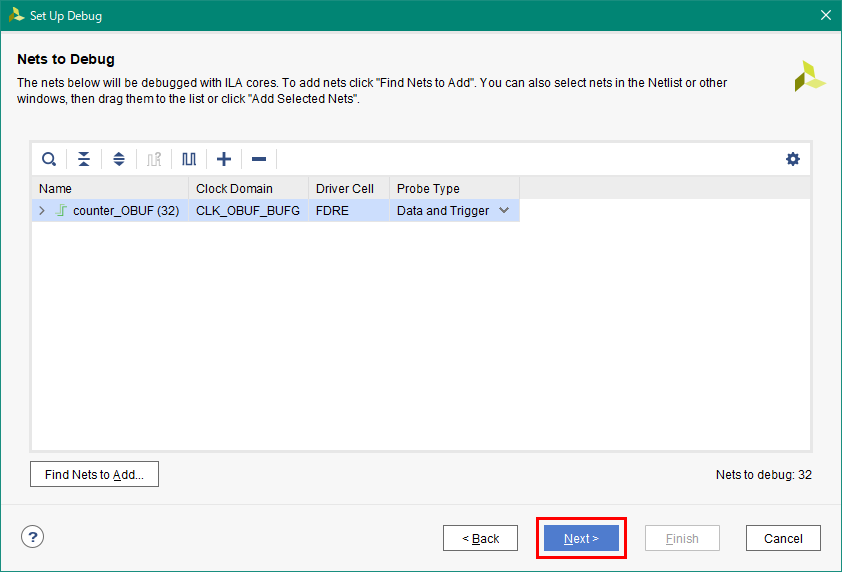

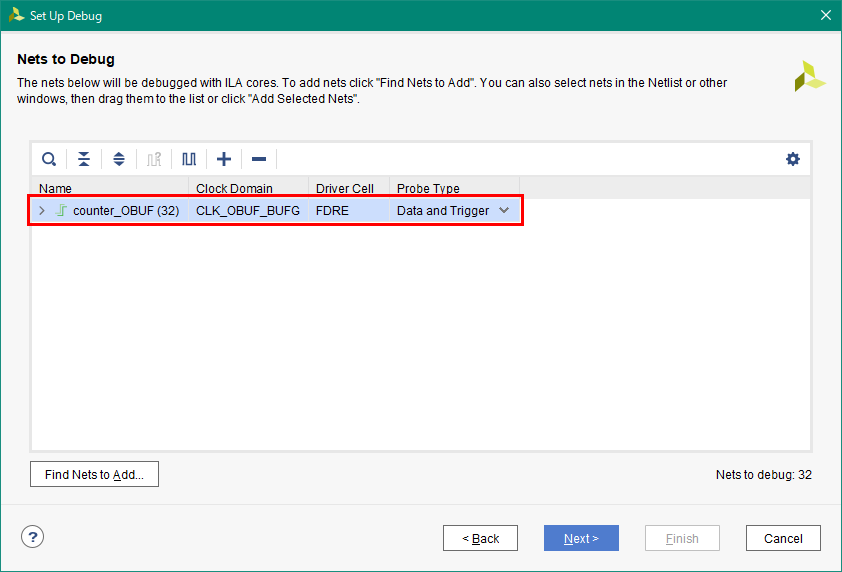

次に「Set Up Debug」ウィンドウが表示されるので、ネットリストから選択する場合には「Netlist View」を選択してVivado® ML Edition 側のNetlistタブから対象となる信号をドラッグアンドドロップすることでILAに信号を追加することができます。

ここではcounter信号をILAに追加したいのでnetから「counter_OBUF」を選択しています。

※画像クリックで大きな画像が表示されます。

(出典:Vivado® ML Edition)

信号が追加されたら「Next」を選択します。

※画像クリックで大きな画像が表示されます。

(出典:Vivado® ML Edition)

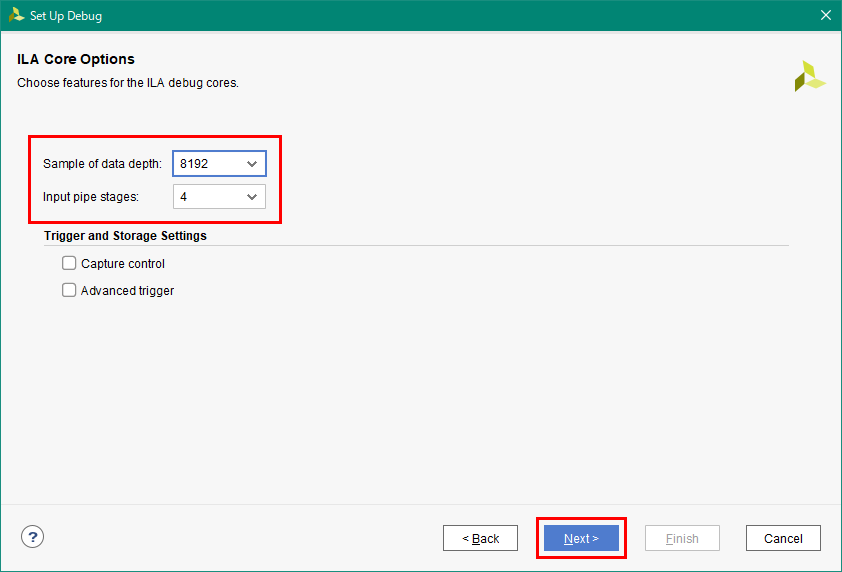

次にILA Coreのオプションを選択します。

・Sample of data depth :

ILAで表示するクロック数(この場合8192クロック分波形表示されます)の波形情報はBlockRAMに格納されるため、波形情報を長くとるにはBlockRAMのリソース量を多く残しておく必要があります。

・Input pipe stages :

ILAの回路ブロックまでに挿入されるパイプラインを指定します。

内部タイミングに影響する項目であるため、多めにとっておいたほうがタイミング制約を満たしやすくなります。ただし本数が多い場合などはF/Fのリソースを消費するため、回路規模が大きくなります。

この設定が終わったら「Next」を選択します。

※画像クリックで大きな画像が表示されます。

(出典:Vivado® ML Edition)

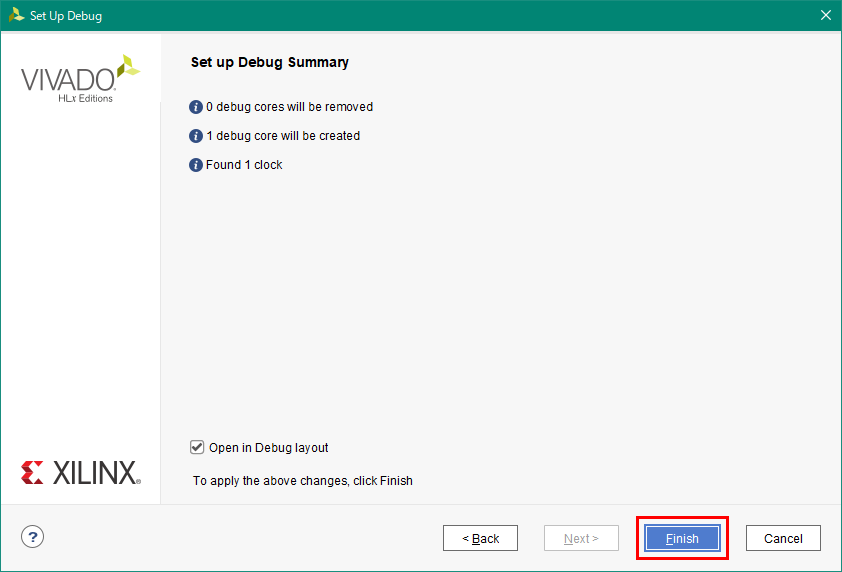

サマリーウィンドウが表示されるので「Next」を選択します。

※画像クリックで大きな画像が表示されます。

(出典:Vivado® ML Edition)

これで信号のILAへの挿入が終わりました。

このあとImplementationを行えば、ILAが挿入されたデザインが完成します。

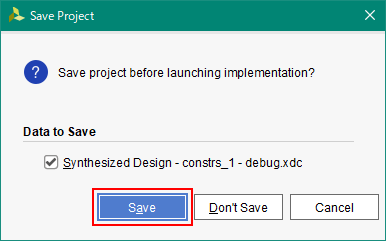

Implementation実行時に以下のような「debug.xdc」に情報をSaveしてもいいかという確認ウィンドウがでますので、「Save」を選択します。

※画像クリックで大きな画像が表示されます。

(出典:Vivado® ML Edition)

デザインにアトリビュートを追加して

合成後のデザインから挿入

Netlistから信号を選択する方法は回路が大規模になると

・目的の信号名を見つけるのが大変

・最適化等で信号名が変わってしまっている

などの、問題がでてきます。

そこで、合成前にRTL上にあらかじめアトリビュートを設定しておくとその信号を自動的に選択してくれるようになります。

ここでは「counter」信号をILAに挿入したいので、その前に

(* mark_debug = "TRUE" *)

とアトリビュートを設定します。

これは複数個設定でき、不要であればILA挿入時にILAに登録せず削除することも可能です。

// Logic

(* mark_debug = "TRUE" *) reg [31:0] counter;

always @(posedge CLK or posedge RSTP) begin

if (RSTP) begin

counter <= 32'd0;

end else begin

counter <= counter + 32'd1;

end

end

これを合成して先ほどと同じようにSet Up Debugを行うと自動的に信号が登録された状態でウィンドウが開きます。

信号が複数ある場合は、複数表示されるので不要であれば右クリックして「Remove Nets」をすればILAには登録されません。

後の作業は同じになります。

※画像クリックで大きな画像が表示されます。

(出典:Vivado® ML Edition)

おわりに

今回はネットリストを選択してILAに挿入する基本的な方法を紹介しました。

この方法でのメリット・デメリットは以下になります。

- メリット

- ・クロックドメインを意識しなくても自動で選択してくれる

・挿入しない場合、回路規模へ影響を与えない

- デメリット

- ・信号を探すのが大変

・合成後に一手間かける必要がある

次回はIPコアを使用したILA/VIOの挿入方法を紹介します。

このブログは「FPGA設計ブログ一覧」の

6. 実機評価のひとつです。

調査依頼や、設計検討などありましたら、お気軽にお問い合わせください。

最後までご覧いただきありがとうございました。