【FPGA検証ノウハウ】Vivado™ロジックアナライザーを便利に使ってみる(Advanced triggerの使い方)~実践編~

皆さん、こんにちは。

実機でFPGAの動作確認を行う場合、Vivado™に搭載されているロジックアナライザーを使うことが多いかと思います。

信号を選んで、値を設定して単純にトリガーをかけるだけならよいのですが、複雑な条件を設定してトリガーをかけたくなることはありませんか?

本ブログでは、ロジックアナライザーを便利にする「Advanced trigger」の使い方を紹介したいと思います。今回は実践編です。

【FPGA検証ノウハウ】Vivado™ロジックアナライザーを便利に使ってみる(Advanced triggerの使い方)~準備・概要編~ 【FPGA検証ノウハウ】Vivado™ロジックアナライザーを便利に使ってみる(Advanced triggerの使い方)~記述編~

それでは、はじめましょう。

このブログは「FPGA設計ブログ一覧」の

6. 実機評価のひとつです。

目次

前提条件

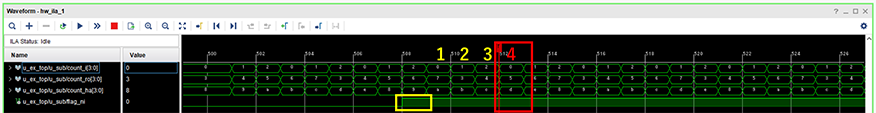

3つのカウンタと1つのフラグ信号があり、次のような動作をします。

| カウンタ「い」 | u_ex_top/u_sub/count_i[3:0]( 0x0 から始まり、0x0~0x2を繰り返す。) |

|---|---|

| カウンタ「ろ」 | u_ex_top/u_sub/count_ro[3:0]( 0x3 から始まり、0x3~0x7を繰り返す。) |

| カウンタ「は」 | u_ex_top/u_sub/count_ha[3:0]( 0x8 から始まり、0x8~0xEを繰り返す。) |

| フラグ「に」 | u_ex_top/u_sub/flag_ni( Low から始まり、途中でHighになる。) |

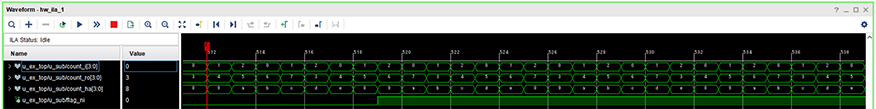

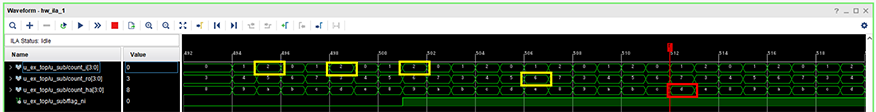

出典:Vivado™ 2020.2.2 Hardware Manager hw_ila_1画面(参照 2023/09/22)

以降、波形に描かれた黄色枠はAdvanced triggerに設定した条件、赤色枠は設定条件且つトリガーが行われた箇所になります。

例① 3つの値が一致

条件

同じタイミングで3つのカウンタの値が一致したらトリガーを実行します。

トリガー設定内容

state ex1_seq1:

if ((u_ex_top/u_sub/count_i == 4'h1) &&

(u_ex_top/u_sub/count_ro == 4'h7) &&

(u_ex_top/u_sub/count_ha == 4'hc)) then

trigger;

else

goto ex1_seq1;

endif実動作

出典:Vivado™ 2020.2.2 Hardware Manager hw_ila_1画面(参照 2023/09/22)

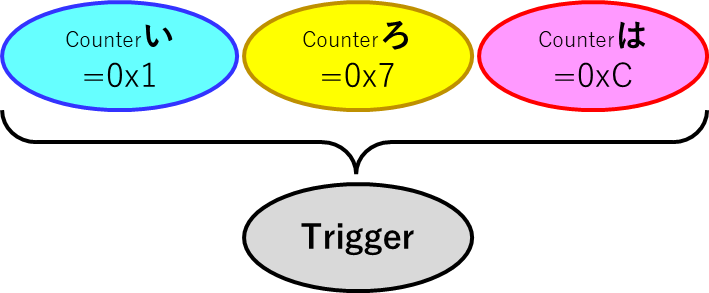

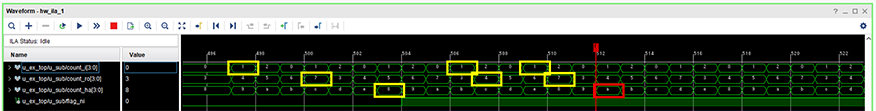

例② 5つの値を順番に待つ

条件

3つのカウンタの値が次の順番で一致したらトリガーを実行します。

トリガー設定内容

state ex2_seq1:

if ((u_ex_top/u_sub/count_i == 4'h2) && ($counter0 == 16'h0002)) then

goto ex2_seq2;

elseif (u_ex_top/u_sub/count_i == 4'h2) then

increment_counter $counter0;

goto ex2_seq1;

else

goto ex2_seq1;

endif

state ex2_seq2:

if (u_ex_top/u_sub/count_ro == 4'h6) then

goto ex2_seq3;

else

goto ex2_seq2;

endif

state ex2_seq3:

if (u_ex_top/u_sub/count_ha == 4'hd) then

trigger;

else

goto ex2_seq3;

endif実動作

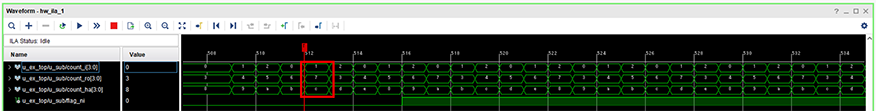

出典:Vivado™ 2020.2.2 Hardware Manager hw_ila_1画面(参照 2023/09/22)

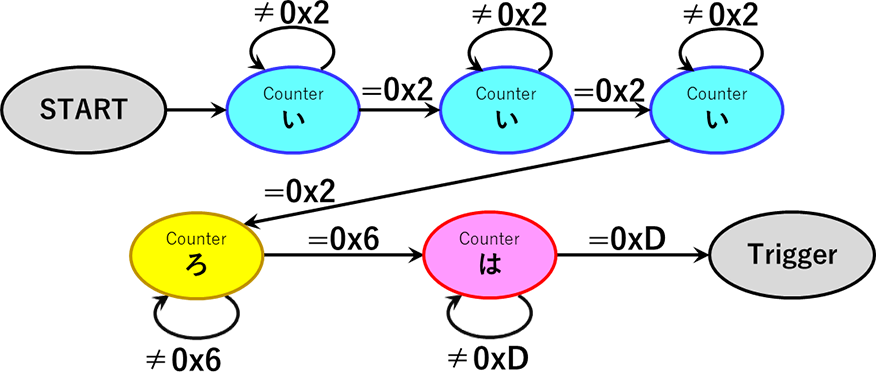

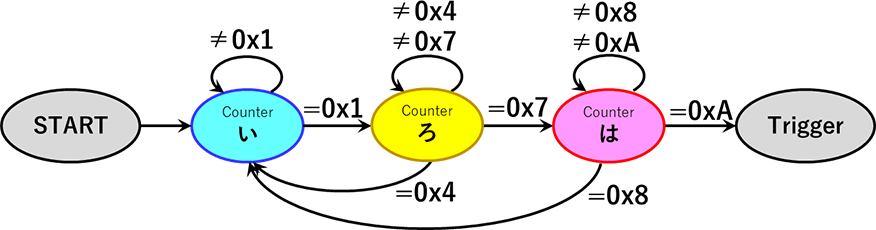

例③ 3つの値を順番に待つが、指定の値があったらやり直し

条件

3つのカウンタの値が次の順番で一致したらトリガーを実行します。

ただし、特定の値が途中にあったら初めからやり直しをします。

トリガー設定内容

state ex3_seq1:

if (u_ex_top/u_sub/count_i == 4'h1) then

goto ex3_seq2;

else

goto ex3_seq1;

endif

state ex3_seq2:

if (u_ex_top/u_sub/count_ro == 4'h7) then

goto ex3_seq3;

elseif (u_ex_top/u_sub/count_ro == 4'h4) then

goto ex3_seq1;

else

goto ex3_seq2;

endif

state ex3_seq3:

if (u_ex_top/u_sub/count_ha == 4'ha) then

trigger;

elseif (u_ex_top/u_sub/count_ha == 4'h8) then

goto ex3_seq1;

else

goto ex3_seq3;

endif実動作

出典:Vivado™ 2020.2.2 Hardware Manager hw_ila_1画面(参照 2023/09/22)

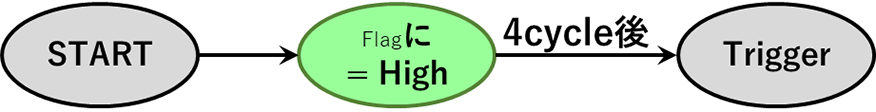

例④ 遅延トリガー

条件

flag_ni = High に遷移してから4サイクル後にトリガーを実行します。

トリガー設定内容

state ex4_seq1:

if (u_ex_top/u_sub/flag_ni == 1'br) then

increment_counter $counter0;

goto ex4_seq2;

else

goto ex4_seq1;

endif

state ex4_seq2:

if ($counter0 == 16'h00_04) then

trigger;

else

increment_counter $counter0;

goto ex4_seq2;

endif実動作

出典:Vivado™ 2020.2.2 Hardware Manager hw_ila_1画面(参照 2023/09/22)

いかがでしたでしょうか。

Advanced trigger を使うと複雑な条件でのトリガーが実行できることをご確認いただけたと思います。

最後までご覧いただきましてありがとうございました!

これからもTECHブログを通じて、皆様の設計にお役立てできればと思います。

次回のブログもどうぞよろしくお願いいたします。

このブログは「FPGA設計ブログ一覧」の

6. 実機評価のひとつです。

弊社ではFPGA設計や回路図設計、レイアウト設計、ソフトウェア設計、筐体設計などを受託開発しています。サービス内容をWEBサイトに掲載していますので、ぜひご覧ください。

FPGAの活用に際して設計検討などありましたら、お気軽にお問い合わせください。