【FPGA検証ノウハウ】Vivado™ロジックアナライザーを便利に使ってみる(Advanced triggerの使い方)~準備・概要編~

皆さん、こんにちは。

実機でFPGAの動作確認を行う場合、Vivado™に搭載されているロジックアナライザーを使うことが多いかと思います。

信号を選んで、値を設定して単純にトリガーをかけるだけならよいのですが、複雑な条件を設定してトリガーをかけたくなることはありませんか?

本ブログでは、ロジックアナライザーを便利にする「Advanced trigger」の使い方を紹介したいと思います。今回は準備・概要編です。

それでは、はじめましょう。

このブログは「FPGA設計ブログ一覧」の

6. 実機評価のひとつです。

目次

準備

まずは、動作確認を行う信号をロジックアナライザー(ILA)で観測する準備を行います。

詳細は、以下の記事を参考にしてください。

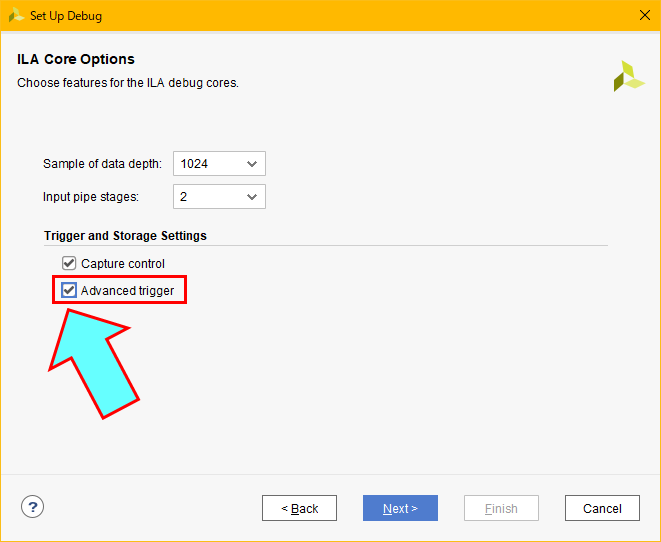

Set up Debug の最後にある「Advanced trigger」にチェックをいれることをお忘れなく!!

出典:Vivado™ 2020.2.2 Set up Debug画面(参照 2023/09/22)

Advanced triggerの文法や記述例

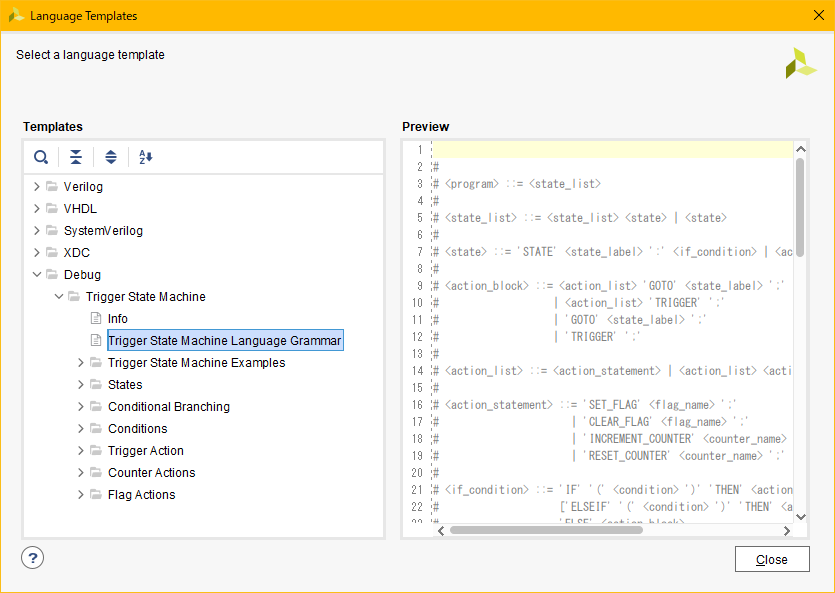

この「Advanced trigger」についてですが、

Vivado™ の Tools -> Language Templatesの Debug -> Trigger State Machine

の中に、文法や記述例があります。ご存じでしたか?

文法の一部

出典:Vivado™ 2020.2.2 Language Templates画面(参照 2023/09/22)

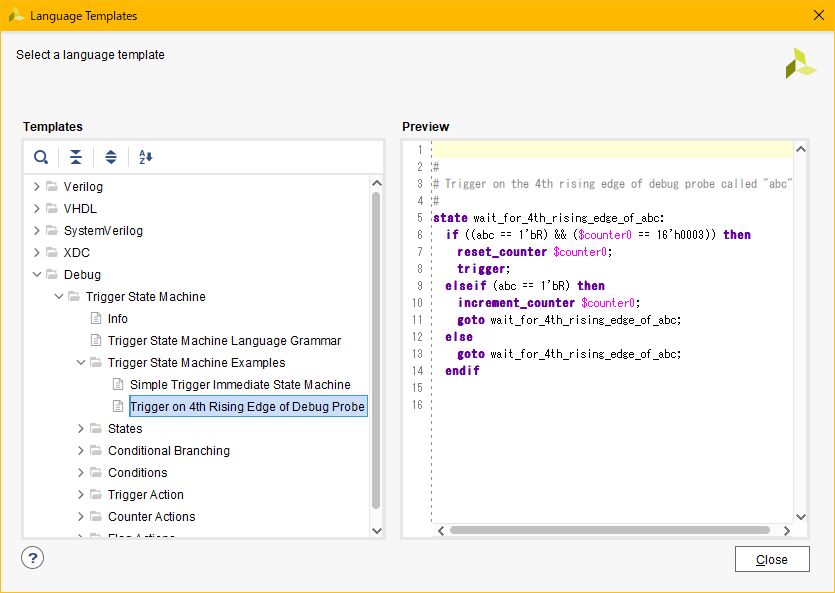

記述例

出典:Vivado™ 2020.2.2 Language Templates画面(参照 2023/09/22)

これ以外に、説明が書かれているのは以下のユーザーガイドとなります。

Vivado Design Suite User Guide: Programming and Debugging (UG908)

Advanced triggerの使い方の流れ

Advanced triggerの使い方は次のような流れになります。

- ①

- ロジックアナライザーに設定した信号を使って、トリガー条件(ステートマシーン)を「.tsm」ファイルに記述します。

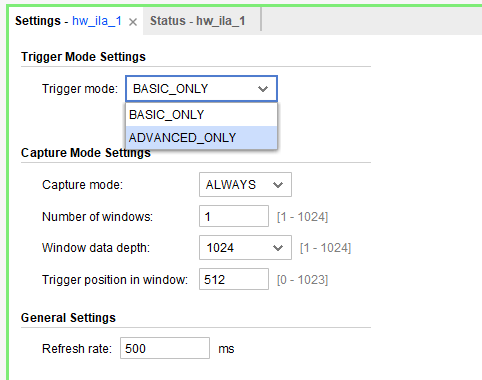

- ②

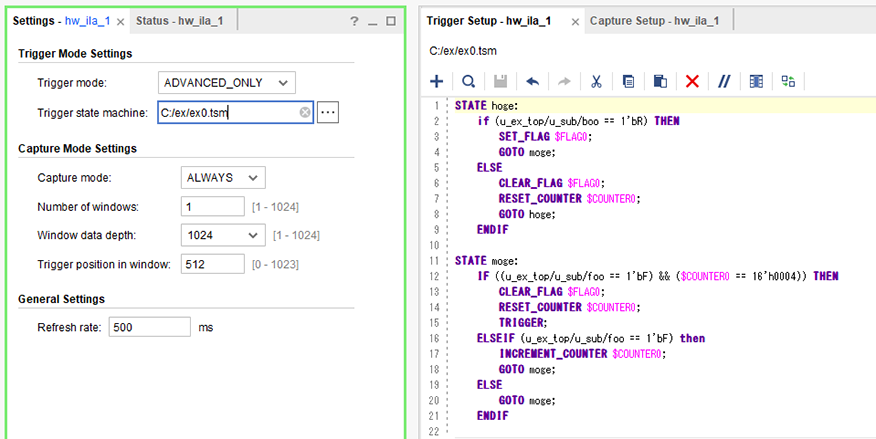

- トリガーモードを「BASIC_ONLY」から「ADVANCED_ONLY」に変更します。

出典:Vivado™ 2020.2.2 Hardware Manager hw_ila_1画面(参照 2023/09/22)

- ③

- トリガー条件を記載した「.tsm」ファイルを指定します。

読み込まれると別のタブにその内容が表示されます。

もしくは、タブに直接条件を書くことも可能です。(保存可能です)

出典:Vivado™ 2020.2.2 Hardware Manager hw_ila_1画面(参照 2023/09/22)

- ④

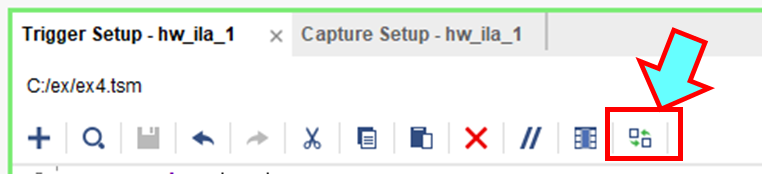

- 読み込んだ(もしくは修正した)トリガー条件をコンパイルします。

出典:Vivado™ 2020.2.2 Hardware Manager hw_ila_1画面(参照 2023/09/22)

- ⑤

- エラーが出た場合は、修正します。

- ⑥

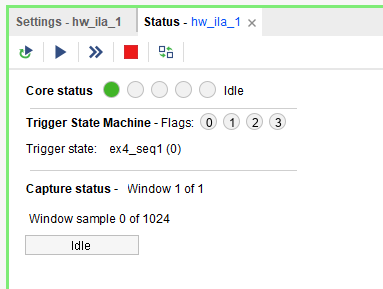

- 準備が整ったらいつも通り「Run trigger」を実行します。

- ※

- 実行中のステートやフラグはStatus の中に表示されます。(遷移が早い場合、目では見えません)

出典:Vivado™ 2020.2.2 Hardware Manager hw_ila_1画面(参照 2023/09/22)

いかがでしたでしょうか。

Advanced triggerの使用までの一連の流れを記載しました。

次回はトリガー条件の書き方を紹介したいと思います。

最後までご覧いただきましてありがとうございました!

これからもブログを通じて、皆様の設計にお役立てできればと思います。

次回のブログもどうぞよろしくお願いいたします。

このブログは「FPGA設計ブログ一覧」の

6. 実機評価のひとつです。

弊社ではFPGA設計や回路図設計、レイアウト設計、ソフトウェア設計、筐体設計などを受託開発しています。サービス内容をWEBサイトに掲載していますので、ぜひご覧ください。

FPGAの活用に際して設計検討などありましたら、お気軽にお問い合わせください。