IPコアによるILA,VIOのデザインへの挿入

AMD ザイリンクス社のVivado® ML Editionは、波形内部の波形を観測できるILA(Integrated Logic Analyzer)とVIO(Virtual Input/Output)をデザインに挿入することができます。

前回はネットリストから選択する方法を紹介しましたので今回はIPコアを使ってILA/VIOを挿入する方法を紹介したいと思います。

このブログは「FPGA設計ブログ一覧」の

6. 実機評価のひとつです。

目次

IPコアによるILAの挿入方法

ILAのIPコアを直接デザインに挿入することで、合成後に手動で挿入しなくてもILAを挿入することが可能です。

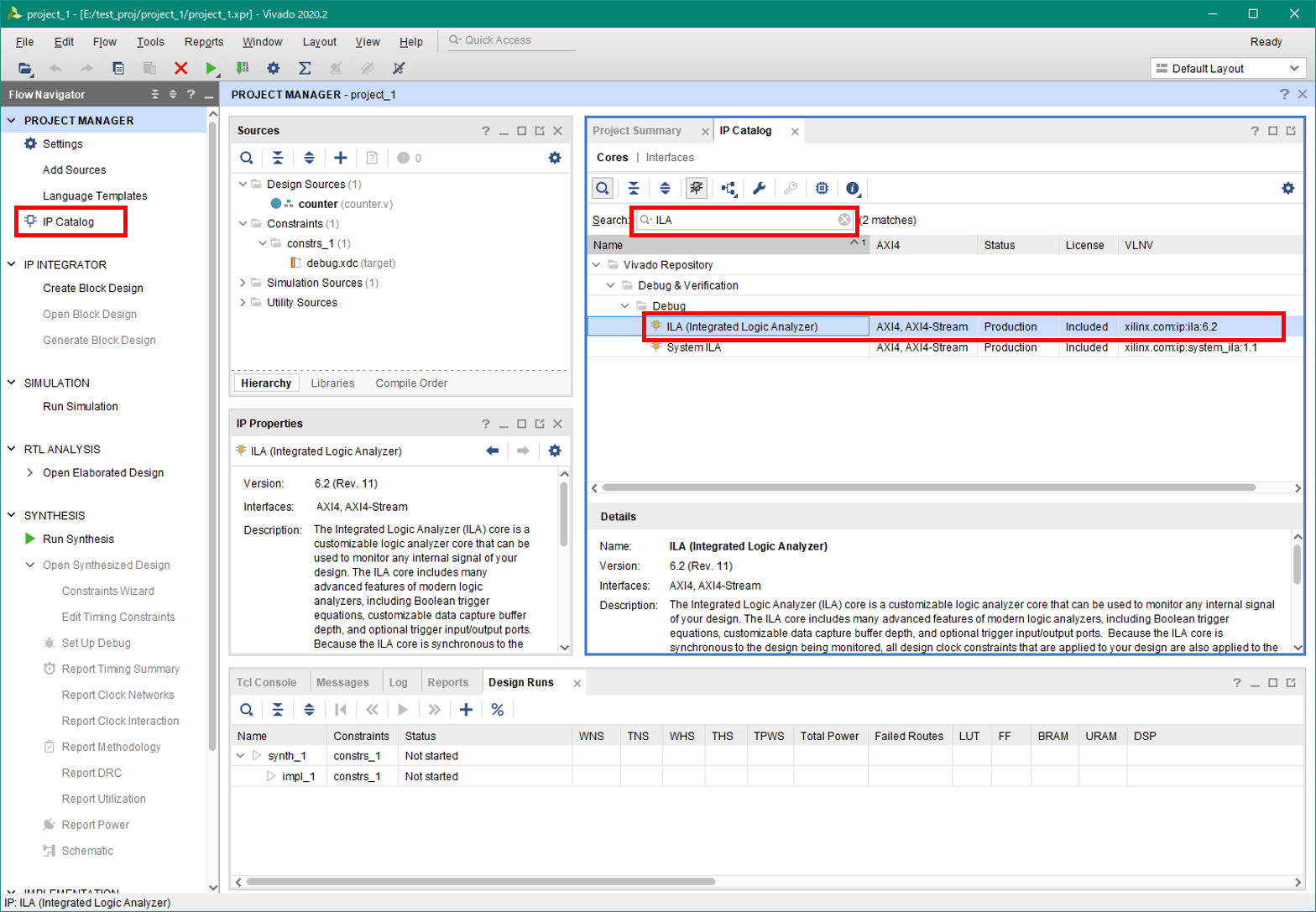

ILAのIPコアを生成するにはVivado® ML Editionの「IP Catalog」からILAで検索をしてILAのコアを選択します。

※画像クリックで大きな画像が表示されます。

(出典:Vivado® ML Edition)

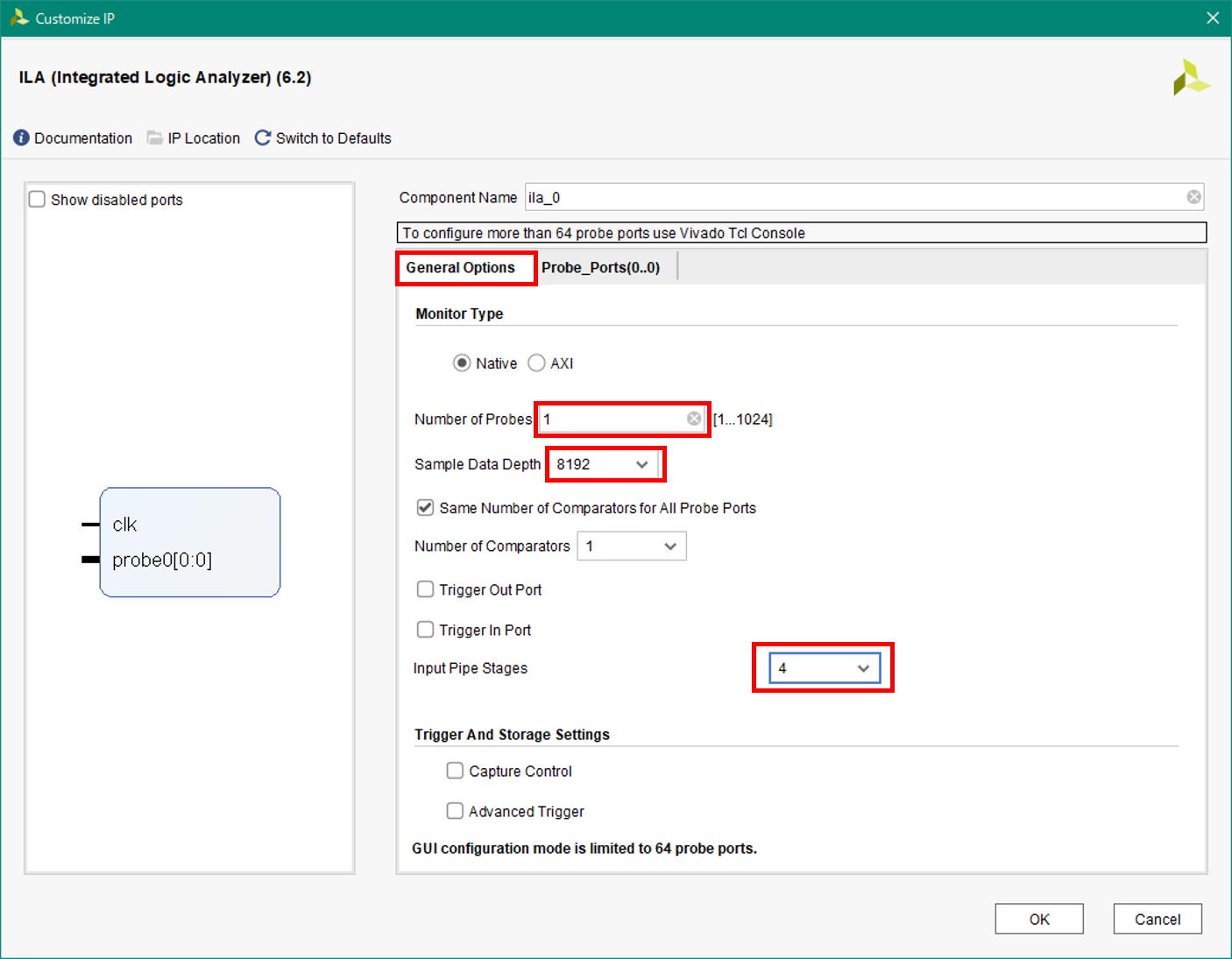

ILAのIPコア生成ウィンドウが表示されますので、今回は基本的な使い方として先ほどと同じCounter信号を挿入するための設定を行います。

General Optionsタブ

Number of Probes :

ILAに挿入したい信号の本数を設定します。(Bit幅ではなく1信号名に対して1個)

ここで注意したいのが、違うクロックドメインの信号を1つのILAに挿入した場合に正常に波形がみられない可能性があるため、違うクロックドメインの信号を見たい場合には複数のILA IPコアを生成が望ましいです。

Sample of data depth :

ILAで表示するクロック数を設定します。

Input pipe stages :

ILAの回路ブロックまでに挿入されるパイプラインを指定します。

※画像クリックで大きな画像が表示されます。

(出典:Vivado® ML Edition)

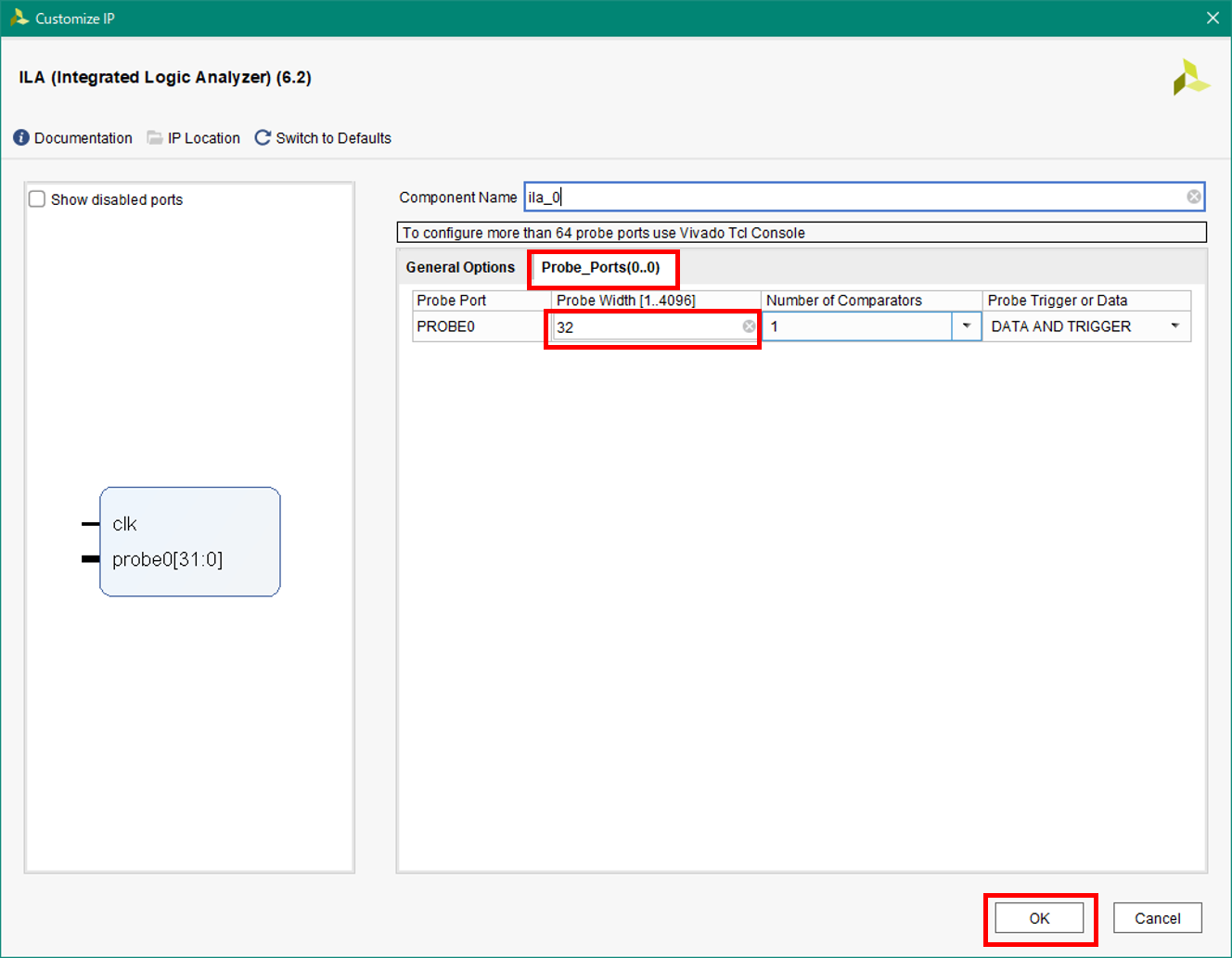

Probe Portsタブ

プローブ1個に対してのBit幅を設定します。

ここではCounter信号に合わせて32bitを設定しています。

設定が終わった「OK」を選択してIPコアを生成します。

※画像クリックで大きな画像が表示されます。

(出典:Vivado® ML Edition)

ILA IPコアをRTL上に記述します。

生成したILA IPコアのインスタンスは以下となりますので、それをベースに信号を設定していきます。

\(project名).gen\sources_1\ip\ila_0\ila_0.veo

ここではサンプリングクロック(CLK)とプローブ信号(counter)を設定しています。

この設定が終わったら、通常と同じようにVivado®でコンパイルすることでILAが挿入されたデザインが生成されます。

// Logic

reg [31:0] counter;

always @(posedge CLK or posedge RSTP) begin

if (RSTP) begin

counter <= 32'd0;

end else begin

counter <= counter + 32'd1;

end

end

ila_0 ila_counter (

.clk (CLK ), // input wire clk

.probe0 (counter ) // input wire [31:0] probe0

);

IPコアによるVIOの挿入方法

デザインへのVIOの挿入は、VIO IPコアを使用する方法のみとなります。

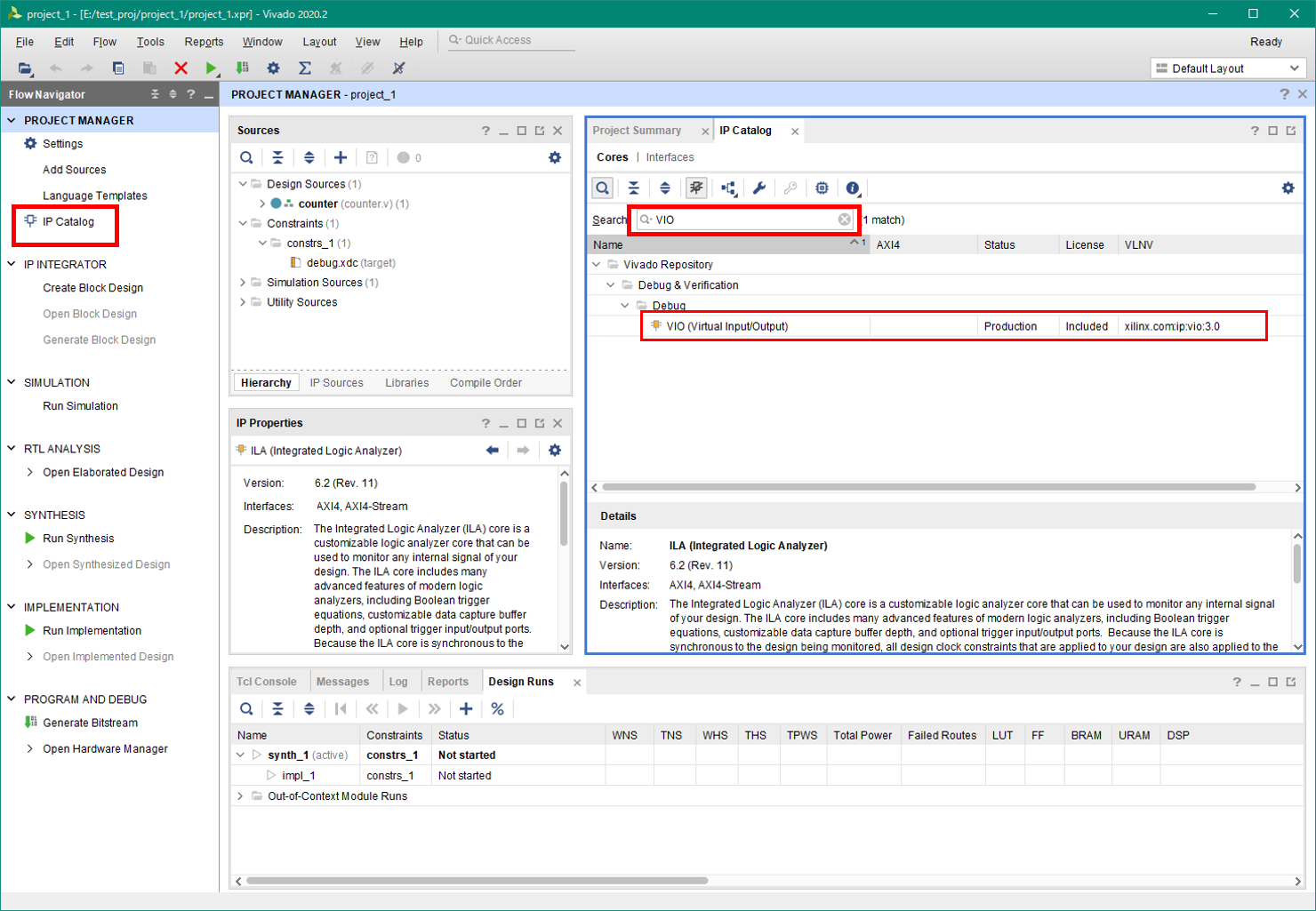

VIOのIPコアを生成するにはVivado®の「IP Catalog」からVIOで検索をしてVIOのコアを選択します。

※画像クリックで大きな画像が表示されます。

(出典:Vivado® ML Edition)

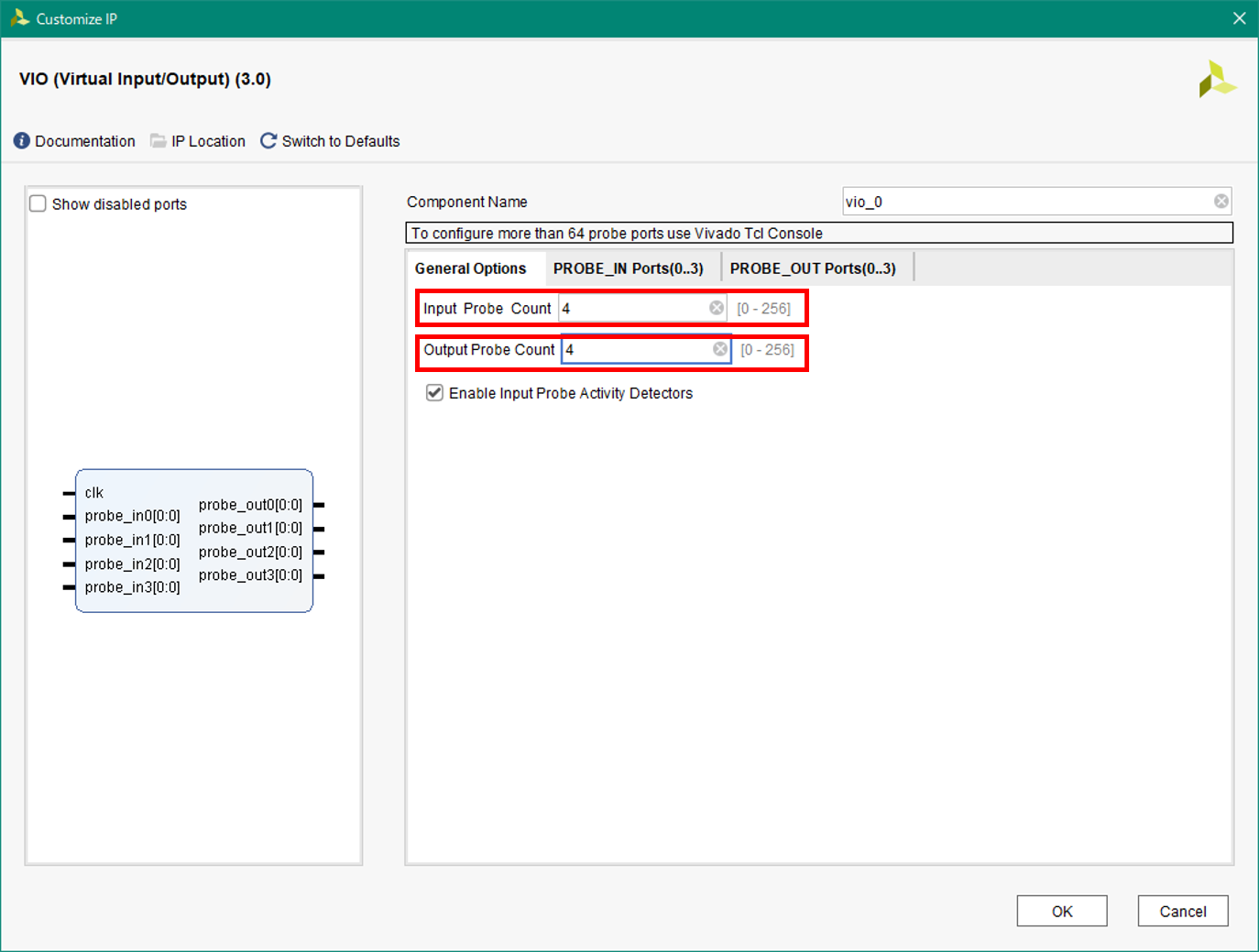

General Optionsタブ

VIOの入力と出力の本数を選択します。(Bit幅ではなく1信号名に対して1個)

ここでは入力4本、出力に4本を選択しています。

※画像クリックで大きな画像が表示されます。

(出典:Vivado® ML Edition)

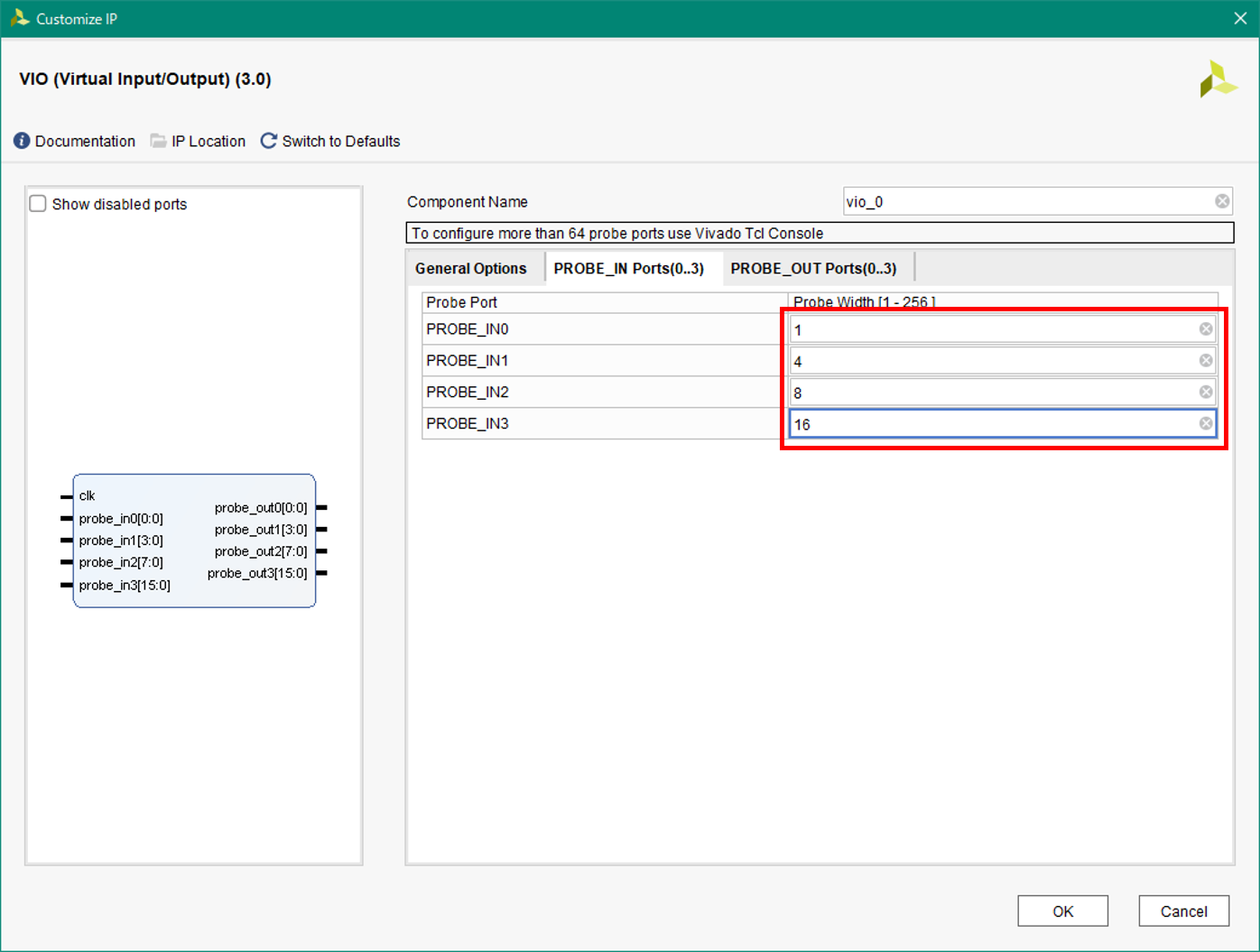

PROBE_IN_Ports

設定された4本の入力プローブに対してBit数を設定できます。

ここでは、1,4,8,16Bitのプローブとしています。

※画像クリックで大きな画像が表示されます。

(出典:Vivado® ML Edition)

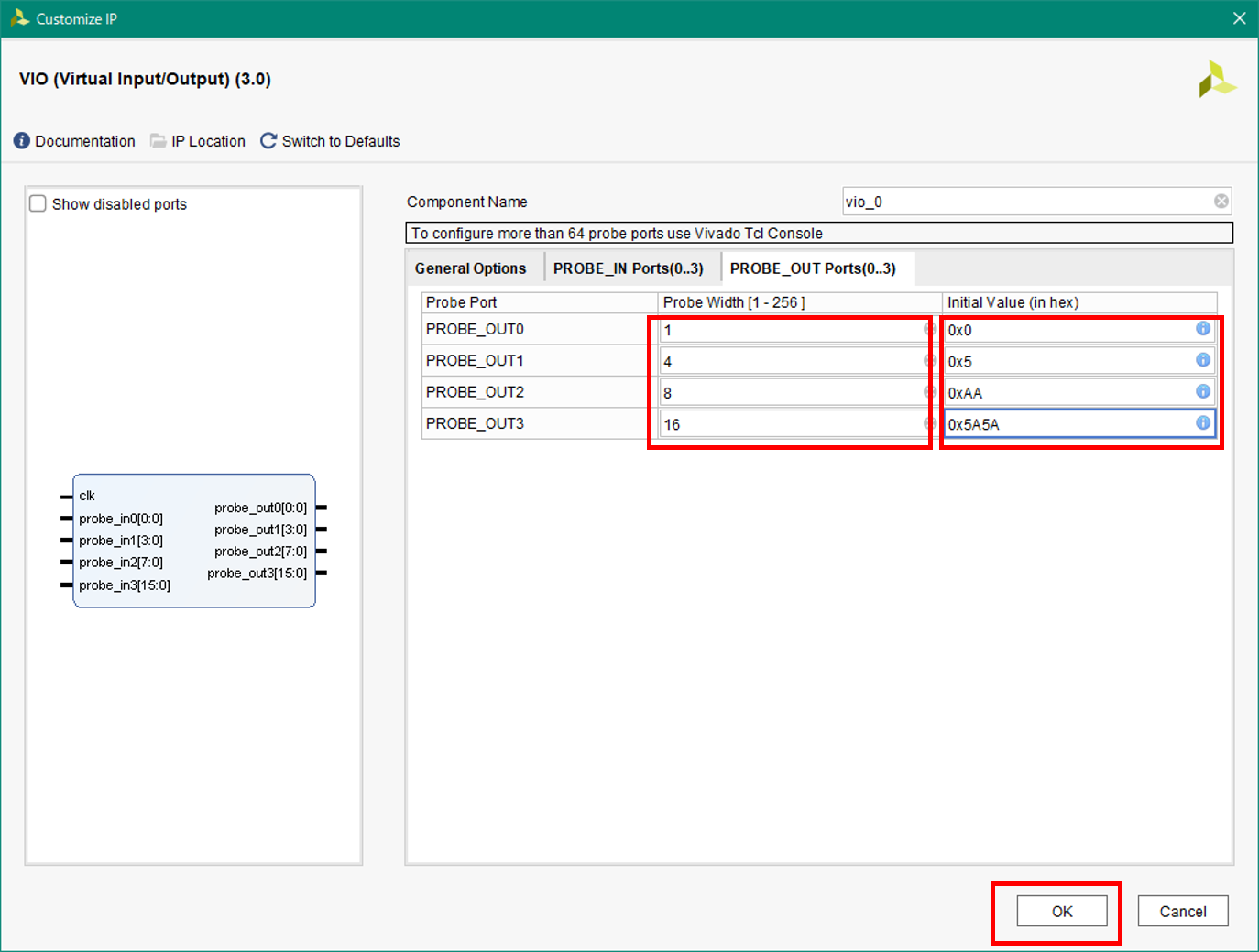

PROBE_OUT_Ports

設定された4本の出力プローブに対してBit数を設定できます。

ここでは、1,4,8,16Bitのプローブとしています。

また出力プローブは初期値を設定可能です。

設定が終わった「OK」を選択してIPコアを生成します。

※画像クリックで大きな画像が表示されます。

(出典:Vivado® ML Edition)

VIO IPコアをRTL上に記述します。

生成したVIO IPコアのインスタンスは以下となりますので、それをベースに信号を設定していきます。

\(project名).gen\sources_1\ip\vio_0\vio_0.veo

VIOは以下のように記述され入力と出力の各4本があり、ここに必要な信号を接続することで入力信号の状態と信号の出力が可能になります。

注意点はクロックを指定する必要があるということです。出力信号はこのクロックに同期して出力されます。

vio_0 your_instance_name (

.clk (clk ), // input wire clk

.probe_in0 (probe_in0 ), // input wire [0 : 0] probe_in0

.probe_in1 (probe_in1 ), // input wire [3 : 0] probe_in1

.probe_in2 (probe_in2 ), // input wire [7 : 0] probe_in2

.probe_in3 (probe_in3 ), // input wire [15: 0] probe_in3

.probe_out0 (probe_out0), // output wire [0 : 0] probe_out0

.probe_out1 (probe_out1), // output wire [3 : 0] probe_out1

.probe_out2 (probe_out2), // output wire [7 : 0] probe_out2

.probe_out3 (probe_out3) // output wire [15: 0] probe_out3

);

おわりに

いかがでしたでしょうか。

AMD ザイリンクス社のVivado® ML Editionが波形内部の波形を観測できるILA(Integrated Logic Analyzer)とVIO(Virtual Input/Output)をデザインに挿入する様子をお届けしました。

このブログは「FPGA設計ブログ一覧」の

6. 実機評価のひとつです。

弊社でのお受けしている開発の内容や開発体制、開発分野などについて、以下ページに記載していますので、ご興味がありましたらご覧ください。

https://www.paltek.co.jp/design/odm/index.html

調査依頼や、設計検討などありましたら、お気軽にお問い合わせください。

最後までご覧いただきありがとうございました。