【Vivado®で使用するXDCファイルの基本的な記述例】第4回 Vivado®からみるXDCファイルの優先度、省略できる記述

このブログでは、Vivado® ML EditionsおよびVivado® design Suite(以下「Vivado」といいます)で使用する、「XDCファイル」の基本的な記述について解説します。

XDCとは、Xilinx Design Constraint(頭文字)の略です。

XDCファイルは、AMD ザイリンクス社のFPGAおよび適応型SoCに対して制約を与えることができるファイルで、以下の項目で制約設定が可能です。

- ・端子配置設定

- ・クロック設定

- ・コンフィグレーション設定

- ・タイミング設定 など

本ブログシリーズでXDC制約の基本的な記述について述べてきました。

今回は、補足として、Vivado® ML Edition からみるXDCファイルの優先度、省略できる記述などについて説明します。

このブログは「FPGA設計ブログ一覧」の

4. インプリメント(配置配線)のひとつです。

目次

XDCファイルの読み込み

XDCは以下のような特徴があります。

・TCL構文に従ったコマンドである

・他のTCLコマンド同様に、Vivado® ML Edition で解析できる

Vivado® ML Editionでは、複数のXDCファイルを読み込むことが可能です。

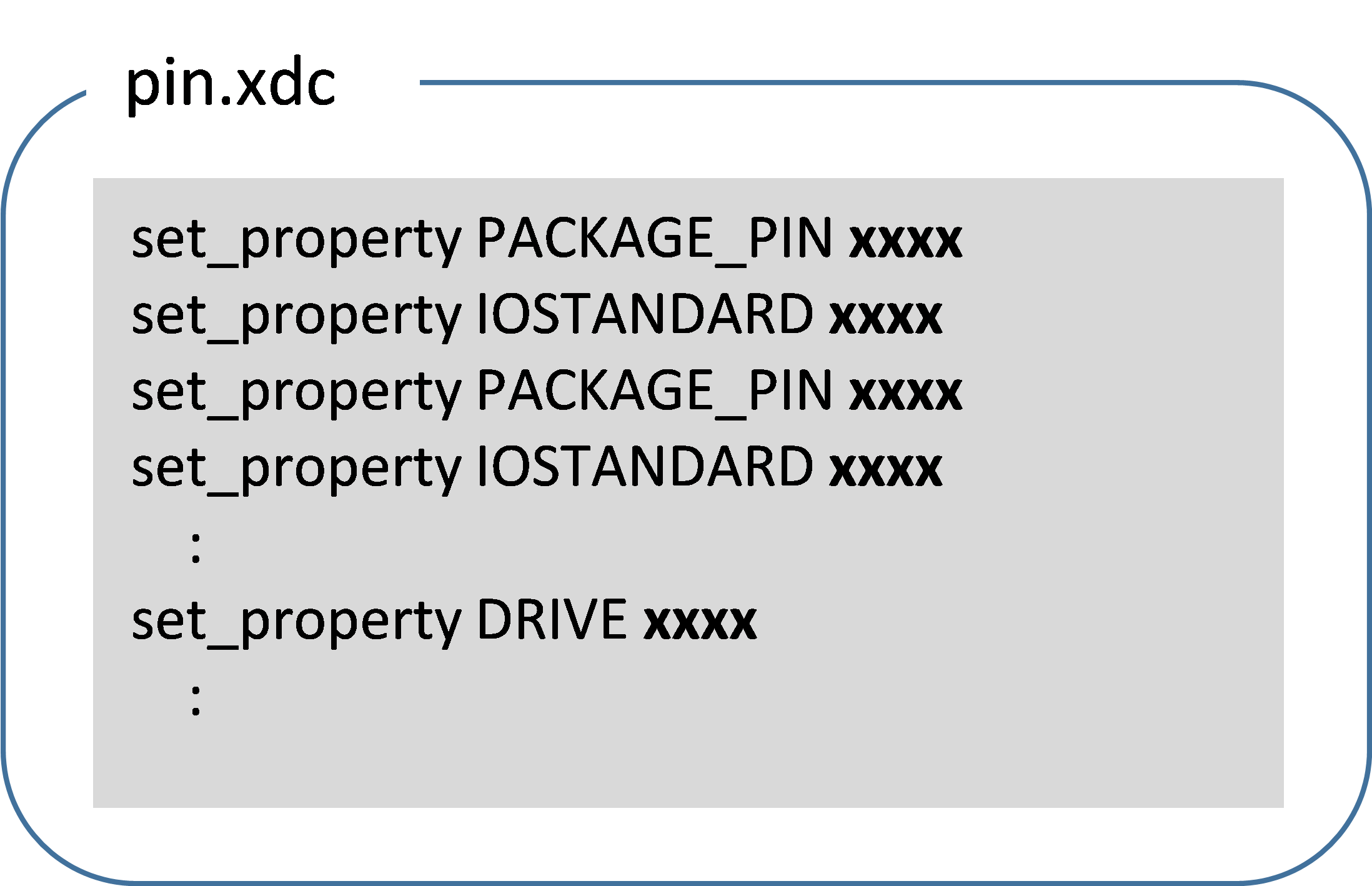

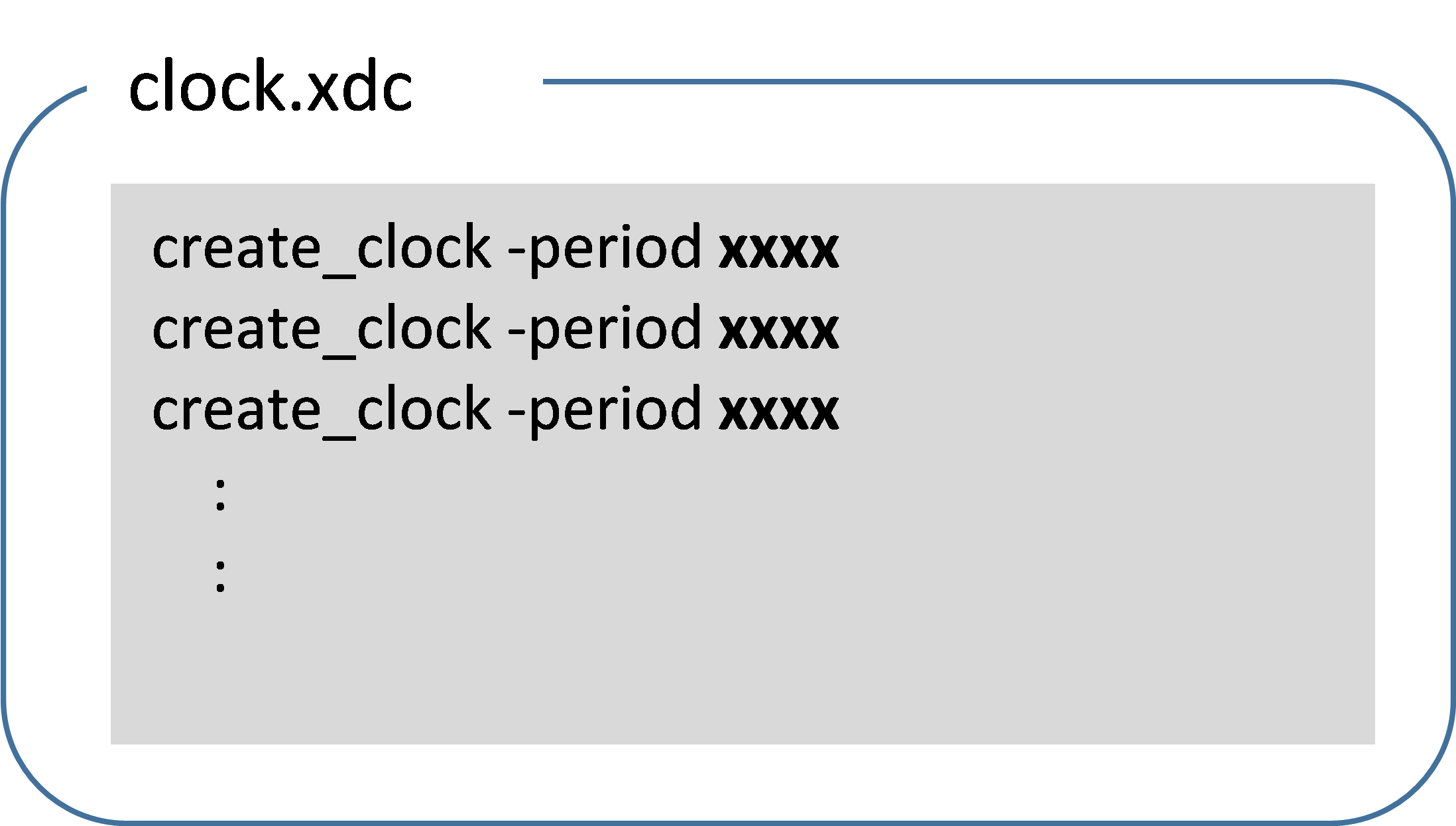

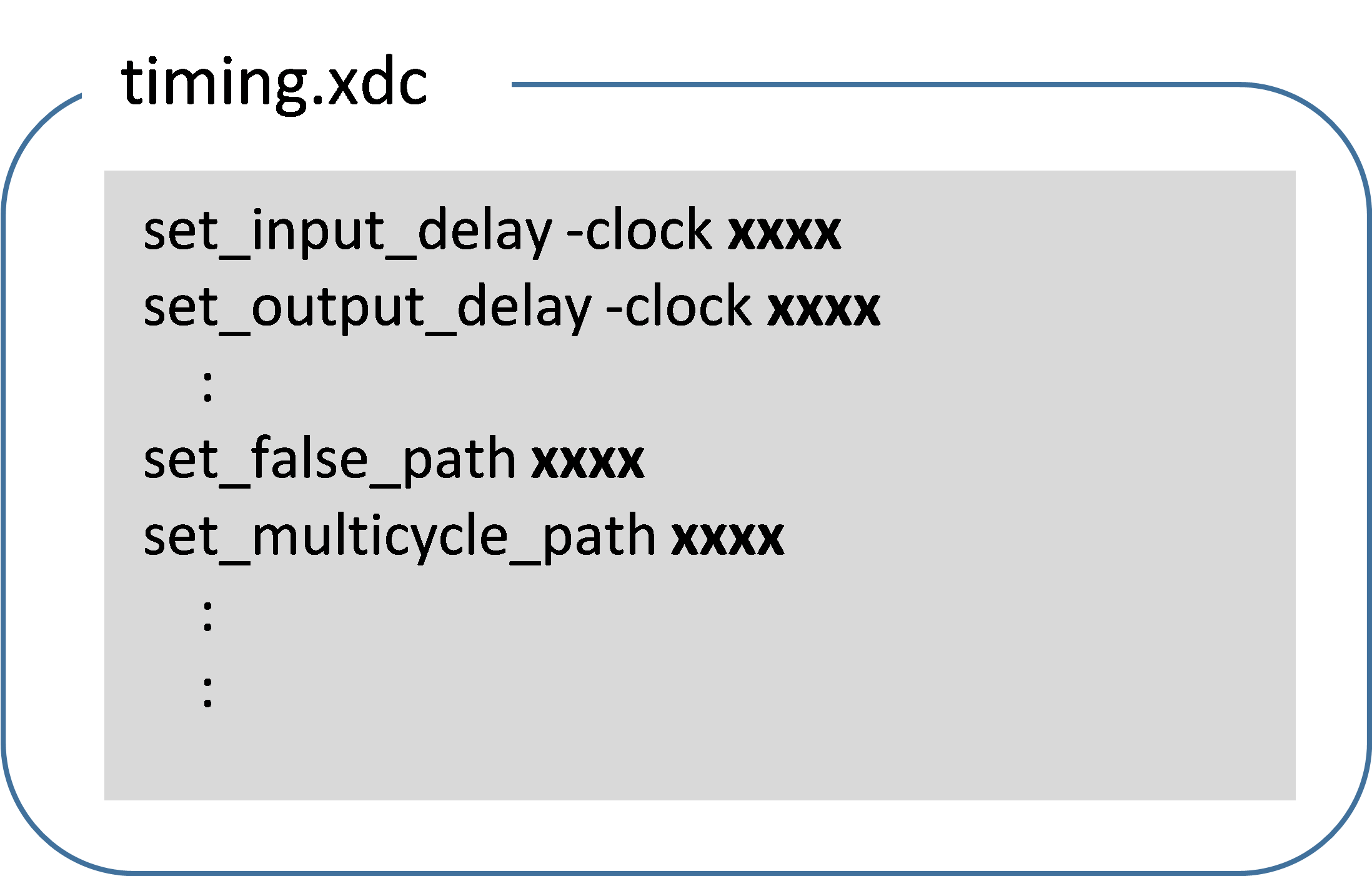

例えば多ピンのFPGAの場合、1つのXDCファイルにすると、行数が多くなり、変更(修正)が大変になります。PIN制約、クロック制約、タイミング制約などに分けてXDCを作成することで、見やすさや管理しやすくなると思います。

(例)以下にpin.xdc、clock.xdc、timing.xdcに

分けた場合のイメージ

IPコアを含んだ環境でのXDCファイルの優先度

生成した各IPコアフォルダの中にXDCファイルが存在しています。

そのため、IPコアのXDCファイル、ユーザーで作成したXDCファイルの読み込まれる順序があります。

まず、最初にIPコアのXDCファイルが読み込まれ、次にユーザーで作成したXDCファイルが読み込まれます。

注意として、ユーザーで作成したXDCファイルが後に読み込まれるため、IPコアの制約を上書きできてしまいます。

XDCの記述では、以下の内容は省略できます。

外部インタフェースに関係するIPコアを生成した場合

- IPコア生成時に自動生成されて、ツールが勝手に参照しに行くためです。

外部インタフェースとは、DDR3/4メモリ、ZYNQでは、MIOなどになります。

差動信号の場合

- ・信号のバス幅の違い

・信号名が不一致

・対象のモジュールの階層が違っている

XDCファイルで発生するワーニング

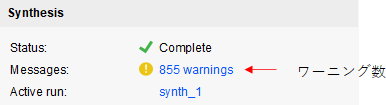

Vivado® ML Edition でコンパイル実行すると、XDC関連のワーニング、クリティカルワーニングが表示される場合があります。

XDCファイルの記述内容とデザイン内容に差分があり、無効な制約に関して表示されます。

- ・信号のバス幅の違い

・信号名が不一致

・対象のモジュールの階層が違っている

など、他の要因もありますが1例となります。

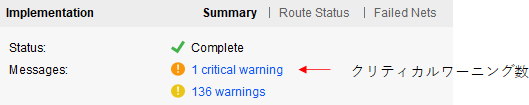

(例)Vivado® ML Editionで

Synthesis結果のレポート抜粋

(例)Vivado® ML Editionで

Implementation結果のレポート抜粋

ワーニング

多数出る場合がありますがメッセージの確認を行い、処置する/しないをユーザーで判断する必要があります。

制約の有効性を確認するために、何度もコンパイルを実行する場合があります。

クリティカルワーニング

動作不具合の原因になりますので、すべてのメッセージを確認し処置することをお勧めします。

コンパイルに使用しているRTLソースファイルの機能追加もしくは修正した場合でもXDCファイルに反映することを忘れていたために、ワーニング、クリティカルワーニングが発生する場合がありますので注意ください。

本件に関しては、いろいろな場合がありますので、別の機会にでも記載できたらと思います。

おわりに

以下のような場合には、XDCファイルの再確認、見直しを行うことをおすすめします。

不具合の発生原因のヒントにつながるかもしれません。

- ・XDCファイルに制約を記述しているが、デザインに反映されていない

・XDCファイルの制約が抜けているために、実機動作で不安定な現象が発生する

→実行動作の不具合の原因となり、解析に時間を要してしまう

このブログは「FPGA設計ブログ一覧」の

4. インプリメント(配置配線)のひとつです。

最後までご覧いただきありがとうございました。

今回説明した内容でのご不明な点や、FPGA設計などでお困りのことなどがありましたら、下記よりお問い合わせください。

弊社ではFPGA設計や回路図設計、レイアウト設計、ソフトウェア設計、筐体設計などを受託開発しています。サービス内容をWEBサイトに掲載していますので、ぜひご覧ください。