【Vivado®で使用するXDCファイルの基本的な記述例】第2回 コンフィグレーション設定、タイミング設定編

このブログでは、Vivado® ML EditionsおよびVivado® design Suite(以下「Vivado」といいます)で使用する、「XDCファイル」の基本的な記述について解説します。

XDCとは、Xilinx Design Constraint(頭文字)の略です。

XDCファイルとは、Xilinx社のFPGA及び適応型SoCに対して制約を与えることができるファイルで、以下の項目の制約設定が可能です。

- ・端子配置設定

- ・クロック設定

- ・コンフィグレーション設定

- ・タイミング設定 など

前回は、端子配置設定の中の「端子配置設定」、「クロック設定」についてお話しました。

前回のブログは コチラ をご覧ください。

第2回では、「コンフィグレーション設定の方法」と「タイミング設定」を説明します。

このブログは「FPGA設計ブログ一覧」の

4. インプリメント(配置配線)のひとつです。

目次

コンフィグレーション設定

CCLKの公称周波数の設定をします。(推奨:33)

set_property BITSTREAM.CONFIG.CONFIGRATE 33 [current_design]SPIフラッシュのSPIのバス幅の設定をします。(推奨:4)

set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 4 [current_design]以下の設定を行わなかった場合は、周波数3MHz、SPIビット幅1bitとなり、FPGAの起動に時間がかかってしまいます。※最大周波数→66MHz

set_property BITSTREAM.CONFIG.CONFIGRATE 33 [current_design]

set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 4 [current_design]以下は、Bank0のVCCIO電圧の設定です。

VCCIO=1.8Vの場合、CFGBVS→GND

VCCIO=2.5V or 3.3Vの場合、CFGBVS→VCCO の設定とします。

本記述は、なしでも動作します。

set_property CONFIG_VOLTAGE <1.8 2.5 3.3> [current_design]

set_property CFGBVS <GND / VCCO> [current_design]MIGなど、IPを生成した場合、XDCは自動生成されているため、記述する必要はありません。

タイミング設定

入力遅延

入力ポートでのデータ遅延時間を設定

set_input_delay -clock {クロック} -max 最大遅延 [get_ports 信号名]

set_input_delay -clock {クロック} -min 最小遅延 [get_ports 信号名]| クロック | 基準となるクロック |

| 最大遅延 | クロックエッジ後にデータが到達する最大時間→Setupの制約 |

| 最小遅延 | クロックエッジ後にデータが到達する最小時間→Holdの制約 |

| 信号名 | 対象となる信号名 |

出力遅延

出力ポートでのデータ遅延時間を設定

set_output_delay -clock {クロック} -max 最大遅延 [get_ports 信号名]

set_output_delay -clock {クロック} -min 最小遅延 [get_ports 信号名]| クロック | 基準となるクロック |

| 最大遅延 | クロックエッジ後にデータが必要とする最大時間→Setupの制約 |

| 最小遅延 | クロックエッジ後にデータが必要とする最小時間→Holdの制約 |

| 信号名 | 対象となる信号名 |

タイミング解析の除外

非同期入力をタイミング解析から除外するための設定

set_false_path [-from <node_list>] [-to <node_list>] [-through <node_list>]| -from | 始点のノー ド リ ス トを指定 |

| -to | 終点のノー ド リ ス トを指定 |

| -through | ”pin”、”port”、または”net”のノー ド リ ス ト を指定 |

例1) resetポートからすべてのレジスタへのタイミング解析の除外

set_false_path -from [get_port reset] -to [all_registers]例2) 2つの非同期クロックドメイン間(CLKAからCLKB)のタイ ミング解析の除外

set_false_path -from [get_clocks CLKA] -to [get_clocks CLKB]

set_false_path -from [get_clocks CLKB] -to [get_clocks CLKA]タイミング例外には、 set_false_path 以外に下記のコマンドがあります。

| コマンド | 機能 |

|---|---|

| set_multicycle_path | パスの開始点から終点までデータを伝搬させるのに必要なクロックサイクル数を指定します。 |

| set_max_delay set_min_delay |

最小パス遅延または最大パス遅延の値を指定します。 このコマンドを使用すると、デフォルトのセットアップおよびホールド制約ではなく、ユーザーが指定した最大/最小遅延値が使用されます。 |

マルチサイクルパス

- 同一クロック間で定義されるマルチサイクル

- 低速クロックから高速クロックへ定義されるマルチサイクル

- 高速クロックから低速クロックへ定義されるマルチサイクル

について記載します。

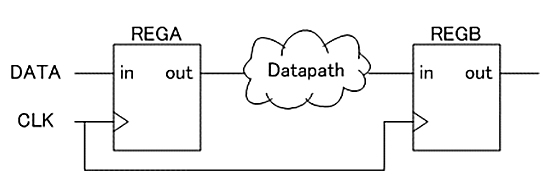

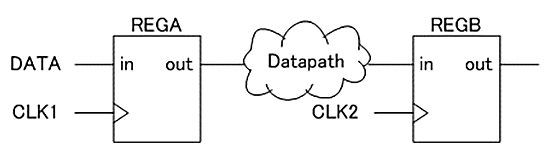

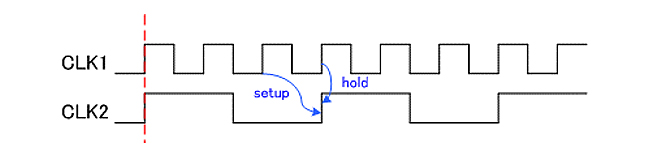

同一クロック間で定義されるマルチサイクル

デフォルトのセットアップ/ホールドの関係を示します。

以下にコマンド例を示します。

set_multicycle_path n -setup -from [get_pins REGA/C] -to [get_pins REGB/D]

set_multicycle_path n-1 -hold -from [get_pins REGA/C] -to [get_pins REGB/D]

・セットアップの乗数を”2”に設定した場合

set_multicycle_path 2 -setup -from [get_pins REGA/C] -to [get_pins REGB/D]

set_multicycle_path 1 -hold -from [get_pins REGA/C] -to [get_pins REGB/D]となります。

・セットアップの乗数を”4”に設定した場合

set_multicycle_path 4 -setup -from [get_pins REGA/C] -to [get_pins REGB/D]

set_multicycle_path 3 -hold -from [get_pins REGA/C] -to [get_pins REGB/D]となります。

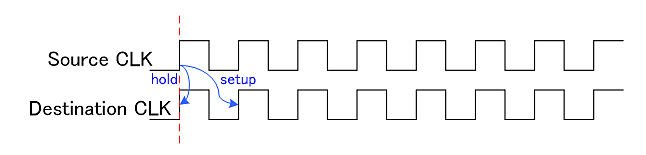

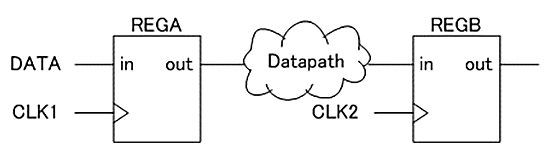

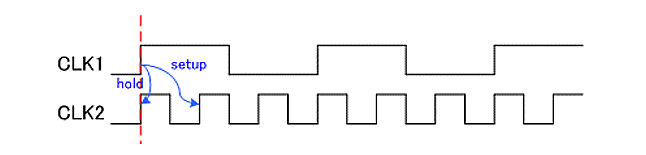

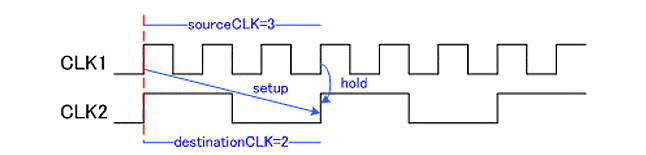

低速クロックから高速クロックへのマルチサイクル

・CLK2は、CLK1の3倍の周波数とした場合

デフォルトのセットアップ/ホールドの関係を示します。

set_multicycle_path n -setup -from [get_clocks CLK1] -to [get_clocks CLK2]

set_multicycle_path n-1 -hold -end -from [get_clocks CLK1] -to [get_clocks CLK2]

セットアップの乗数”n”に設定した場合、ホールドの乗数”n-1”をデスティネーションクロックに対して設定します。

・セットアップの乗数を”3”に設定した場合

set_multicycle_path 3 -setup -from [get_clocks CLK1] -to [get_clocks CLK2]

set_multicycle_path 2 -hold -end -from [get_clocks CLK1] -to [get_clocks CLK2] となります。

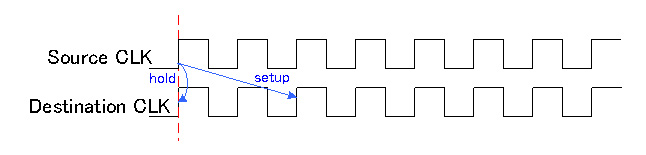

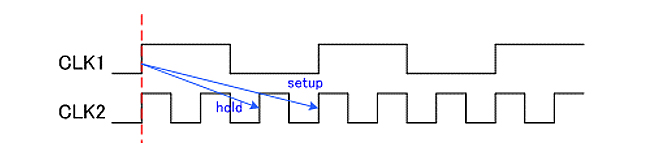

高速クロックから低速クロックへのマルチサイクル

・CLK2は、CLK1の1/3の周波数とした場合

デフォルトのセットアップ/ホールドの関係を示します。

set_multicycle_path n -setup -start -from [get_clocks CLK1] -to [get_clocks CLK2]

set_multicycle_path n-1 -hold -from [get_clocks CLK1] -to [get_clocks CLK2]

セットアップの乗数”n”をソースクロックに対して設定し、ホールドの乗数”n-1” に設定します。

・セットアップの乗数を”3”に設定した場合

set_multicycle_path 3 -setup -start -from [get_clocks CLK1] -to [get_clocks CLK2]

set_multicycle_path 2 -hold -from [get_clocks CLK1] -to [get_clocks CLK2]となります。

最大/最小遅延

- 最大遅延:セットアップを変更する場合に使用します。

- 最小遅延:ホールドを変更する場合に使用します。

・最大遅延コマンド例

set_max_delay <delay> [-datapath_only] [-from<node_list> ]

[-to <node_list>] [-through <node_list>]・最小遅延コマンド例

set_min_delay <delay> [-from <node_list>]

[-to <node_list>] [-through <node_list>]

・オプション

| -datapath_only | →スラックの算出からクロックスキューを除外できる →set_max_delayのみサポート →ホールドは無視される |

| -from | →クロック、入力または入出力ポート |

| -to | →クロック、出力または入出力ポート |

| -through | →ピン、ポート 、またはネット |

入力または出力ロジックの制約

set_max_delay/set_min_delayコマンドは、入力または出力ロジックの制約に使用されません。

入力ポートと初段のロジック間は、set_input_delayコマンドを使用します。

終段のロジックと出力ポート間は、set_output_delayコマンドを使用します。

入力/出力ポートの間の組合せパス(in-to-out)ではset_max_delay/set_min_delayコマンドを使用します。

ここまでが基本的なタイミング設定になります。

XDCファイルは、VivadoのconstraintからGUI上で設定する場合、もしくはテキストファイルに直接記載することが可能です。

拡張子は、xdcとなります。

以上となります。

次回は、バススキュー制約、優先順位、物理的制約について解説します。

このブログは「FPGA設計ブログ一覧」の

4. インプリメント(配置配線)のひとつです。

最後までご覧いただきましてありがとうございました!

今回説明した内容でのご不明な点や、FPGA設計などでお困りのことなどがありましたら、下記よりお問い合わせください。